仕様の説明:NIマルチファンクションI/O(MIO)DAQ

概要

内容

概要

このガイドは、ほとんどのNI仕様書と同じセクションに分かれています。以下の用語と定義はアルファベット順に記載されており、仕様書では異なる順序で記載されている場合があります。 このガイドは、60xx、61xx、62xx、63xx、64xx MIO DAQデバイスおよびモジュールにのみ適用されます。それ以外のNI製品ファミリ (cDAQおよびcRIOシャーシおよびコントローラ、91xx、92xx、94xx Cシリーズモジュール、マルチファンクションRIO 78xx Rシリーズ、デジタルマルチメータ、スコープ/デジタイザ、およびその他の計測器) では、仕様を取得する際に異なる用語や方法を使用している場合があります。したがって、MIO DAQファミリ以外のデバイスおよびモジュールでは、このガイドをリファレンスとして使用しないでください。

このガイドでは、全体を通してNI 6361およびNI 6363デバイスを基準として使用します。これらのデバイスの仕様を確認したい場合は、NI 6361およびNI 6363の仕様のリンクをクリックしてください。

仕様の用語について

さまざまな仕様間でカテゴリの違いがあることに注意してください。NIでは、テストおよび測定用計測器の機能および性能を「仕様」、「標準仕様」、および「特性」または「補足仕様」として定義しています。どの仕様が保証仕様または標準仕様であるかの詳細については、お使いのデバイスの仕様書を参照してください。

- 「仕様」は推奨キャリブレーション間隔内において、記載された動作条件下で保証される計測器の性能を示します。

- 「標準仕様」は推奨キャリブレーション間隔内において、記載された動作条件下で大多数の計測器が満たす仕様を示します。標準仕様は保証されている値ではありません。

- 「特性」または「補足仕様」は、設計または開発中に特定された計測器の基本的機能および属性を示し、検証または調整中に評価されたものではありません。これには、前述の定義に含まれていない、計測器の標準的な使用に関する情報が記載されています。

アナログサブシステムの仕様

NI MIO DAQデバイスおよびモジュールには、アナログ入力、アナログ出力、またはこれら両方のシステムが混在している場合があります。サブシステムごとに固有の仕様もありますが、両方に適用される仕様もあります。このセクションは、一般的な仕様、アナログ入力固有、およびアナログ出力固有を対象とする3つのセクションで構成されています。

アナログ入力およびアナログ出力

Absolute Accuracy at Full Scale(フルスケールでの絶対確度)

確度とは、測定値の正しい値にどれだけ近いかを指します。フルスケールでの絶対確度とは、測定対象の値が指定した範囲でサポートされる最大電圧であると仮定して計算される理論上の確度のことです。測定の確度は測定の変化に応じて変わるため、デバイス間の比較が行えるように、フルスケールの確度が使用されます。フルスケールでの絶対確度では、動作温度を25℃とするなど、実際には異なる可能性がある環境変数に関して仮定を行うことに注意してください。

- 公称レンジの正のフルスケール—特定の範囲で測定できる理想的な最大の正の値。

- 公称レンジの負のフルスケール—特定の範囲で測定できる理想的な最大の負の値。

- 残差ゲイン誤差—計装用アンプに固有のゲイン誤差。セルフキャリブレーション後に存在することが知られています。

- ゲイン温度係数—温度が最後のセルフキャリブレーション時の温度と比較してアンプのゲインにどのように影響するかを表す温度係数。

- 残差オフセット誤差—計装用アンプに固有のオフセット誤差。セルフキャリブレーション後に存在することが知られています。

- 基準温度係数—特定の温度での測定が、最後の外部キャリブレーション時の温度と比較してどの程度正確かを表す温度係数。

- INL誤差(相対確度分解能)—ADCの電圧出力から理想的な出力までの最大偏差。最悪の場合のDNLと考えることができます。関連トピック:DNL

- オフセット温度係数—温度が最後のセルフキャリブレーション時の温度と比較してADC変換のオフセットにどのように影響するかを表す温度係数。

- ランダム/システムノイズ—アナログフロントエンドによって別に生成されるシステムノイズ。入力チャンネルを接地して測定します。

サンプル

NI PXIe-6363のレンジは±0.5 Vです。フルスケールでの絶対確度は、測定対象の信号が0.5 Vであると仮定して計算されます。±0.5 Vレンジのフルスケールでの絶対確度は100 µVです。

関連トピック

Analog-to-Digital Converter(ADC)Resolution(A/D変換器(ADC)分解能)

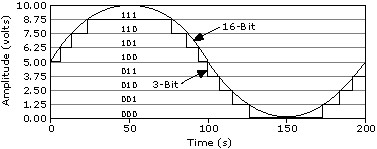

分解能は、デバイスまたはセンサが検出できる入力信号の変化の最小単位です。アナログ信号を表すのに使用されるビット数によってADCの分解能が決定します。

サンプル

NI PXIe-6363は16ビットデバイスです。つまり、±5 Vレンジで検出できる最小の振幅変化は0.152 mVです。±0.1 Vレンジでは、この値は3.05 µVです。

Common Mode Rejection Ratio (CMRR) (コモンモード除去比 (CMRR))

アンプの正と負の入力で同じ信号が観測される場合、CMRRは、この信号のうちどの程度が最終出力から拒否されるかを指定します(通常はdBで測定)。理想的なアンプではコモンモード信号の100%が除去されますが、これは実装では達成できません。

サンプル

NI PXIe-6363のCMRRは100 dBです。つまり、コモンモード電圧が100,000倍まで減衰します。測定される信号が5 Vpkの正弦波で、正と負の入力間のオフセットまたは共通電圧が5 VDCである場合、最終出力では5 VDC入力が5 µVまで拒否または減衰されます。CMRRは確度の導出の際は含まれません。測定される信号にコモンモード電圧が含まれている場合は、別途考慮してください。

Convert Interval(変換インターバル)

マルチチャンネル測定でチャンネル間に必要な整定時間。

サンプル

PCI-6221では、ユーザが必要とする確度のレベルに応じて、4~7マイクロ秒の変換インターバルが生じます。

関連トピック

Coupling(カプリング)

2つの回路からなるインタフェースのプロパティで、インタフェースの一方からもう一方に渡される信号のタイプを定義します。通常は2つのオプションがあります。

- DCカプリング: AC信号とDC信号の両方を通過させます。

- ACカプリング: AC信号のみを通過させます。結果として、信号のDCオフセットの除去をハードウェアで実装します。

ソフトウェアで選択可能なカプリングを備えているデバイスもあれば、ACまたはDCのいずれかを備えているデバイスもあります。

サンプル

NI PXIe-6363は、アナログ入力とアナログ出力の両方でDCカプリングを備えています。ACカプリングはどちらもサポートしていません。

関連トピック

Crosstalk(クロストーク)

あるチャンネルの信号が隣接するチャンネルにどの程度結合される、つまり影響を与える可能性があるかを示す測定量を指します。クロストークは、あるワイヤまたはPCBトレースに振幅が変化する信号が存在し、そのワイヤまたはPCBトレースが物理的に近い別のワイヤまたはPCBトレースに存在する場合に、常に存在します。

サンプル

NI PXIe-6363のクロストークの仕様は、隣接チャンネルで-75 dB、非隣接チャンネルで-95 dBです。たとえば、チャンネルai2のクロストーク仕様は、チャンネルai1とai3の間で-75 dBとなり、他のすべてのaiチャンネルについては-95 dBとなります。

データ転送メカニズム

NIデバイスでは、デバイスからコンピュータへ(入力の場合)、およびコンピュータからデバイスへ(出力の場合)、双方向にデータが転送されます。バス(USB、PXI Expressなど)に応じて、さまざまなデータ転送メカニズムが使用されます。バスによっては複数の転送メカニズムに対応できます。具体的なメカニズムの詳細については、NI-DAQmxのヘルプドキュメントを参照してください。

サンプル

USB-6341は、USBバルクデータ転送(信号ストリーム)とプログラムI/Oデータ転送に対応しています。NI PXIe-6363は、ダイレクトメモリアクセス(DMA)とプログラムI/Oに対応しています。

関連トピック

Differential Non-Linearity (DNL)(微分非直線性(DNL))

DACの理想的なステップサイズ(ステップサイズの計算方法については「デジタル-アナログ変換器(DAC)分解能」を参照)と、出力される実際の値(通常はLSBで測定)との差を指します。理想的なDACでは、DNLは0 LSBになります。

サンプル

NI PXIe-6363のDNLは±1 LSBです。つまり、DACから出力される値の場合、実際の値はプログラムされた値から±1 LSB離れている可能性があります。たとえば、ユーザが±5 Vの範囲で1 Vの値を出力するようにDACをプログラムした場合、出力 (確度の影響を除く) は次の範囲になります。

INLはDNLの複合作用であるため、INLの仕様は確度計算でよく使用されます。NI PXIe-6363の場合、確度表のINL仕様は使用範囲の64 ppm、つまり4 LSBです。

Digital-to-Analog Converter(DAC)Resolution(デジタル-アナログ変換器(DAC)分解能)

デジタル値から変換するときのアナログ信号を表すビット数を指します。

サンプル

NI PXIe-6363では16ビットDACを使用します。つまり、216とおりの離散値があり、±5 V、±10 V、またはユーザによる供給電圧のいずれかで出力できます。

関連トピック

FIFO Size (Analog) (FIFOサイズ (アナログ))

NI DAQデバイスは、アナログ入力またはアナログ出力のタスクを実行するときに、データをオンボードFIFOに保存できます。

- 入力タスクの場合、このFIFOを使用してデータをバッファリングした後、NI-DAQmxドライバソフトウェアがそのデータをPCバッファと呼ばれるRAM内の事前に割り当てられた場所に転送します。

- 出力タスクの場合、ユーザが生成を要求したデータを、FIFOとPCバッファの組み合わせでバッファリングできます。

入力チャンネルと出力チャンネルを持つデバイスには、サブシステムごとに専用のFIFOがあります。ただし、FIFOはそのFIFO内のすべてのチャンネルで共有されます。アナログ入力の場合、NI-DAQmxが実装しているデータ転送メカニズムにより、FIFOに格納されたデータはオンボードFIFOがオーバーランしない速度でPCバッファに転送されます。アナログ出力の場合、NI-DAQmxが実装しているデータ転送メカニズムにより、PCバッファ内のデータはFIFOがアンダーランしない速度でオンボードFIFOバッファに転送されます。アナログ出力の場合、ユーザが選択可能なプロパティがあり、PCバッファを使用するかどうかを指定でき、オンボードFIFOのみから単一の波形を再生成できます。

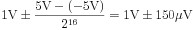

サンプル

NI PXIe-6363には、2,047サンプルの入力FIFOがあります。たとえば、データを1,024サンプル/チャンネル/秒のレートで集録する4つのチャンネルを持つ入力タスクでは、0.5秒未満でオンボードFIFOがオーバーランします。

オーバーランを回避するため、NI-DAQmxはDMAを使用してFIFOからオンボードのコンピュータメモリ (バッファ) にデータを転送します。

関連トピック

Input Bias Current(入力バイアス電流)

入力インピーダンスが有限であることの結果として、デバイスで信号を検出するためには少量の電流が必要になります。理論上はこの値は0 Aでなければなりませんが、実際にはこれは不可能です。

サンプル

NI PXIe-6363の入力バイアス電流は±100 pAです。つまり、NI PXIe-6363で測定対象となるセンサはすべて、正しくデジタル化できるように、電圧出力レンジ全体にわたって少なくともこの電流を供給する必要があります。

Input Current During Overvoltage Condition(過電圧状態での入力電流)

デバイスが過電圧状態の場合に、デバイスがシンクする指定の電流量です。

サンプル

NI PXIe-6363は、過電圧状態でピンあたり最大±20 mAをシンクします。この値を超えると、重要な部品が損傷する可能性があります。

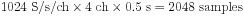

Input Impedance(入力インピーダンス)

入力インピーダンスは、入力回路がアナログ入力グランドへの電流の流れをどれだけ妨げるかを示す尺度です。理想的なADCの場合、この値は無限でなければなりません(つまり、入力からグランドに電流が流れない)。しかし、実際にはこれは不可能です。入力インピーダンスが有限であることから、回路(特に出力インピーダンスが高い回路)に対して、ADCからある程度の負荷がかかります。センサの出力インピーダンスは低いのが一般的です。

サンプル

NI PXIe-6363の入力インピーダンスはZin > 10 GΩです。最も低い入力インピーダンスにおける最悪のシナリオでは、出力インピーダンスZout = 150Ωのセンサを想定した場合、回路の一方がグランドとなっている測定を次の簡略化された回路と見なすことができます。

センサ出力とDAQデバイス入力を直列接続することで、電圧が2つのインピーダンス値の間で分配され、電圧のほとんどが大きい方のインピーダンスにかかります。たとえば、このセンサの感度が20℃/Vで、100℃ (5 Vを出力)を測定しようとする場合、DAQデバイスで測定される電圧は、出力電圧に (入力インピーダンス)/(DAQ入力インピーダンスとセンサ出力インピーダンスの和) を掛けたものになります。

この75 nVの測定差はインピーダンスに起因する5℃の測定誤差に相当しますが、ほぼ無視できます。

入力インピーダンスの仕様が重要になる例を説明するため、センサが5 GΩなどの非常に高い出力インピーダンスを持っている場合を考えます。こうした非常に高い出力インピーダンスを持つセンサにDAQデバイスを接続すると、センサからの5 Vの公称出力が3.33 Vとして読み取られ、33.4℃の仮定の測定誤差が生じます。

Maximum Update Rate(最大アップデートレート)

アナログ出力の場合、アップデートレートは、DACからアナログ電圧または電流値への毎秒サンプル数を示します。ほとんどのNIデバイスは、アナログ出力チャンネルあたりDACを1つ備えていますが、アナログ出力データを格納するFIFOはすべて共有します。このFIFOからデータを読み取ってボード上の別のDACに転送できるレートが原因で、場合によっては、同じデバイスで複数のAOチャンネルを使用している場合にアップデートレートが制限されることがあります。アップデートレートは、単一のチャンネルから出力する場合は毎秒サンプル数(サンプル/秒)で測定され、複数のチャンネルから出力する場合はチャンネルあたりの毎秒サンプル数(サンプル/秒/チャンネル)で測定されます。

アナログ入力の場合については、「サンプルレート」を参照してください。

サンプル

NI PXIe-6363は4つのアナログ出力チャンネルを備えています。

- 単一のチャンネルを使用する場合、そのチャンネルのアップデートレートは2.86メガサンプル/秒です。

- アナログ出力の3つのチャンネルを使用する場合、最大アップデートレートは1.54 MS/秒/チャンネルです。FIFOからデータを読み取って各種DACに送信できるレートにより、スキャンリストに追加されるチャンネルが増えるにつれて、アップデートレートが徐々に制限されます。

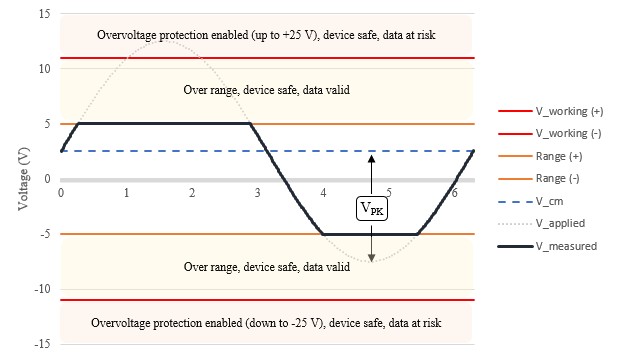

Maximum Working Voltage (最大動作電圧)

最大動作電圧は、デバイスが任意のアナログ入力チャンネルで許容できる合計の電圧レベルを示します。この電圧を超えると他のチャンネルでのデータの有効性が問題になります。他のチャンネルでの確度を保証するため、測定する信号と、AI GNDを基準とするコモンモード電圧との組み合わせが、この最大動作電圧の仕様を超えてはなりません。 最大動作電圧はデバイスの入力レンジに依存はしません。

サンプル

以下では、コモンモードが2.5 VDCである10 Vpkの正弦波を、最大動作電圧が±11 VのPXIe-6363で測定しています。

2つの信号の組み合わせは+12.5 Vでピークに達し、ここで最大動作電圧を超えます。最大動作電圧を超えると、他のマルチプレクスチャンネルでデータの有効性が危険にさらされます。これは、マルチプレクサの過剰な電荷が安定するまでの十分な時間がないためです。

関連トピック

Monotonicity(単調性)

単調性は、DAC符号が増加すると出力電圧も増加することを保証するものです。

サンプル

NI PXIe-6363では、DAC符号が増加するにつれて出力電圧が増加することが保証されます。たとえば、ランプ関数は傾斜の方向に応じて常に増加または減少します。

Output Current Drive(出力電流駆動)

アナログ出力の場合、出力電流駆動は、デバイスがシンク(吸収)またはソース(供給)できる電流の最大量です。接続される負荷(出力インピーダンスを含む、プログラムされた電圧と組み合わされる)によって、プログラムされた出力電圧の維持に必要な電流が決まります。

電流駆動が指定した出力電流駆動を下回ったままであれば、プログラムされた出力電圧が保証されます。出力電流駆動を超えるとデバイスはオーバードライブ状態になり、出力電圧は保証されなくなります。

サンプル

NI PXIe-6363は、任意のアナログ出力チャンネルから±5 mAを駆動できます。±10 Vのレンジの場合は、フルスケールで駆動できる最小の合計インピーダンスが、最大の電力出力、つまり最大の電流と電圧から決定されることになります。

PXIe-6363の出力インピーダンスを考慮すると、フルスケールで駆動できる最小の接続インピーダンスは、最小負荷と出力インピーダンスの差になります。

関連トピック

Output Impedance(出力インピーダンス)

出力インピーダンスとは、以下に示すように、アナログ出力チャンネルと実質的に直列につながったインピーダンスのことです。

出力インピーダンスが低いと、生成される電圧のうちアナログ出力の負荷全体で降下する量が増えます。必要な電圧レベルが確実に達成されるように、出力インピーダンスを考慮することが重要です。

サンプル

NI PXIe-6363の出力インピーダンスは0.2Ωです。たとえば、接続されている負荷のインピーダンスが500Ωで、ユーザが指定した電圧が1 Vの場合、負荷にかかる実際の電圧は0.9996 V、つまり0.4 mVとなり、想定よりも低くなります。この電圧では、デバイスからも1.99 mAの電流が流れます。

Overdrive(Short Circuit)Current(オーバードライブ(短絡回路)電流)

出力と負荷インピーダンスの組み合わせが低すぎて、 出力電流駆動での指定よりも多くの電流がデバイスから流れる場合、デバイスはオーバードライブ状態になります。オーバードライブ(または短絡)電流は、デバイスが破損せずに供給できる電流の最大量です。オーバードライブ状態では、電流が増加するにつれて電圧が降下します。

オーバードライブ電流を超えるとデバイスが破損する恐れがあります。デバイスの破損を防ぐため、常に出力電流駆動の仕様の範囲内でデバイスを使用することをお勧めします。

サンプル

NI 6363のオーバードライブ電流の仕様は26 mAです。短絡時などにこの値を超えると、デバイスが破損する恐れがあります。

関連トピック

Overdrive Protection(オーバードライブ保護)

アナログ出力の場合、オーバードライブ保護は、チャンネルで許容できる最大電圧であり、この電圧を超えるとデバイスの破損が生じます。偶発的な逆駆動電圧の場合に備えて、この仕様はプログラムできる実際の電圧よりも高くなっています。

サンプル

NI PXIe-6363は、各アナログ出力チャンネルで個別に最大±25 Vまで保護されます。このため、出力としてプログラムされた電圧に関係なく、AO GNDを基準にしたピンの電圧が±25 V以内である限り、デバイスの破損は生じません。この値を超えるとデバイスが破損する恐れがあります。

過電圧保護

アナログ入力回路には保護ダイオードが組み込まれており、PGIAやADCなどのデバイスで最も重要なコンポーネントが損傷しないように、大きな電圧が遮断されます。

- デバイスの電源がオンのときは、これらのダイオードの電圧はある程度まで正と負の方向にバイアスします。そのため、バイアス電圧と逆電圧の合計よりも大きい電圧が存在しない限り、これらのダイオードが過負荷になって破損することはありません。

- デバイスの電源がオフのときは、バイアス電圧がなくなるため、ダイオードの反転に必要な電圧が低くなり、デバイスが破損しやすくなります。

過電圧状態では、デバイスがシンクできる最大電流量は過電圧状態での入力電流によって指定されます。

サンプル

NI PXIe-6363は、2つのAIピンに対して最大±25 Vまで保護されます。3つ以上のAIピンで±25 Vを超える過電圧が生じた場合、デバイスが破損する恐れがあります。デバイスがオフの間、保護レベルは±15 Vまで低下します。

Power-on State(電源投入時の状態)

電源投入時の状態は、デバイスの電源がオンになり、 電源投入/切断時のグリッチと呼ばれるグリッチ時間が経過した後の、アナログ出力チャンネルの値を示します。デバイスがバスから電力を受け取る前の出力の値は、電源投入時のグリッチの仕様に記載されています。

サンプル

NI PXIe-6363は、電源投入時にアナログ出力チャンネルで±5 mVになります。

Power-on/off Glitch(電源投入/切断時のグリッチ)

デバイスに電力を供給したり、電力を除去したりすると、アナログ出力チャンネルでグリッチ信号が発生します。

- グリッチエネルギー振幅—グリッチ信号がグリッチ時間中に到達するピーク振幅

- グリッチエネルギー持続時間—グリッチ信号が電源投入状態の範囲内に弱まるまでの時間

サンプル

NI PXIe-6363の指定されたグリッチは1.5 Vpk(200ミリ秒間)です。NI USB-6363の仕様グリッチは1.5 Vpk(1.2秒間)です。ファームウェアアップデートやUSBホストの性能により、USBデバイスのグリッチ時間が指定よりも長くなることがあります。

Range(Input or Output)(レンジ(入力または出力))

アナログ入力の場合、保証された確度で測定できる正と負の最大値です。アナログ出力の場合、生成可能な正または負の最大値です。デバイスによっては、低レベルの信号でより高い解像度が得られるように、複数の入力レンジまたは出力レンジを使用できるものがあります。

サンプル

NI PXIe-6363には、±0.1 V、±0.2 V、±0.5 V、±1 V、±2 V、±5 V、±10 Vの7つの入力電圧レンジと、1つの出力レンジ±10 Vがあります。

関連トピック

Analog-to-Digital Converter(ADC)Resolution(A/D変換器(ADC)分解能)

Digital-to-Analog Converter(DAC)Resolution(デジタル-アナログ変換器(DAC)分解能)

サンプルレート

サンプルレートは、ADCがデータをアナログ値からデジタル値に変換する頻度を示します。ADCが1つしかなく、サンプルレートがチャンネル間で共有されるデバイスもあれば、チャンネルごとに専用のADCを持つデバイスもあります。サンプルレートは1秒あたりのサンプル数(サンプル/秒)で測定され、複数チャンネルから集録する場合はチャンネルごとの1秒あたりのサンプル数(サンプル/秒/チャンネル)で測定されます。

- 単一チャンネルの最大値—チャンネル間で共有されるサンプルレートの場合、1つのチャンネルにおいて、共有時に許容されるよりも高いレートでデータを集録できます。

- マルチチャンネルの最大値—チャンネル間でサンプルレートを共有するデバイスの場合、すべての結合されたチャンネルにおいてデータを集録できる最大レートです。

- 最小値—データを集録できる最小レートです。

アナログ出力の場合については、「最大アップデートレート」を参照してください。

サンプル

NI PXIe-6363はマルチプレクスデバイスです。つまり、アナログ入力チャンネルが単一のADCに多重化されます。1つのアナログ入力チャンネルで、毎秒最大200万サンプル(2 MS/秒)のアナログ信号をサンプリングできます。複数のチャンネルを使用する場合、すべてのチャンネルの合計レートは1 MS/秒未満でなければなりません(2つのチャンネルで500 kS/秒/チャンネルでサンプリング可能、4つのチャンネルで250 kS/秒/チャンネルでサンプリング可能など)。このデバイスでは最小サンプルレートはありません。

Scan List Memory(スキャンリストメモリ)

タスクでスキャンされるチャンネルの数は、スキャンリストメモリとして指定します。アナログ入力タスクでは、スキャンリストと呼ばれるシーケンスに多数の仮想チャンネルを含めることができます。スキャンリストには同じ物理チャンネルを何度も含めることができ、任意の順序でサンプリングできます。タスクがコミットされると、スキャンリストが一時的にDAQデバイスにプログラムされます。

サンプル

NI PXIe-6363には、4,095項目のスキャンリストメモリがあります。つまり、1回のスキャン(サンプルクロックの1ティック)で、すべての物理チャンネルが1つのタスクに含まれている場合、最大4,095個の物理チャンネルが読み取られます。ただし、マルチチャンネル計測器の整定時間(一部のデバイスでは変換インターバルとも呼ばれます)を考慮して、サンプルクロックレートは最大約250 Hzに制限されます。

Settling Time(整定時間)

アナログ出力値が一定の精度内に安定するのにかかる時間。

サンプル

NI PXIe-6363では、フルスケールステップの整定時間が1 LSBまたは2マイクロ秒の15 ppm以内に収まります。たとえば、±5 Vレンジでのフルスケール発振の場合(-5 V、5 V、-5 V、5 Vなど)、1 LSB以内に駆動できる最大周波数は1/(2マイクロ秒) = 500 kHzになります。

Settling Time for Multichannel Measurements(マルチチャンネル計測器の整定時間)

マルチチャンネル集録の実行時にADCを各チャンネルに接続しなければならない時間。

サンプル

±10 VのレンジでNI PXIe-6363のデータを集録する場合、フルスケールのステップ入力が供給された状態で、プログラマブルゲイン計装用アンプ(NI-PGIA)が実際の値の1最下位ビット(LSB)以内に整定するには、マルチプレクサが最大1.5マイクロ秒のあいだ単一のチャンネルに留まる必要があります。

Slew Rate(スルーレート)

スルーレートは、与えられたデバイスのアナログ出力チャンネルの変化率を示します。通常はV/マイクロ秒で測定されます。出力の整定時間は、すでに計算に含まれているスルー時間で計算されます。高振幅高周波信号用のシステムを設計する際はスルーレートを考慮することが重要です。これは、振幅内の大きな振れが対象のデバイスのスルーレートを超える可能性があるためです。

サンプル

NI PXIe-6363の標準的なスルーレートは20 V/マイクロ秒です。これは、生成可能なフルスケールの高周波が1 MHzであることを意味します。より振幅の大きいフルスケール信号を出力しようとすると、望ましくない歪みが生じます。

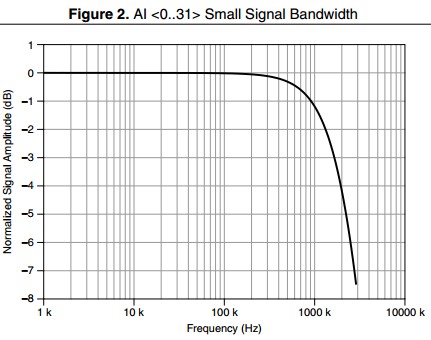

Small Signal Bandwidth(小信号帯域幅)

–3 dB未満の減衰で渡される周波数範囲を指します。小信号帯域幅のテストは、スルーレートによる歪みが要因とならないように低電圧信号で実行されます。

サンプル

NI PXIe-6363の小信号帯域幅は1.7 MHzで、次の特徴があります。

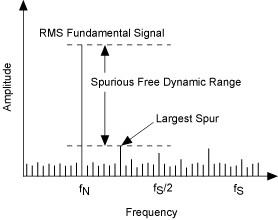

Spurious Free Dynamic Range(SFDR)(スプリアスフリーダイナミックレンジ(SFDR))

スプリアスフリーダイナミックレンジとは、スプリアスノイズによって基本信号が干渉を受けたり歪んだりする前の使用可能なダイナミックレンジのことです。アナログ入力回路とアナログ出力回路のどちらも非線形性があり、その結果として高調波歪みが発生します。SFDRは次のように周波数領域で簡単に観測できます。

サンプル

PCI-6133のSFDRは約95 dBです。前のグラフを例にとると、基本信号が0 dBで適用された場合、次に高いスプリアスは95 dB低い位置で発生し、スプリアス干渉のない使用可能なダイナミックレンジとなります。

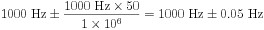

Timing Accuracy(タイミング確度)

NI DAQデバイスでタイミング信号用のクロック信号を生成する場合、生成される実際の周波数はタイミング確度の範囲内になります。この仕様は、オンボードの水晶発振器の全体的な確度に基づいています。通常、タイミング確度は100万分の1(ppm)で測定されます。この確度値をヘルツに変換するには、確度値を掛けて100万で割ります。クロックの周波数は、サイクルごとに大幅に変化することはほとんどありません。

サンプル

PXIe-6363のタイミング確度は50 ppmです。アップデートレートが1,000サンプル/秒のアナログ出力タスクの場合、サンプルクロックは1,000 Hz±50 ppmで動作します。ヘルツで表すと次のようになります。

Timing Resolution (タイミング分解能)

オンボードのタイミングエンジンを使用する場合、アナログ入力および出力タスクのサンプルおよびアップデートレートは離散値に制限されます。2つの隣接するレート間のクロック周期の違いを、タイミング分解能と呼びます。NI-DAQmxでは、ユーザが指定した正確な周波数を生成できない場合、選択した周波数は強制的に、次に使用可能な最大の周波数になります。

サンプル

NI PXIe-6363の指定のタイミング分解能は10ナノ秒です。つまり、データを10ナノ秒の整数倍で生成または集録できます。たとえば、32,000.00 Hzと32,010.2432... Hzは2つの隣接する周波数です。これは、クロック周期がそれぞれ31.250マイクロ秒、31.240マイクロ秒となるためです。次に使用可能な周波数を見つけるには、既知のクロック周期にタイミング分解能を加算または減算します。

Total Harmonic Distortion(THD)(全高調波歪み(THD))

ADCおよびDACの部品には固有の非線形性があるため、測定または生成される信号には高調波周波数が現れます。これらの高調波の電力の総和と基本波の電力との比率のことを、全高調波歪みと呼びます。

サンプル

PCI-6133の指定のTHDは約-101 dBです。つまり、特定のテスト信号(この場合はフルスケールで10 kHzの正弦波)の場合、高調波歪みに起因する信号の電力は0.001%未満になります。逆に、測定される電力の99.999%以上は、対象の基本トーンや信号に起因する可能性があります。

デジタルサブシステムの仕様

NI MIO DAQデバイスおよびモジュールには、デジタル入力、デジタル出力、またはこれら両システムの組み合わせに対応できるものがあります。これらはプログラム可能な機能的インタフェース(PFI)ラインにも対応します。PFIは、バックプレーンを介してデジタル信号をルーティングする手段となります。以下のリストでは、一般的な仕様とその定義、および、その仕様が実際の世界でどのように使用される場合があるかを示します。

DI Sample Clock frequency(DIサンプルクロック周波数)

デジタル波形データを集録できるレートを決定します。この仕様は、デバイスがUSBベースまたはPCIベースかどうか(PCI、PCI Express、PXI、PXI Expressを含む)によって異なります。通常は、PCIベースのデバイスの方が、バスの持続スループットが高く、レイテンシが低く、ダイレクトメモリアクセス(DMA)データ転送が実装されているため、使用できるデジタル波形転送レートが高くなります。

サンプル

NI 6363はUSB、PCI Express、PXI Expressの3つのフォームファクタで提供されます。

- USB - サンプルクロック周波数の範囲は、バス上の他のデバイスのアクティビティに応じて0~1 MHzになります。たとえば、デバイスと同じUSBハブ上のUSB外付けハードドライブにデータを記録している場合、1 MHzの完全な集録レートを達成できない可能性があります。最大限のパフォーマンスを得るため、USB DAQデバイスをUSBルートハブ上の唯一のデバイスにすることをお勧めします。

- PCI ExpressおよびPXI Express - サンプルクロック周波数の範囲は、バス上の他のデバイスのアクティビティに応じて0~10 MHzになります。たとえば、集録中に大量のデータが並列処理のためにGPUに送信されている場合、10 MHzの完全な集録レートを達成できない可能性があります。最大のパフォーマンスを得るため、PCI ExpressまたはPXI Expressデバイスが他のデバイスと同じスイッチ上にある場合は、すべてのデバイスから同じ方向にデータを送信することをお勧めします。

DO Sample Clock frequency(DOサンプルクロック周波数)

ほとんどのNIデバイスのポート0からデジタル波形データを出力できるレートを決定します。この仕様は、デバイスがUSBベースまたはPCIベースかどうか(PCI、PCI Express、PXI、PXI Expressを含む)、およびデータの発信元によって異なります。

- FIFOからの再生成 - ユーザがデバイスにデータを1回書き込み、データがデバイスのオンボードで再生成されます。この方法により、バストラフィックの問題が解消され、出力レートが向上します。

- メモリからのストリーミング - デバイスがデータを再生成しないため、アンダーフローエラーを避けるために、ユーザのアプリケーションから常に新しいデータを使用できる必要があります。この方法では、バス上で常に通信が行われるため、スループットが低いバスほどアップデートレートが制限されます。

サンプル

NI 6363はUSB、PCI Express、PXI Expressの3つのフォームファクタで提供されます。

- USB - PCI ExpressおよびPXI Expressと比較して、スループットが低く、バスのレイテンシが高くなります。FIFOから出力波形を再生する場合、最大10 MHzのアップデートレートを実現できます。メモリからストリーミングする場合、データはUSB経由でストリーミングする必要があるため、より遅い1 MHzの最大レートが指定されます。

- PCI ExpressおよびPXI Express - これらのバスの方が高速であり、高いスループットを維持でき、指定の最大10 MHzのアップデートレートを提供します。

Debounce Filter Settings(デバウンスフィルタ設定)

デジタルラインの状態が変化すると(LOWからHIGH、またはHIGHからLOW)、新しい状態に落ち着くまでに2つの状態の間でバウンスすることがあります。バウンスを無視し、安定した後の値のみを読み取るように、デバウンスフィルタを実装することができます。スタティックデジタル入力ライン(PFI/ポート1/ポート2)の場合、デジタルデバウンスフィルタを使用して、プッシュボタンなどの物理インタフェースから生じることが多いノイズまたはグリッチのある信号をデバウンスします。これらのフィルタは、デジタルラインフィルタとは異なり、フィルタ長に合わせてユーザがカスタマイズできます。

サンプル

PXIe-6363では、フィルタに対して90ナノ秒、5.12マイクロ秒、2.56ミリ秒、またはカスタムの間隔タイミングを使用できます。また、プログラム可能なHIGH/LOW遷移や、入力ラインごとの選択も可能です。これらのフィルタ時間は、PXIe-6363のオンボード発振器から取得されます。

Delta VT Hysteresis(VT+ - VT-)(デルタVTヒステリシス(VT+ - VT-))

ヒステリシスとは、値が増加しているか減少しているかによって遷移しきい値が異なるという特性のことです。この場合は、HIGHから不確定状態への遷移と、LOWから不確定状態への遷移が観測されます。正のしきい値と負のしきい値との差が、電圧しきい値のヒステリシスになります。この仕様は、電圧レベルが再び不確定状態に移るまでにどの程度しきい値を下回るか上回る可能性があるかを示します。

サンプル

NI PXIe-6363では少なくとも0.2 Vのヒステリシスを規定しています。これは、信号が0 Vから5 Vに遷移する場合、VT+値より最大で0.2 Vしか低下しなくても、論理レベルがLOWと見なされる可能性があることを意味します。この変動期間中に、値は不確定状態を通過します。

Digital Line Filter(デジタルラインフィルタ)

ポート0のいずれかのラインでラインフィルタが有効になっている場合、そのラインでは、論理レベルとして登録されるように、指定したフィルタ時間のあいだ安定した論理レベルを維持する必要があります。このツールは、長いケーブルやノイズの多い環境でデジタルデータを送信する場合に役立ちます。通常、ソフトウェアでは異なるフィルタ時間を選択でき、短、中、長のフィルタを使用できます。システムのノイズ特性に応じて、これらのフィルタ時間のいずれかがアプリケーションに適する場合があります。

サンプル

PXIe-6363には、160ナノ秒、10.24マイクロ秒、5.12ミリ秒の3つのデジタルラインフィルタ時間が組み込まれています。これらのフィルタはポート0のラインにのみ適用されます。ポート1、ポート2、PFIライン、またはPXI固有のラインにおけるフィルタリングオプションについては、「デバウンスフィルタ設定」を参照してください。

Direction Control(方向制御)

デジタルまたはPFIラインを入力または出力ラインとして構成できるかどうかを決定します。

サンプル

PXIe-6361では、各デジタルまたはPFIラインを入力または出力として構成できます。

Ground Reference(Digital)(グランド基準(デジタル))

デジタル信号を測定または生成する際の基準点を示します。たとえば、論理HIGHデジタル出力で、出力ピンと指定したグランド基準との間で5ボルトが測定される場合があります。

サンプル

PXIe-6361では、デジタルグランド(D GND)信号を、デジタル入力、デジタル出力、およびPFIライン信号のグランド基準として使用します。異なるレベルや周波数の信号の混合による干渉を避けるため、デジタルグランドはアナロググランドから分離されています。デジタルグランドもアナロググランドも、シャーシのグランドを基準にしています。USBデバイスの場合は特に注意が必要です。これは、アナロググランドもデジタルグランドも、USBケーブルのシールドを介してコンピュータのシャーシのグランドを基準にしているためです。

Input High Current / Input Low Current(IIH / IIL)(入力HIGH電流/入力LOW電流(IIH/IIL))

理想的には、デバイスの入力インピーダンスは無限であり、電流は流れませんが、これは現実には達成できません。デジタル値を0 Vまたは5 Vのどちらで読み取っても、NIデバイスのデジタル入力回路から少量の電流が流れます。高電圧レベルの測定時に流れる電流の量を入力HIGH電流と呼びます。同様に、低電圧レベルの測定に流れる電流の量を入力LOW電流と呼びます。測定対象のデジタル信号において、指定した電流値を許容できることが重要になります。

サンプル

NI PXIe-6363は、Vin = 0 Vの場合は最大10 µAをソースします。または、Vin = 5 Vの場合は最大250 µAをシンクします。これはすべてのデジタルおよびPFIラインに適用されます。

Input High Voltage / Input Low Voltage(VIH / VIL)(入力HIGH電圧/入力LOW電圧(VIH/VIL))

論理HIGHまたは論理LOWを登録するために入力信号として推奨される動作電圧レンジを指します。この仕様は推奨される動作条件を定めているため、ユーザには信号の本来の値がわかりますが、VT+とVT-はデバイス自体の仕様になります。

サンプル

NI PXIe-6363では、LOW信号として記録される電圧入力のレンジを0~0.8 Vと規定しています。HIGH信号では、このレンジは2.2~5.25 Vです。0V未満および5.25 Vを超える場合は、デバイスが過電圧保護状態になります。また、LOWからHIGHへ、またはHIGHからLOWへの変化がVIHまたはVILを超えるまで登録されない不確定なレンジも存在します。

関連トピック

入力電圧保護(デジタル)

個々のデジタル入力ラインには、静電気放電(ESD)および過電圧状態に対する専用のI/O保護が設けられています。デバイスの安全性を高めるため、すべてのデジタルラインとPFIラインで共有される第二レベルの保護が設けられています。複数のラインに同時に過電圧がかかると、この共有保護回路にストレスがかかり、デバイスが破損する恐れがあります。

サンプル

NI PXIe-6363は、同時に最大2つのピンで±20 Vの入力電圧保護を備えています。つまり、各ラインで個別に最大±20 Vの過電圧を安全に処理できますが、公称電圧入力を超えることのできるラインは一度に2つ以下です。

関連トピック

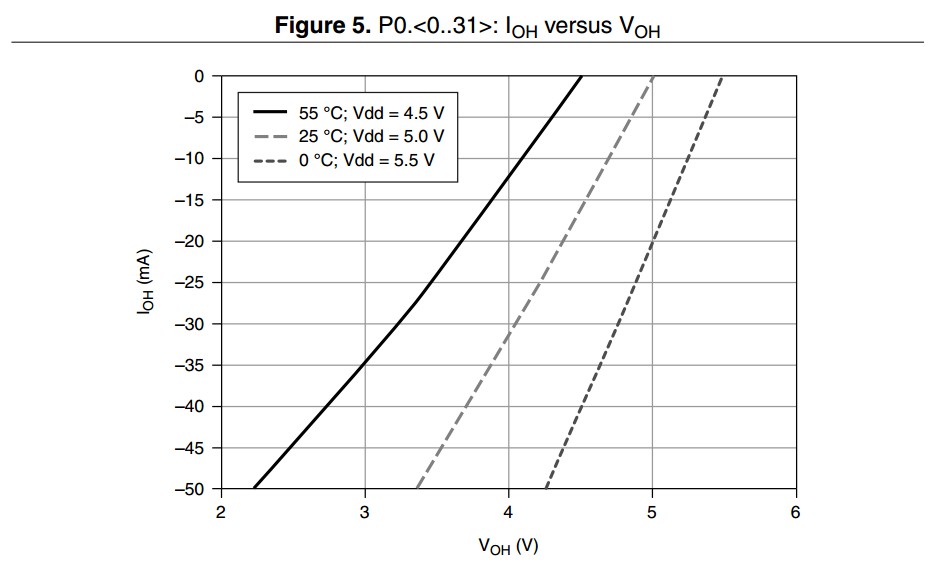

Output High Current / Output Low Current(IOH / IOL)(出力HIGH電流/出力LOW電流(IOH / IOL))

HIGHまたはLOWの値を出力する場合、ほとんどのNIデバイスの公称電圧は0および5 Vです。ただし、比較的低いインピーダンス負荷が接続されていると、要求される電流が大きくなり、この公称電圧が0 Vから上昇するか、5 Vから低下します。この仕様は、出力電流と出力電圧の関係の特徴を示しています。

サンプル

PXIe-6363は、ピンにHIGHの値が書き込まれるかLOWの値が書き込まれるかに応じて、電流をソースまたはシンクできます。ポート0の場合、ソースおよびシンク電流の最大推奨値はラインあたり24 mAです。電流がデバイスから流出する場合(ソース)、電流は-24 mAと表示されます。電流がデバイスに流入する場合(シンク)、電流は+24 mAと表示されます。特定の温度と出力電圧において流すことができる電流の特性については、次のグラフを参照してください。

Port/Sample Size(ポート/サンプルサイズ)

デジタル波形を集録または生成する場合、ポート0のライン数によってサンプルのサイズが定義されます。バス上のトラフィック量を制限するため、サンプルにライン0~7の任意の組み合わせが含まれている場合、サンプルのサイズは1バイトになります。同様に、サンプルにライン0~15のみが含まれている場合、サンプルのサイズは2バイトに縮小されます。これは、ポートの最大ライン数まで、ポート全体のサイズまで適用されます。

サンプル

NI PXIe-6363のポート0には32本のラインがあります。つまり、1つのデジタルサンプルの長さは最大32ビット(4バイト)になります。

正方向のしきい値(VT +)/負方向のしきい値(VT-)

デバイスに論理信号を入力するとき、信号が不確定のレンジから論理HIGHのレンジに変化する値のことを、正方向のしきい値と呼びます。逆に、論理LOWを登録するために超える必要がある電圧レベルのことを、負方向のしきい値と呼びます。正方向のしきい値は常に負方向のしきい値よりも大きくなります。デジタルの状態を正確に登録するためには、信号がこれら2つのレベルを確実に通過することが重要です。これらの仕様はデバイス自体を参照していますが、入力電圧の高低は推奨動作条件を参照しています。

サンプル

NI PXIe-6363のVT+は最大2.2 V、VT-は最小0.8 Vです。

関連トピック

Pull-down / Pull-up Resistor(プルダウン/プルアップ抵抗)

一部のNIデバイスは、デジタルまたはPFIラインを入力、出力、または高インピーダンスとしてプログラムで構成できます。プル抵抗は、本来ならばフローティングするピンにおいて、グランドや電圧ソースなどの既知の信号が基準となるようにするために使用します。プルダウン抵抗は、フローティング信号をグランド状態または論理LOWにプルします。プルアップ抵抗は、フローティング信号を論理HIGH電圧値にプルします。

サンプル

PXIe-6361では50 kΩのプルダウン抵抗を使用して、アクティブにHIGHまたはLOWに駆動されていない端子がLOW状態にフローティングするようにします。

波形集録(DI)FIFO

デジタル波形データを読み取る場合、データをバッファリングする一時的な格納要素(FIFOと呼ばれます)がデバイスに搭載されています。DAQmxは、このFIFOからRAM内のメモリブロック(PCバッファと呼ばれます)にデータをコピーします。ここから、LabVIEWなどのADEがデータをアプリケーションメモリにコピーします。FIFOのサイズと、FIFOにデータを格納する際のレートによって、DAQmxドライバがオーバーフロー状態を避けるためにデータをコピーする頻度が決まります。

サンプル

NI PXIe-6363は255サンプルのデジタル波形集録FIFOを備えています。たとえば、データを100 kbit/秒のレートで集録している場合、DAQmxドライバがデータをPCバッファに転送しなければオンボードFIFOは約2.5ミリ秒でオーバーフローします。

波形生成(DO)FIFO

FIFOと呼ばれる先入れ先出しデータ構造でデータポイントをバッファリングする、一時格納用のオンボードMIOデバイスがあります。このストレージは、バス経由の転送に時間がかかるUSBデバイスの場合、とりわけ多数のデバイスが同じUSBルートハブを共有する場合に、特に役立ちます。単一のデジタルパターンのみが必要な場合は、そのパターンをFIFOにロードすることで、何回もバス経由でデータを転送せずに済みます。ユーザはDAQmx APIを使用して、こうしたケースに対応したプログラミングができます。

サンプル

NI PXIe-6363は2,047サンプルのデジタル波形生成FIFOを備えています。たとえば、デジタル出力をデータレート100 kbit/秒のI2C通信に使用している場合は、FIFO全体が20ミリ秒で出力されます。このような場合、FIFOにデータをストリーミングし続けるためには、ユーザがそれよりも頻繁にDAQmx書き込みを呼び出す必要があります。データレートテストを行う場合は、DAQmx APIを使用して単一のパターンをFIFOにロードし、さまざまなデータレートで出力できます。PCI Expressバスを介して新しいデータを書き込む必要はありません。

カウンタの仕様

Base Clock Accuracy(general-purpose counters)(ベースクロック確度(汎用カウンタ))

内部ベースクロックの確度は、汎用カウンタからのあらゆる測定または周波数生成の確度に直接影響します。この確度はデバイス全体のタイムベース確度からも継承されます。つまり、より高い確度のマスタタイムベースが外部から提供されている場合、このクロックの確度を向上させることができます。

サンプル

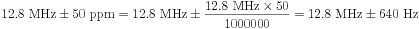

PXIe-6363のベースクロック確度は50 ppmです。ユーザがこのモジュールで12.8 MHzの自走クロックを生成する必要がある場合は、次の計算で確度を決定できます。

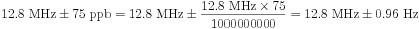

より高い確度の外部ベースクロックや、より優れたベースクロック確度を持つPXIe-6614などのデバイスを使用することで、この誤差を改善できます。PXIe-6614では、温度変動の影響を受けにくく、最悪の場合でも75 ppbのベースクロック確度で動作する、より正確で安定した恒温槽付水晶発振器(OCXO)を使用しています。このモジュールで同じ信号を生成すると、実際の周波数は次のようになります。

Counter Resolution (カウンタ分解能)

カウンタで数値の表現に使用できるビット数を指します。汎用カウンタがパルスを出力するように構成されている場合、パルスがアクティブである時間の長さは、カウンタのレジスタの値によって表されます。この値と、カウンタがカウントしているレート(カウンタのベースクロックにより設定)の組み合わせによって、達成可能な最大パルス幅が決まります。同様に、カウンタを使用して信号のパルス幅を測定する場合、登録できる最大パルス幅は、カウンタのベースクロックとカウンタの分解能によって決まります。信号が最大パルス幅を超える場合、カウンタはロールオーバーし、NI-DAQmx APIはエラーを返します。このため、最大信号パラメータの計算方法を知っておくことが重要です。

分解能と測定/生成の長さとの間でトレードオフを行う場合、カウンタの分解能が高いほど柔軟性が高まります。このトレードオフの詳細については、次のグラフを参照してください。

サンプル

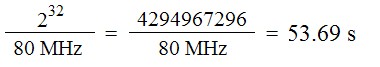

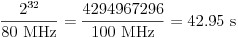

PXIe-6614は、カウンタ入力タスクとカウンタ出力タスクに32ビットのカウンタを使用します。カウンタ入力タスクがパルス幅を測定するように構成されている場合、測定可能な最大パルス幅を計算するには、最大カウンタ値を計算し、カウンタの内部ベースクロックレートで割ります。100 MHzのカウンタベースクロックでは10ナノ秒の精度が可能になるため、そうした例ではベースクロックが選択されます。

External Base Clock Frequency (general-purpose counters) (外部ベースクロック周波数 (汎用カウンタ))

特定のベースクロックレートが必要な場合、ほとんどのNI MIOデバイスでは外部ベースクロックを使用することができます。このクロックは内部ベースクロックと同じ目的のすべてで使用できますが、ユーザが外部から提供します。帯域幅の制限により、外部ベースクロックの最大レートはデバイスのバスに依存します。

サンプル

NI 6363は、外部ベースクロックの要件が異なる複数のフォームファクタで提供されます。

- PCI ExpressおよびUSB - 外部ベースクロックの周波数レンジは0~25 MHzで、任意のPFIラインに入力します。最大周波数の制限は、PFIラインの帯域幅によるものです。

- PXI Express - PXIe-6363では、PXI Expressシャーシの高度な機能を利用して、差動スターライン(DSTAR)で最大100 MHzの信号が可能です。

FIFO(general-purpose counters)(FIFO(汎用カウンタ))

MIOデバイスに搭載された先入れ先出し(FIFO)メモリ要素は、入力または出力アプリケーションのデータのサンプルをバッファリングするために使用されます。カウンタ入力アプリケーションの場合、データポイント(特定の間隔でのカウンタ値など)がFIFOに保存された後、DAQmxによって、PC RAMの事前割り当てされたブロックにデータが自動的に転送されます。カウンタ出力アプリケーションでは、FIFOを使用して一連のデューティサイクルと周波数値を保存し、生成される波形の形状を変更します。デバイスに搭載されたFIFOが大きいほど、小さなFIFOと比べて大きなデータブロックを少ない頻度で転送でき、データバス上のトラフィック量が減少するので便利です。

サンプル

PXIe-6614には、カウンタごとに127サンプルを格納するFIFOがあり、バス経由で別途転送が必要になる前に127個の異なるパラメータをパルス列生成用に構成できます。

内部ベースクロック(汎用カウンタ)

カウンタの内部ベースクロックは、ゲート端子の状態に応じてカウンタの値を増減させる信号です。このクロックの周期によって、測定または生成される信号の秒単位の分解能が決まると同時に、長いパルスを測定または生成するときにカウンタがロールオーバーする速度も決まります。カウンタの測定またはアプリケーションでは、タイムベース周期の量子化誤差が±1存在します。量子化誤差の量を最小限に抑えるため、アプリケーションに対して可能な限り最速のベースクロックを選択することが重要です。

サンプル

PXIe-6614を使用して測定を実行する場合、使用可能な内部ベースクロックのレートは、100 kHz、20 MHz、100 MHzの3つです。これらのベースクロックは10マイクロ秒~10ナノ秒の分解能を提供します。125 kHzでデューティサイクルが35%のPWM信号を適用する場合、実際の秒単位のパルス幅は2.8マイクロ秒になります。これは100 kHzベースクロックの分解能を下回っているため、この測定には使用できません。20 MHzクロックの分解能は50ナノ秒なので、この信号±1のベースクロックパルスの持続時間を完全に測定できます。この結果、測定値は2.8マイクロ秒±0.05マイクロ秒、誤差は約1.8%となります。同じ測定を100 MHzクロックで行うと、測定値は2.8マイクロ秒±0.01マイクロ秒、誤差0.36%となります。この場合、100 MHzクロックではカウンタがロールオーバーする前に最大約43秒のパルス幅を測定できるため、この2.8マイクロ秒というパルス幅は最大制限を大幅に下回っています。

関連トピック

その他の仕様

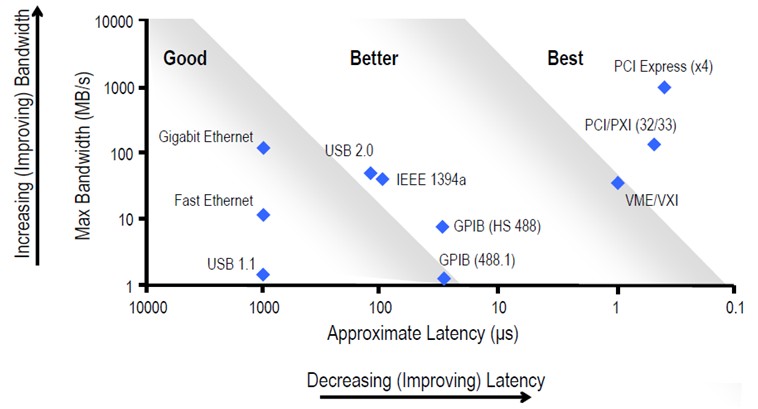

Bus Interface(バスインタフェース)

PCI、PCI Express、PXI、PXI Express、USBはすべて、MIO DAQデバイスで使用できるバスインタフェースの例です。これらのバスは、データスループット、レイテンシ、移植性、チャンネル数に関していくつかの重要なトレードオフを提供します。

サンプル

NI 6363は、USB、PXI Express、およびPCI Expressで提供されます。これらのデバイスとモジュールは同様の機能を備えていますが、PXI ExpressモジュールとPCI Expressデバイスは、USBデバイスと比較して低レイテンシと高スループットを提供します。PXI Expressモジュールでは、さらにPXI Expressシステムが持つ利点が加わります。USBデバイスはホットスワップ可能であり、他と比べてコンパクトなためモバイルアプリケーションに適しています。

キャリブレーション

あらゆるテスト装置や測定機器と同様に、デバイスが指定された確度設定内で動作することを確認するために、定期的なキャリブレーションを実行することが重要です。デバイスではある程度の自己発熱が生じるため、測定を行う前に、安定した温度に到達するまで、指定されたウォームアップ時間を確保することが重要です。温度が安定した時点で、デバイスのセルフキャリブレーションを行うことをお勧めします(サポートされている場合)。NIが提供しているキャリブレーションサービスの詳細については、「キャリブレーションサービス」を参照してください。

サンプル

USB-6363のウォームアップ時間は15分で、キャリブレーション間隔は2年です。最適な確度を確保するため、電源を入れてから15分後にデバイスのセルフキャリブレーションを行うことをお勧めします。使用期間が2年経過したら、デバイスをNIに送付して認定済みのキャリブレーションを受けることをお勧めします。

Current Limits(電流制限)

すべてのMIOデバイスには、シンクまたはソースできる最大量の電流が定められています。このセクションの仕様は、シンク電流とソース電流の両方を組み合わせたものです。デバイスによっては、偶発的なサージが発生した場合に備えて+5 Vのユーザラインにセルフリセットヒューズを備えています。最大電流の仕様を超えると、デバイスが破損する恐れがあります。

サンプル

PXIe-6363がポート0にある32本のDIOラインすべてから最大電流を駆動している場合(ラインあたり24 mA)、ポート0からの合計電流は0.768 Aになります。コネクタ0およびコネクタ1にある+5 Vユーザラインにも回路が接続されていて、各コネクタから0.25 Aが流れている場合、モジュールからは合計1.268 Aが供給されることになります。この0.25 Aは各電源コネクタの最大である1 Aの範囲内にあります。また、DIOラインから流れている0.768 Aと+5 Vユーザラインから流れている0.5 Aの和は、すべての合計出力の最大である2 Aの範囲内にあります。これと同じアプリケーションをPCIe-6363で使用する場合は、オプションのディスクドライブコネクタを接続して、デバイスが最大電流制限の範囲内で動作することを確かめる必要があります。

Environmental Management(環境管理)

NIでは環境に配慮した製品の設計、製造に取り組んでいます。詳細については、「環境に対する取り組み」をご覧ください。

External Digital Triggers(外部デジタルトリガ)

MIOデバイスは、任意のPFIラインからデジタルトリガ信号をインポートすることができ、デバイスで同期の目的で使用される最も一般的な信号の一部をエクスポートすることもできます。サンプルクロックや開始トリガなどの信号は、MIOデバイスから出力できます。これらの信号のいずれにも、DAQmx APIを使用してデジタルフィルタを適用できます。これらのトリガ経路の詳細については、NI MAXに記載されているデバイスのルーティング表を参照してください。

- 極性 - エクスポートまたはインポートする信号がアクティブHIGHかアクティブLOWかを示します。

サンプル

PXIe-6363は、アナログ入力開始トリガを、別のタスクまたはデバイスで使用するために予約されていない任意のPFI、PXIe_DSTARA、PXIe_DSTARB、PXI_TRIG、またはPXI_STARラインにルーティングできます。MAXに記載されているデバイスの経路を見ると、このルーティングは双方向にもなっています。つまり、デバイスはこれらと同じどのソースからのアナログ入力開始トリガも受け付けることができます。

Frequency Generator(周波数発生器)

MIOデバイスに備わっている汎用カウンタに加えて、周波数発生器として使用できる、機能が制限された別のカウンタがあります。通常、MIOデバイスには単一の周波数発生器が備わっていますが、生成できる周波数は有限数に制限されています。ここから生成可能な周波数は、デバイス上の別のサブシステムにクロック信号を供給するために使用したり、外部回路で使用するためにエクスポートしたりできます。

サンプル

PXIe-6363には、3つのベースクロック(20 MHz、10 MHz、100 kHz)の1つを受け取り、それを1から16までの除数で分割できる周波数発生器チャンネルが備わっています。ユーザが50.0 kHz信号を生成する必要がある場合は、100 kHzのベースクロックと2の除数を選択できます。次の表は生成可能な周波数の一部を示しています。

| 除数 | ベースクロック | ||

|---|---|---|---|

| 20 MHz | 10 MHz | 100 kHz | |

| 1 | 20 MHz | 10 MHz | 100 kHz |

| 2 | 10 MHz | 5 MHz | 50 kHz |

| 3 | 6.67 MHz | 3.33 MHz | 33.3 kHz |

| ... | |||

| 15 | 1.33 MHz | 0.67 MHz | 6.67 kHz |

| 16 | 1.25 MHz | 0.63 MHz | 6.25 kHz |

Operating Temperature(動作温度)

MIOデバイスの動作範囲として想定された周囲温度範囲を示します。この温度は、オンボード温度センサであるDAQmx APIを使用して報告されるものとは異なります。

サンプル

PXIe-6363の動作温度範囲は0~55℃です。通常の使用中に、これよりも高い温度がPCB温度センサから報告される場合がありますが、これは許容の範囲内です。

Phase-Locked Loop(PLL)(位相ロックループ(PLL))

一部のMIOデバイスでは、デバイスが自身の基準クロックを外部基準クロックにロックできるようにする位相ロックループ回路がオンボードで搭載されています。デバイスが外部基準クロックにロックされると、ロックされたクロックのレート、ドリフト、および確度が継承されます。PXIまたはPXI Expressデバイスは、PXI_CLK10またはPXI_CLK100基準クロックに自動的にロックされます。NI-DAQmx APIを使用すると、PFIラインなどの別の基準クロックソースにロックできます。

サンプル

USB-6363にはPLL回路が1つオンボードで搭載されており、10 MHzクロックがPFIライン0~15のいずれかに存在する場合はそのクロックにロックできます。DAQmx APIを使用してタスクを構成する場合は、外部クロックが接続されているPFIラインに基準クロックを設定します。PXIe-6363にも同様のPLL回路がありますが、PXI Expressシャーシ内の複数のデバイス間で同期を取る場合は、DAQmx APIを使用して基準クロックソースを設定しない限り、PXI_CLK100の100 MHzクロックに自動的にロックされます。PCIe-6363には、同様に任意のPFIまたはRTSIラインにロックできるPLL回路があります。PCI ExpressまたはUSBデバイスには自動ロックはありません。

Physical Characteristics(物理特性)

NIではほとんどの製品について寸法図を公開しています。これらの寸法図は、デバイスを購入する前にクリアランスを確認したり、開発するシステムのモデルを作成したりする目的で使用できます。また、外形寸法に加えて、カスタムのケーブル、コネクタ、ネジの包括的なリストも提供しています。

関連トピック

Power Requirements(所要電力)

正しい電力量を供給できるように、USBデバイス、PCIデバイス、またはPXIモジュールについて、その所要電力を知っておくことが重要です。このセクションに示されている値は通常の使用に対するものであり、仕様の範囲外で使用する場合にデバイスまたはモジュールで使用できる最大電力を示すものではありません。USBデバイスの場合、NIが提供している電源は推奨仕様を満たしていますが、必要に応じてサードパーティまたはカスタムの電源を使用できます。PCIまたはPCI Expressデバイスの場合、より多くの電力が必要な場合に使用できる補助電源コネクタを備えています。これは、+5 Vユーザレールを使用して外部回路に電力を供給する場合によく使用されます。詳細については、「電流制限」[電流制限へのリンク]を参照してください。PXIまたはPXI Expressモジュールの場合、この仕様はパワーバジェットを作成する際に役立ちます。詳細については、関連リンクをご覧ください。

サンプル

PCIe-6363は、オプションのディスクドライブ電源コネクタを取り付けない場合、+3.3 Vレールから4.6 W、+12 Vレールから5.4 Wを供給します。ディスクドライブコネクタを使用すると、デバイスに最大15 Wを供給できる+5 Vレールが追加されますが、+3.3 Vレールから供給される電力が1.6 Wに減少します。

関連トピック

Safety、Electromagnetic Compatibility、CE Compliance(安全性、電磁両立性、CE準拠)

MIOデバイスでテストを行い準拠を確認した規格については、仕様書の3つのセクションに記載されています。規格の詳細については、「製品の規格認証」をご覧ください。

サンプル

認証検索を使用してPXIe-6363の準拠仕様を確認できます。NI PXIe-6363 - 製品の規格認証

Shock and Vibration(耐衝撃/振動)

MIOデバイスは、仕様およびデバイスの整合性に基づいて規定された確度が、定められた耐衝撃/振動の仕様にわたって維持されていることを保証するために、特定の業界規格に準拠するようにテストされています。デバイスで適正かつ正確な操作を行うために、これらの規定値を超えないようにすることが重要です。

サンプル

PCIe-6363は、IEC-60068-2-27に準拠してテストされ、MIL-PRF-28800Fに準拠してテストプロファイルが確立されました。