ni.com is currently undergoing scheduled maintenance.

Some services may be unavailable at this time. Please contact us for help or try again later.

信号の生成:関数発生器のタイプ、DACの考慮事項、その他の一般的な用語

概要

信号発生器がアナログ信号を生成する方法、および信号発生器のタイプ、ビット分解能、帯域幅、減衰、デジタルゲイン、デジタルフィルタ処理、アナログフィルタ処理などのテーマについて学習します。

内容

信号発生器のタイプ

広範な信号発生器のカテゴリには、さまざまなタイプのデバイスが含まれます。より上位のレベルでは、次の2つの主要なグループがあります。(1) 信号発生器 (任意/関数発生器および任意波形発生器とも呼ばれる) (2) 論理ソース (パルス発生器またはパターン発生器とも呼ばれる)信号発生器はアナログ特性を持つ波形を生成し、論理ソースはコンピュータバスのテストに一般的に使用されるデジタル波形を生成します。この記事では、信号発生器について説明します。

関数発生器

関数発生器は、限られた数の定義済み周期波形を正確な周波数で生成します。最近の関数発生器には、ダイレクトデジタルシンセシス (DDS) と呼ばれるテクノロジが採用されており、デバイスは正確な周波数で波形を生成できます。DDSを使用した関数発生器は、短い応答時間で生成中に出力波形周波数を変更できます。DDSの詳細については、計測器の基礎シリーズの「ダイレクトデジタルシンセシス (DDS)」ホワイトペーパーを参照してください。関数発生器は、少量の周期波形のみを保存するため、メモリサイズがとても少ない場合がしばしばあります。関数発生器のメモリには、正弦波、方形波、パルス波、ランプ波、スイープ波などの一般的な波形が含まれています。ただし、デバイスによっては、使用可能な波形オプションが多少異なる場合があります。関数発生器は、刺激応答テスト、フィルタ特性評価、クロックソースシミュレーションなど、周期的な波形のみを必要とするアプリケーションに適した費用対効果の高いデバイスです。

任意関数発生器

任意関数発生器 (AFG) は、関数発生器に似ていますが、重要な追加機能 (ユーザ定義波形専用のオンボードメモリ領域) があります。これにより、波形を定義して、AFGオンボードメモリに保存し、DDSを使用して波形を出力することができます。関数発生器と同様に、AFGにも、DDSを使用して出力可能なデバイスのオンボードメモリに格納された事前定義済みの波形セットがあります。したがって、関数発生器に適した同じ種類のアプリケーションを使用する場合には、AFGは非常に価値のあるデバイスです。しかし、ベンダーが提供する事前定義済み波形ではない独自の波形を定義できるという利点があります。購入する前に、ユーザ定義波形がデバイスのユーザ使用可能メモリに収まることを必ず確認してください。

任意波形発生器

任意波形発生器 (AWG) は、標準波形だけでなく、大規模で複雑なユーザ定義波形も生成できます。一部のAWGでは、出力する波形シーケンスを効率的に生成するために、波形の組み合わせをリンクおよびループする機能が追加されています。複雑な波形やシーケンスされた波形を出力するために、AWGは大量のオンボードメモリを使用して、これらの波形を保存する必要があります。そのため、アプリケーションで特定の複素波形を使用する予定がある場合は、該当する波形を保存するのに十分なメモリを備えたAWGを購入してください。メモリ領域の増加だけでなく、AWGは関数発生器やDDSを使用するAFGとは異なるクロック機能方式も採用しています。AWGのクロック機能方式では、デバイスはメモリに配置された順序でのみポイントを出力できます。つまり、出力周波数を短時間で変更することはできません。

デジタル/アナログ変換特性

ビット分解能

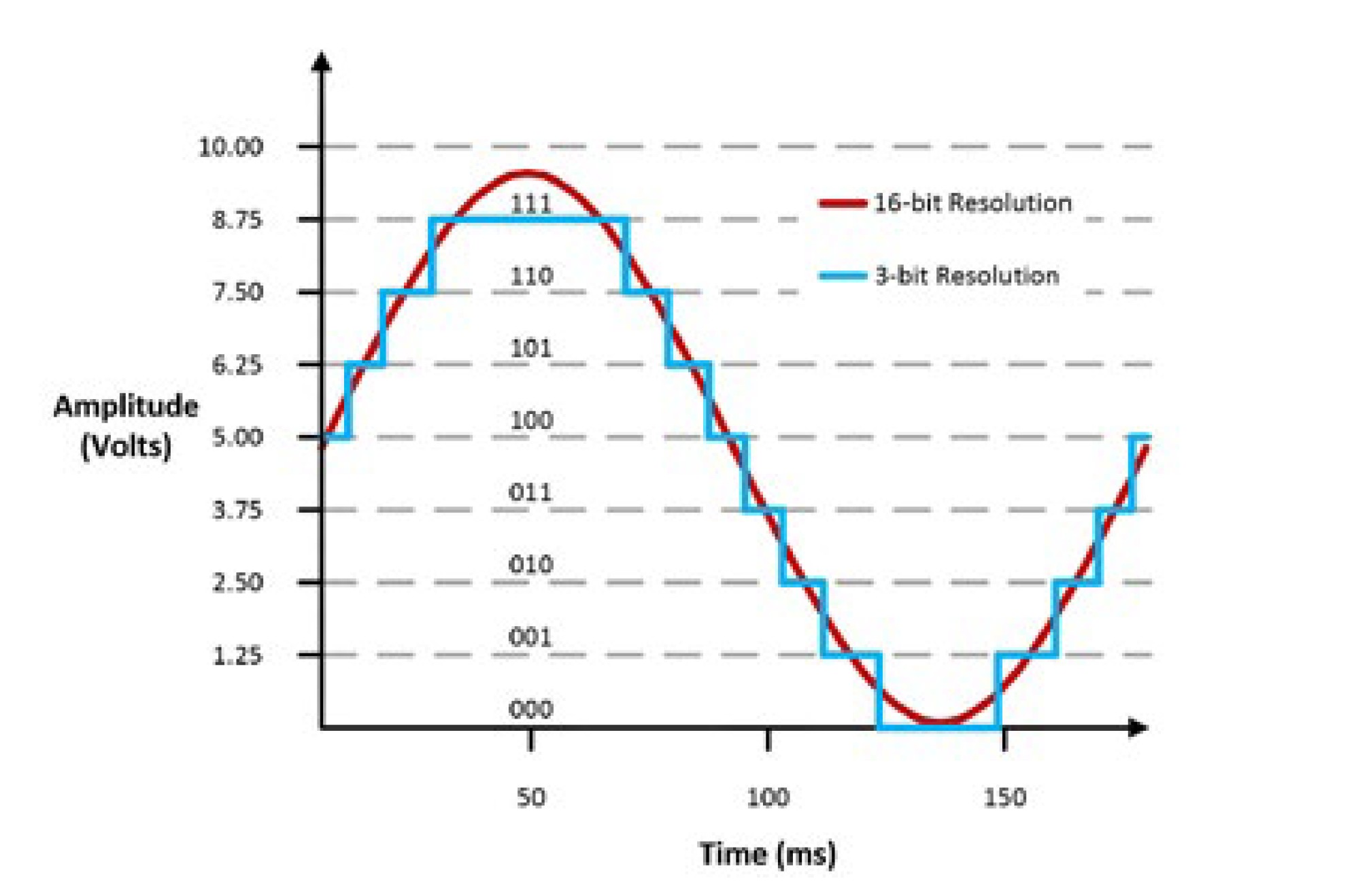

信号発生器のビット分解能 (垂直分解能) は、使用するデジタル/アナログ変換器 (DAC) の分解能で定義されます。DACは、離散電圧ステップ (レベル) を使用してのみ出力波形を生成できます。DACが生成できる離散電圧レベルの数は、2のDAC分解能の累乗で求めることができます。図1は、理論上の3ビットDACによって生成された正弦波と16ビットDACによって生成された正弦波を比較することにより、さまざまなDAC分解能の違いを示しています。

図1:アナログ信号生成における2つの異なるDAC分解能の違い

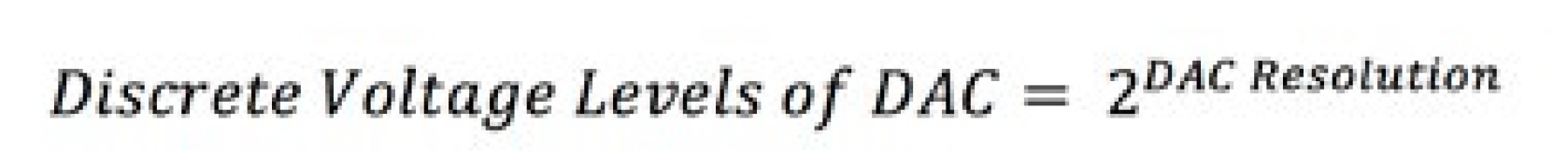

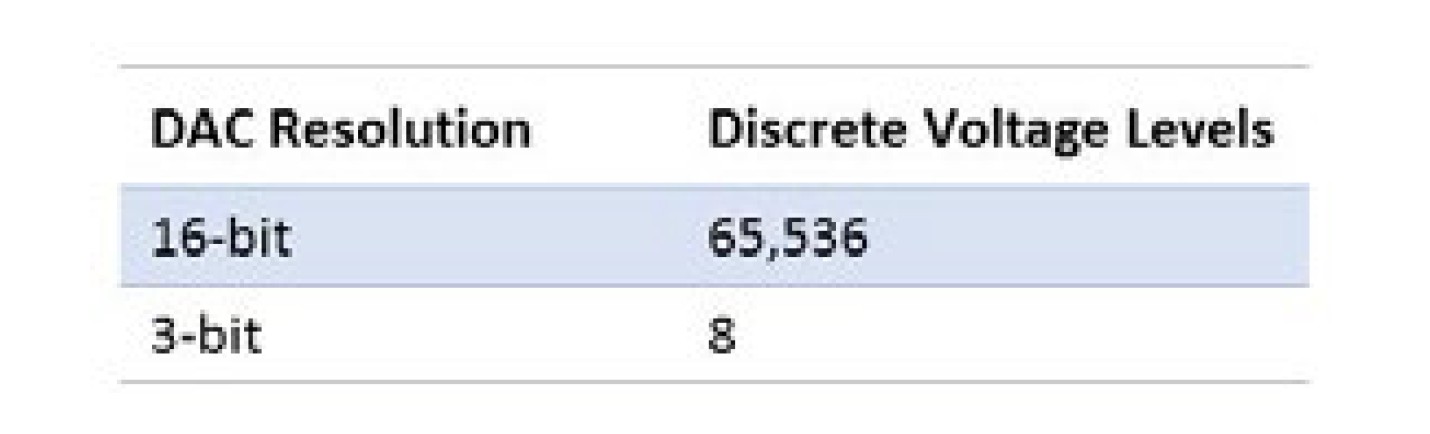

表1は、各DACが生成できる離散電圧レベル数を示し、式1はDACの離散電圧レベル数の計算方法を示しています。

式1:DACの離散電圧レベルの計算

表1:3ビットおよび16ビットDACの離散電圧レベル

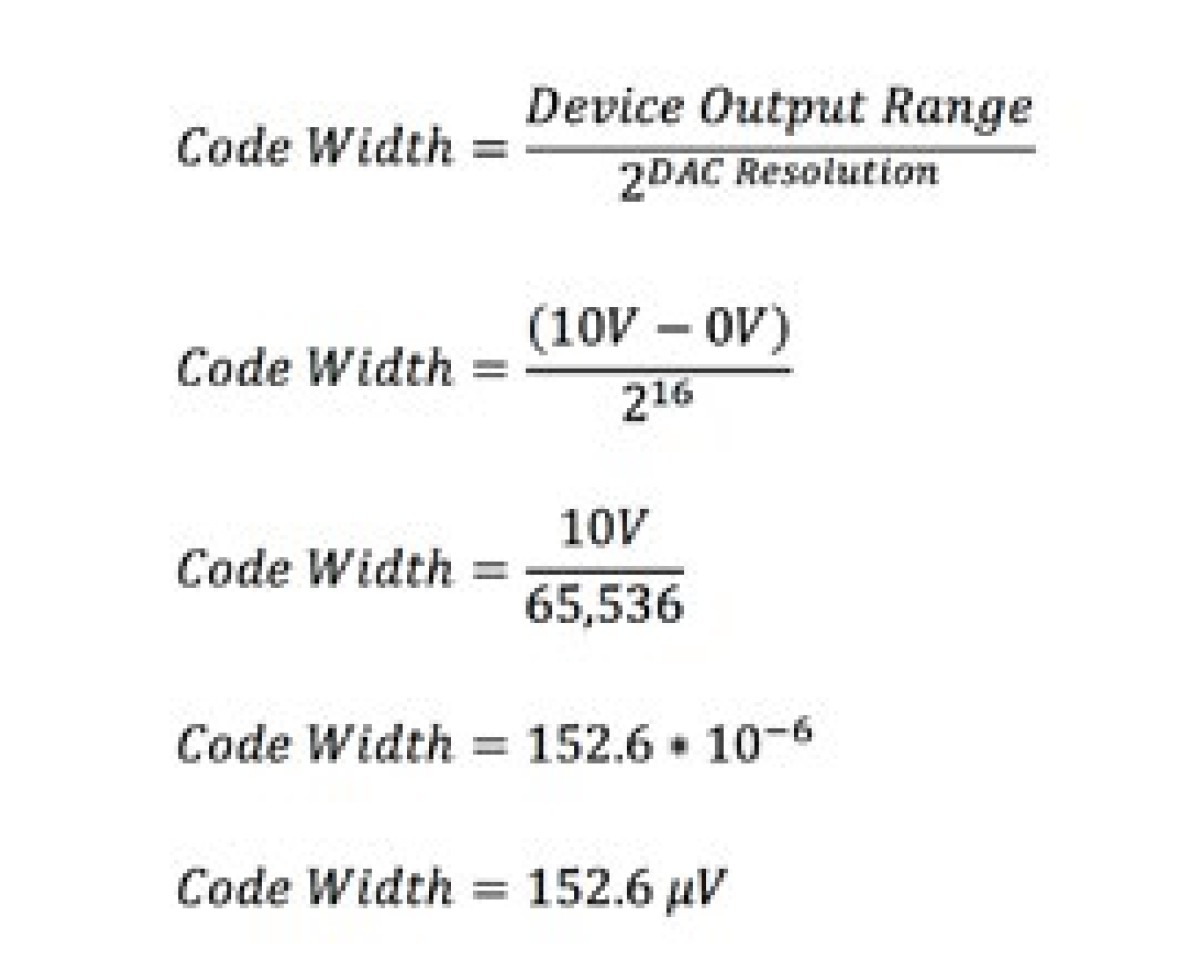

3ビットDACは、8つの離散電圧レベルのみを出力できます。したがって、DACの信号範囲が0 V~10 Vの場合、図1に示すように、1.25 V刻みの電圧しか生成できません。16ビットDACは、152.6 μV刻みで電圧を生成できるため、信号がより滑らかに表示されます。式2は、一般的な式と、16ビットDACの電圧増分 (一般にコード幅と呼ばれる) の計算方法を示しています。

式2:16ビットDACのコード幅の一般式とコード幅の計算例

十分に小さいスケールに拡大すると、16ビットDACによって生成された正弦波も152.6 μV増分で段階的に表示されます。

帯域幅

AFGまたはAWGの帯域幅は、デバイスのアナログ回路が大幅な減衰なしで出力できる最大周波数を表します。帯域幅仕様の最大周波数は、正弦波出力信号が信号の元の振幅の70.7%に減衰する周波数として定義されます。この周波数は、ボード線図の-3 dBポイントとしても知られています。

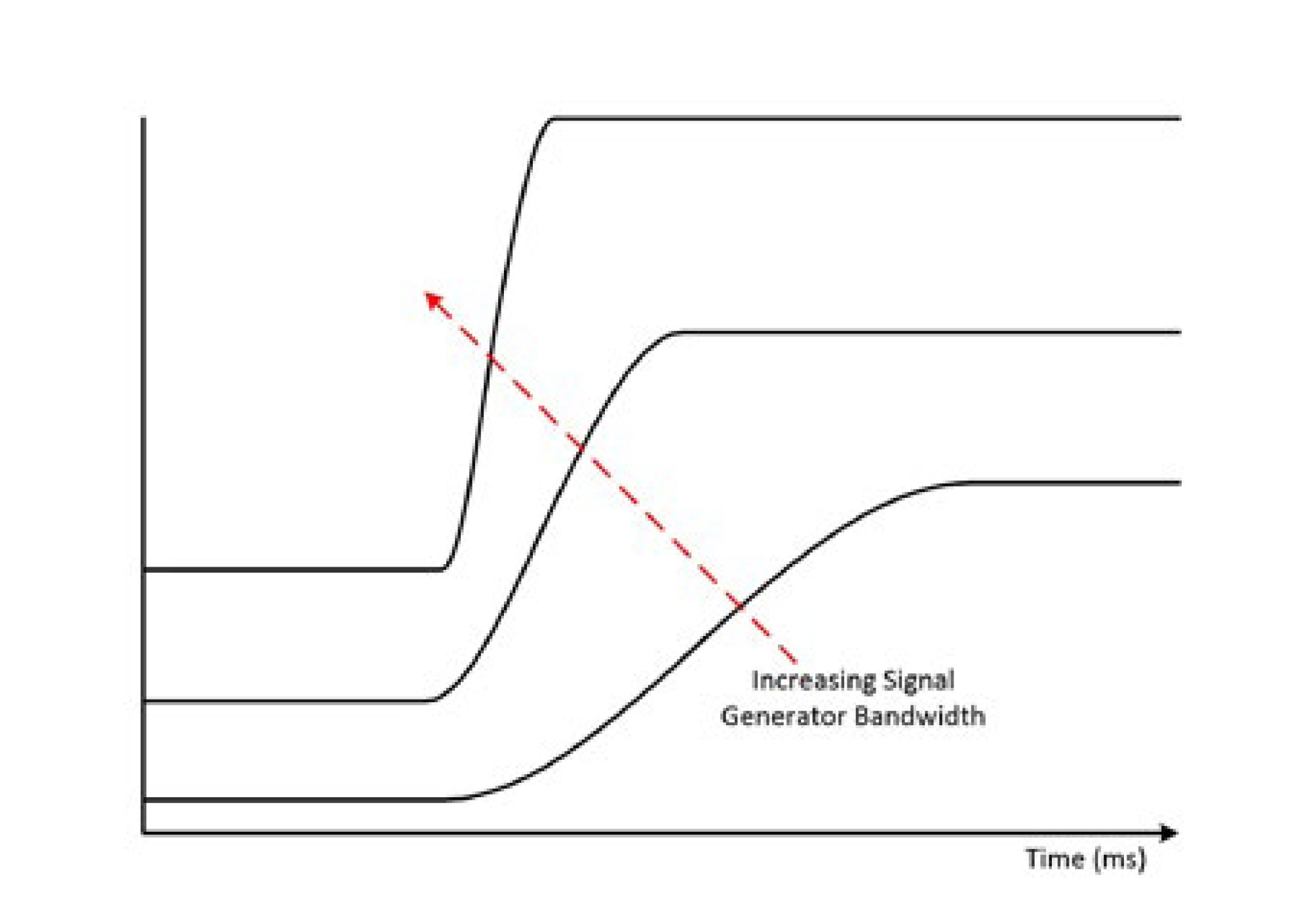

帯域幅仕様は、正弦波出力の最大周波数、計測器のオーバーシュートや立ち上がり時間などのその他の仕様を決定します。これは、信号発生器で方形波またはパルス信号を生成する場合に重要になります。図2に示すように、より高い帯域幅の信号発生器では、オーバーシュートが小さく、立ち上がり時間が速い方形波を生成できます。

図2:より高い信号発生器の帯域幅では、信号の表現が向上する。この図では、信号は方形波となる。

減衰とデジタルゲイン

信号発生器は、さまざまな電圧範囲で波形を生成するように設計されており、これらの電圧範囲を素早く切り替えることができます。サポートされている電圧範囲とその実装方法によっては、電圧範囲を変更すると、リレースイッチで信号の物理的な経路を変更する必要がある場合があります。これは出力信号に影響し、グリッチを発生させる可能性があります。このタスクを実行するために、信号発生器は以下の方法を使用できます。

減衰

DAC出力信号を減衰することで、信号発生器はDACのダイナミックレンジを使用しながら、生成された信号の振幅を変更できます。これを説明するために、0~10 Vの範囲の16ビットDACが使用されているが、必要な出力信号の範囲が0~1 Vの場合を考えてみます。 必要な出力信号を生成するには、デジタルデータを0~10 Vの全範囲でDACに書き込み、DACの出力でアナログ信号を10倍に減衰します。これにより、16ビットDACの最大分解能が使用されたため、電圧分解能は実質的に15.26 μVに低下します。0~10 V範囲で0~1 Vの値を表すデジタルワードだけをDACに書き込んで0~1 V信号を生成した場合、電圧は分解能式2に示すように、152.6 μVのままになります。減衰はDACの最大分解能を使用しますが、抵抗ネットワークの組み合わせを切り替える必要があるため、多くの場合、速度が遅い手法です。

デジタルゲイン

デジタルゲインは、波形デジタルデータがDACに到達する前に、そのデータを係数で乗算することを含む手法です。デジタルゲインはデジタルデータが信号発生器のメモリから転送される間の波形生成中に適用されるため、デジタルゲインの適用に関連する遅延はアナログゲイン方法と比較して最小限に抑えられます。ただし、DACの出力分解能はデジタルゲインの関数であるため、アナログゲインのみがDACの最大分解能を使用できます。

フィルタ処理と補間

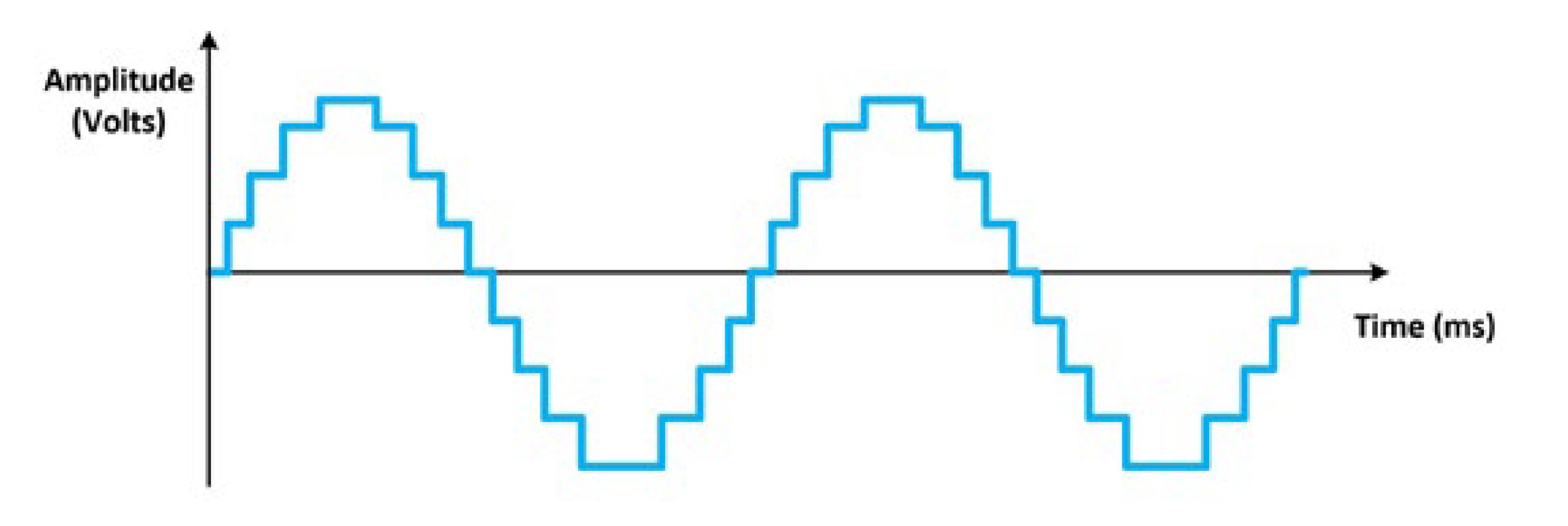

適切な周波数で信号を生成するには、デバイスのアップデートレートまたはサンプリングレートが、生成される信号の最大周波数成分の2倍である必要があります。この基準に厳密に従うと、正しい周波数の信号のみが生成されますが、波形形状の最も正確な表現を生成するには、DAC動作を考慮する必要があります。DACはサンプルホールド技術を使用するため、高度にオーバーサンプリングされた波形でも高周波数画像が発生します。正弦波が正弦波周波数の20倍でサンプリングされた場合、図3の時間領域でサンプルホールド出力を視覚的に見ることができます。サンプルホールド出力は、ステップ状の波形を提供します。

図3:生成された正弦波のこの時間領域グラフは、DACで使用されるサンプルホールド技術を示す。

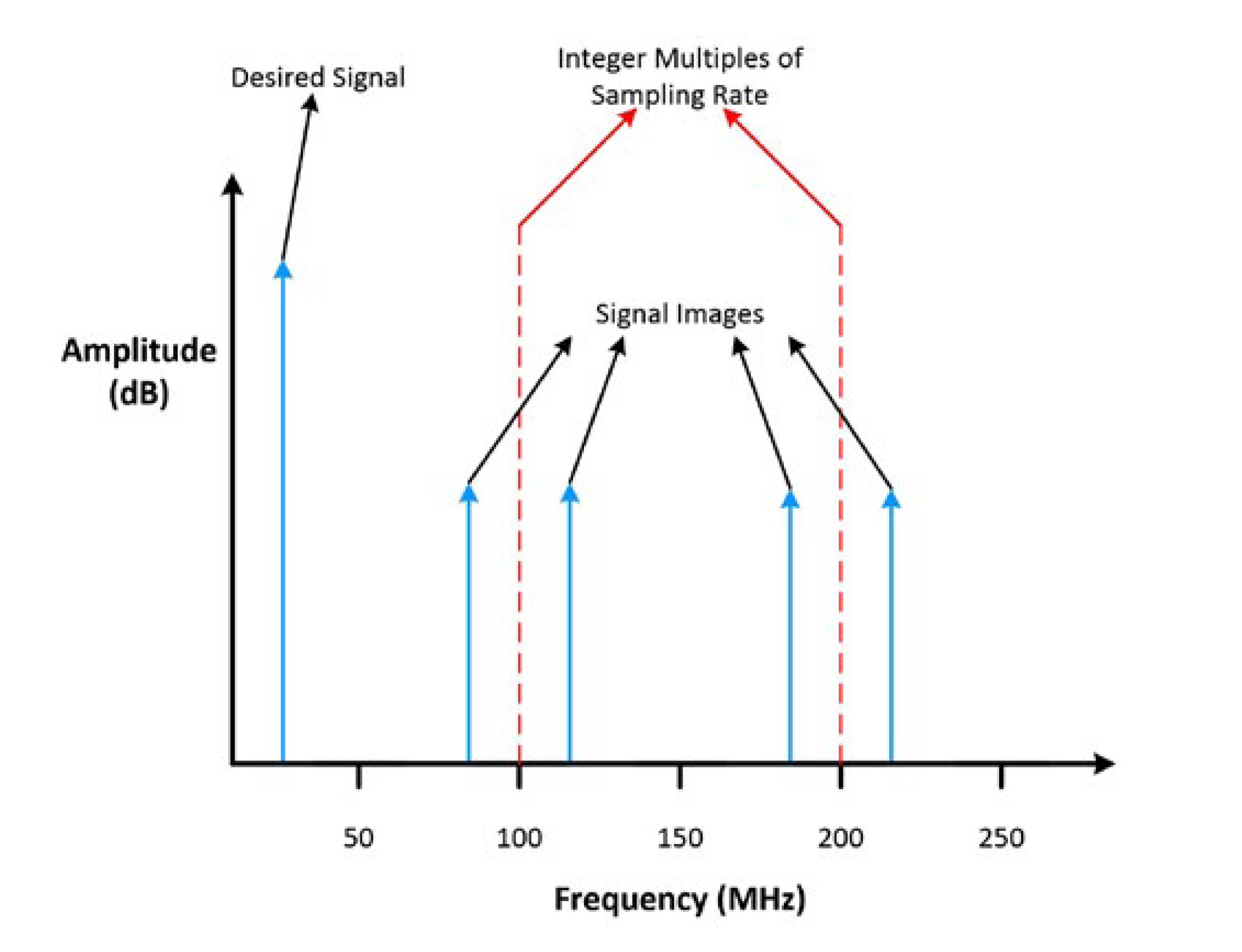

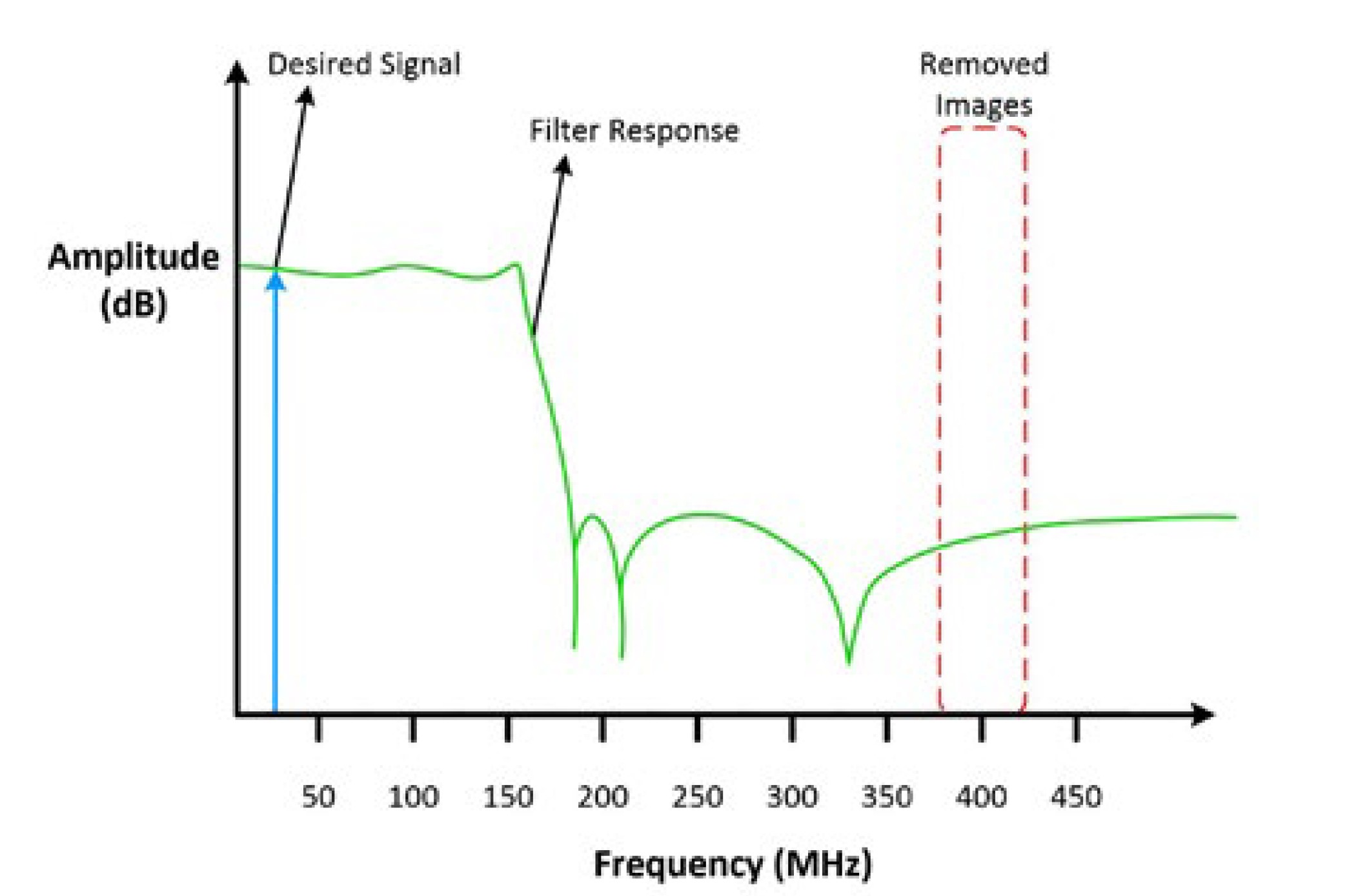

時間領域信号は正弦波に似ています。ただし、周波数領域を調べると、DACによって生成された高周波数の画像が現れます。これらの画像は、サンプリングレートに基本トーンを加算または減算した整数倍で発生します。たとえば、100 MHzのサンプリングクロックによって生成された20 MHzの正弦波には、80 MHz、120 MHz、180 MHz、220 MHzなどの画像が含まれます。図4は、生成された正弦波の周波数領域と高周波数画像を示します。

図4:生成された正弦波のこの周波数領域グラフは、高周波数画像を示す。

信号発生器は、デジタルフィルタとアナログフィルタを組み合わせてこれらの画像を除去し、より純粋なスペクトル信号を生成します。

デジタルフィルタ処理と補間

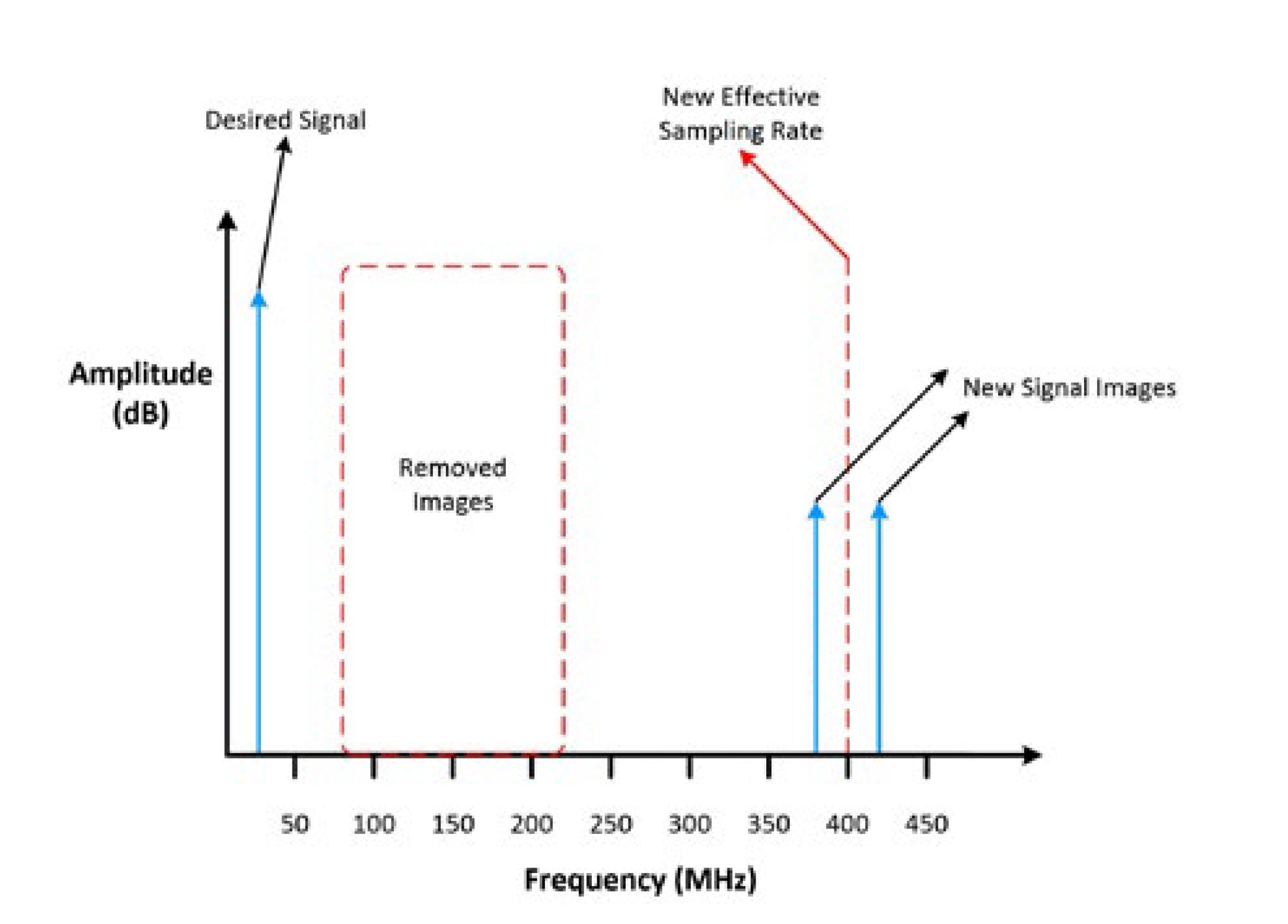

信号発生器は、デジタル有限インパルス応答 (FIR) フィルタを使用して、生成されたサンプル間を補間するポイントを提供できます。これにより、有効サンプリングレートが増加し、周波数領域での高周波数画像の位置が変化します。この概念の説明として、100 MHzのサンプリングクロックによって生成された20 MHzの正弦波の元の例を考えてみましょう。FIRフィルタが信号を4倍で補間する場合、サンプリングクロックレートに400 MHzを使用して画像を検出できるため、380 MHz、420 MHz、780 MHz、820 MHzなどの画像が生成されます。図4では、元画像は80 MHz、120 MHz、180 MHz、220 MHzなどでした。以下の図5が示すように、補間によってスペクトル画像は除去されませんが、これらの画像は基本トーンから大きくシフトします。

図5:生成された正弦波のこの周波数領域グラフでは、デジタルフィルタ処理により高周波数画像が基本トーンからさらに遠ざけられている

アナログフィルタ処理

最も純粋なスペクトル信号を生成するには、補間信号の後にアナログフィルタを適用します。デジタルFIRフィルタは高周波数画像を基本トーンから遠ざけるため、アナログフィルタの要件が緩和されました。アナログフィルタには、回路のパスバンドフラットネスを低下させるような急峻なカットオフ周波数は必要ありません。図6に示すように、デジタルFIRフィルタとアナログフィルタを適用後、高周波数画像は周波数領域から削除されます。

図6:デジタルおよびアナログフィルタ処理の適用後に生成された正弦波の周波数領域グラフ。

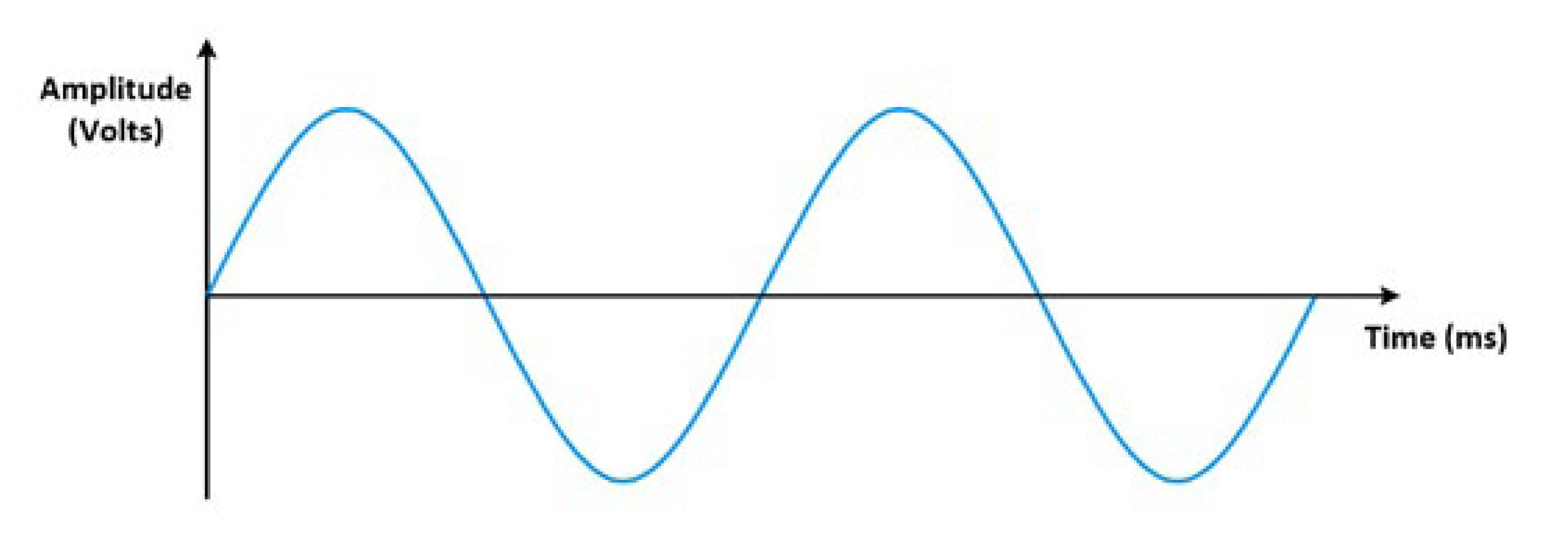

デジタルFIRフィルタとアナログフィルタが高周波数画像を効果的に除去したため、図7の正弦波形を時間領域で再検査できます。

図7:デジタルおよびアナログフィルタ処理後に生成された正弦波形の時間領域グラフ。

高周波数画像によって作成された階段状の波形の外観が削除され、生成された正弦波信号が図1の正弦波と比較して、より純粋な正弦波に見えることに注目してください。

ここまで、ビット分解能、帯域幅、減衰、ゲイン、フィルタ処理によって、信号発生器からの出力信号がどのように影響するかを説明してきました。信号発生器の仕様書シートを参照する際は、これらの仕様を念頭に置き、アプリケーションの要件と一致させてください。

まとめ

- 関数発生器は、正確な周波数で、制限および事前定義された周期波形のセットを生成します。

- 任意関数発生器 (AFG) は、関数発生器と同じ機能がありますが、アクセス可能なオンボードメモリを使用して、ユーザ定義波形を追加できるという利点があります。

- 任意波形発生器 (AWG) は、標準波形だけでなく、関数発生器やAFGと比較して、非常に大きなオンボードメモリを使用して大規模で複雑なユーザ定義波形も生成します。

- 信号発生器のビット分解能 (垂直分解能) は、DACが生成できる離散電圧レベルの数を定義します。

- 帯域幅は、信号発生器が出力できる周波数の範囲を表します。帯域幅は、正弦波入力信号が元の振幅の70.7%に減衰する周波数で定義され、-3 dBポイントとしても知られています。

- 減衰は、ダイナミックレンジを犠牲にしたり、デジタルビットの表現力を失うことなく、生成された信号の振幅を変更する手法です。

- デジタルゲインは、波形デジタルデータがDACに到達する前に、そのデータを係数で乗算することを含む手法です。これにより、生成された信号の振幅をほぼ瞬時に変更できるようになります。しかし、DACの最大分解能を使用できない場合があります。

- 補間とアナログフィルタ処理を使用して、有効サンプリングレートを向上させ、DACによって生成された信号の高周波数画像を除去できます。

次のステップ

- 信号発生器の用語と仕様を確認する

- 自動化された特性評価、検証、製造テストのために用いるNI PXI波形発生器の詳細

- 適切なアナログ信号発生器を探す

- NIのオンラインPXIアドバイザを使用してテストシステムを構築