스펙 설명: NI 다기능 I/O (MIO) DAQ

개요

내용

소개

본 가이드는 대부분의 NI 스펙 매뉴얼과 동일한 섹션들로 구성되어 있습니다. 아래 용어 정의는 알파벳 순으로 되어 있으나, 스펙 매뉴얼에는 다른 순서로 정렬되어 있을 수도 있습니다. 본 가이드는 60xx, 61xx, 62xx, 63xx, 64xx MIO DAQ 디바이스 및 모듈에만 적용됩니다. cDAQ 및 cRIO 섀시 및 컨트롤러, 91xx, 92xx, 94xx C 시리즈 모듈, 다기능 RIO 78xx R 시리즈, 디지털 멀티미터, 스코프/디지타이저, 그리고 기타 인스트루먼트와 같은 다른 NI 제품군은 스펙에 대해 다른 용어나 방법이 사용될 수 있습니다. 따라서 본 가이드는 MIO DAQ 제품군이 아닌 디바이스와 모듈에 대한 참조로는 사용할 수 없습니다.

본 가이드에서는 NI 6361 및 NI 6363 디바이스를 참조로 사용합니다. 이들 디바이스의 스펙을 확인하려면 아래 링크를 클릭하십시오. NI 6361 및 NI 6363 스펙.

스펙 용어의 이해

우선, 다양한 스펙 간 카테고리 차이를 확인하는 것이 중요합니다. NI는 테스트 및 측정 인스트루먼트의 기능과 성능을 스펙, 일반 스펙 및 특성 또는 보충 스펙으로 정의합니다. 어떤 스펙이 보증 스펙 또는 일반 스펙인지에 대한 자세한 내용은 해당 디바이스의 스펙 매뉴얼을 참고하십시오.

- 스펙은 기술된 작동 조건 하의 권장 교정 간격 내에서 인스트루먼트의 보증 성능을 나타냅니다.

- 일반 스펙은 기술된 작동 조건 하의 권장 교정 간격 내에서 대다수의 인스트루먼트에 의해 충족되는 스펙입니다. 일반 스펙은 보증되지 않습니다.

- 특성 또는 보충 스펙은 설계 또는 개발 단계에서 설정되었으나 확인 또는 조정 단계에서 평가되지 않은 인스트루먼트의 기본적인 기능과 속성을 설명합니다. 이는 이전 정의에 포함되지 않은 인스트루먼트의 적절한 사용과 관련된 정보를 제공합니다.

아날로그 서브시스템 스펙

NI MIO DAQ 디바이스 및 모듈은 아날로그 입력, 아날로그 출력 또는 두 시스템이 혼합된 형태를 지원합니다. 각 서브시스템에만 적용되는 스펙도 있고, 양쪽에 모두 적용되는 스펙도 있습니다. 본 섹션은 공통 스펙, 아날로그 입력 스펙, 아날로그 출력 스펙의 세 부분으로 구성됩니다.

아날로그 입력 및 아날로그 출력

전체 스케일에서의 절대 정확도

정확도는 정확한 측정 값에 얼마나 가까운지를 나타냅니다. 전체 스케일에서의 절대 정확도는 측정되는 값이 주어진 범위에서 지원되는 최대 전압이라고 가정하여 계산된 이론적 정확도입니다. 어떠한 측정의 정확도는 해당 측정이 변화하면 달라지므로 디바이스 간 비교를 하려면 전체 스케일에서의 정확도를 사용해야 합니다. 전체 스케일에서의 절대 정확도는 25 °C 작동 온도 등 실제로는 달라질 수 있는 환경 변수에 대한 가정을 합니다.

- 공칭 범위 양의 전체 스케일 — 특정 범위에서 측정할 수 있는 이상적인 최대 양의 값

- 공칭 범위 음의 전체 스케일 — 특정 범위에서 측정할 수 있는 이상적인 최대 음의 값

- 잔류 게인 에러 — 계측 증폭기 고유의 게인 에러이며 자기 교정 후 존재하는 것으로 알려져 있습니다.

- 게인 온도 계수 — 최종 자기 교정 온도와 비교하여 온도가 증폭기의 게인에 미치는 영향을 설명하는 온도 계수

- 잔류 오프셋 에러 — 계측 증폭기 고유의 오프셋 에러이며 자기 교정 후 존재하는 것으로 알려져 있습니다.

- 참조 온도 계수 — 최종 외부 교정 온도와 비교하여 특정 온도에서 측정이 얼마나 정확한지 나타내는 온도 계수

- INL 에러(상대 정확도 분해능) —ADC의 전압 출력에서 이상적인 출력까지의 최대 편차. 최악의 경우의 DNL로 생각할 수 있습니다. 또한 다음을 참조하십시오. DNL

- 오프셋 온도 계수 — 최종 자기 교정 온도와 비교하여 온도가 ADC 변환에서 오프셋에 미치는 영향을 나타내는 온도 계수

- 랜덤/시스템 노이즈 — 입력 채널을 접지하여 측정한 아날로그 프런트 엔드에서 생성된 추가 시스템 노이즈

예

NI PXIe-6363의 범위는 ±0.5 V입니다. 전체 스케일에서의 절대 정확도는 측정되는 신호가 0.5 V인 것으로 가정하여 계산됩니다. ±0.5 V 범위에 대한 전체 스케일의 절대 정확도는 100 µV입니다.

또한 다음을 참조하십시오

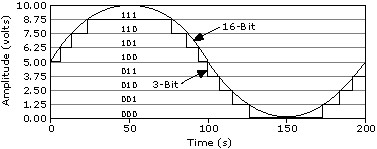

아날로그-디지털 변환기(ADC) 분해능

분해능은 디바이스나 센서가 감지할 수 있는 가장 작은 입력 신호 변화입니다. 아날로그 신호를 나타내는 데 사용되는 비트 개수가 ADC의 분해능을 결정합니다.

예

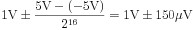

NI PXIe-6363은 16비트 디바이스이므로 ±5 V 범위에서 감지할 수 있는 최소 진폭 변화는 0.152 mV입니다. ±0.1 V 범위에서 이 값은 3.05 µV입니다.

공통 모드 제거율 (CMRR)

증폭기의 양의 출력과 음의 출력에서 동일한 신호가 관찰될 때 CMRR은 최종 출력으로부터 이 신호가 얼마나 제거되는지를 지정합니다(일반적으로 dB 단위 사용). 이상적인 증폭기는 공통 모드 신호를 100%까지 제거하지만, 구현에서는 도달할 수 없는 제거율입니다.

예

NI PXIe-6363의 CMRR은 100 dB입니다. 즉, 공통 모드 전압을 100,000배 감쇠시킨다는 의미입니다. 측정되는 신호가 5 Vpk 사인파이고 양의 입력과 음의 입력 간 오프셋 또는 공통 전압이 5 VDC인 경우 최종 출력은 5 VDC 입력을 5 µV로 감쇠시키거나 제거합니다. CMRR은 정확도 도출에 포함되지 않으며, 측정된 신호에 공통 모드 전압이 포함된 경우, 별도로 고려해야 합니다.

변환 간격

다중 채널 측정에서 채널 간에 필요한 안정화 시간.

예

PCI-6221은 사용자가 요구하는 정확도 수준에 따라 변환 간격이 4~7 µs입니다.

또한 다음을 참조하십시오

커플링

인터페이스의 한쪽에서 다른 한쪽으로 전달되는 신호 유형을 정의하는 두 회로의 인터페이스 속성입니다. 일반적으로 두 가지 옵션이 있습니다.

- DC 커플링: AC 및 DC 신호를 모두 전달합니다

- AC 커플링: AC 신호만 전달하므로, 신호의 DC 오프셋을 제거하는 하드웨어를 구현합니다

디바이스에 따라 소프트웨어로 선택 가능한 커플링을 지원하거나 AC 또는 DC 커플링 중 하나만 지원합니다.

예

NI PXIe-6363은 아날로그 입력과 아날로그 출력 모두에 대해 DC 커플링을 지원합니다. AC 커플링은 어떤 쪽에 대해서도 지원되지 않습니다.

또한 다음을 참조하십시오

누화(crosstalk)

한 채널의 신호가 인접 채널에 커플링되거나 영향을 줄 수 있는 정도를 측정합니다. 누화는 진폭 변화 신호가 다른 와이어 또는 PCB 트레이스에 물리적으로 가까운 와이어 또는 PCB 트레이스에 존재할 때마다 발생합니다.

예

NI PXIe-6363은 인접 채널의 경우 -75 dB, 인접하지 않은 채널의 경우 -95 dB의 누화 스펙을 갖습니다. 이는 채널 ai2가 채널 ai1과 ai3 사이에 -75 dB의 누화 스펙을, 다른 모든 ai 채널에 대해 -95 dB의 누화 스펙을 가짐을 의미합니다.

데이터 전송 메커니즘

NI 디바이스는 데이터를 디바이스에서 컴퓨터로(입력의 경우), 컴퓨터에서 디바이스로(출력의 경우) 양방향 전송합니다. 버스(USB, PXI Express 등)에 따라 다른 데이터 전송 메커니즘이 사용됩니다. 일부 버스는 여러 전송 메커니즘을 지원할 수 있습니다. 특정 메커니즘에 대한 자세한 내용은 NI-DAQmx 도움말 문서를 참조하십시오.

예

USB-6341은 USB 벌크(신호 스트림) 및 프로그래밍된 I/O 데이터 전송을 지원합니다. NI PXIe-6363은 직접 메모리 액세스(DMA) 및 프로그래밍된 I/O를 지원합니다.

또한 다음을 참조하십시오

차동 비선형성(DNL)

DAC의 이상적인 단계 크기(단계 크기 계산 방법은 디지털―아날로그 변환기(DAC) 분해능 참조)와 출력되는 실제 값(일반적으로 LSB 단위 사용)의 차이입니다. 이상적인 DAC에서 DNL은 0 LSB입니다.

예

NI PXIe-6363의 DNL은 ±1 LSB입니다. 즉, DAC에서 출력되는 모든 값의 실제 값은 프로그래밍된 값에서 ±1 LSB만큼 차이가 날 수 있습니다. 예를 들어, 사용자가 ±5 V 범위에서 1 V의 값을 출력하도록 DAC를 프로그래밍하는 경우 출력 범위 (정확도의 영향을 포함하지 않음)는 다음과 같습니다.

INL은 DNL의 복합 효과이므로 INL 스펙은 정확도 계산에 자주 사용됩니다. NI PXIe-6363의 경우, 정확도 테이블의 INL 스펙은 사용된 범위의 64 ppm 또는 4 LSB입니다.

디지털―아날로그 변환기(DAC) 분해능

디지털 값에서 변환할 때 아날로그 신호를 나타내는 비트 수입니다.

예

NI PXIe-6363은 16비트 DAC를 사용하므로 ±5 V, ±10 V 또는 공급된 사용자 전압 사이에서 216개의 이산값이 출력될 수 있습니다.

또한 다음을 참조하십시오

FIFO 크기 (아날로그)

NI DAQ 디바이스는 아날로그 입력 또는 아날로그 출력 작업을 수행할 때 온보드 FIFO에 데이터를 저장할 수 있습니다.

- 입력 작업의 경우, 이 FIFO는 NI-DAQmx 드라이버 소프트웨어가 데이터를 PC 버퍼라고 하는 RAM의 사전 할당된 위치로 전송하기 전에 데이터를 버퍼링하는 데 사용됩니다.

- 출력 작업의 경우, 사용자가 생성하도록 요청한 데이터는 FIFO와 PC 버퍼의 조합으로 버퍼링될 수 있습니다.

입력 및 출력 채널이 있는 디바이스에는 각 서브시스템에 대한 전용 FIFO가 있습니다. 그러나 FIFO는 해당 FIFO 내의 모든 채널에서 공유됩니다. 아날로그 입력의 경우, NI-DAQmx는 FIFO에 저장된 데이터가 PC 버퍼로 빠르게 전송되어 온보드 FIFO가 오버런되지 않도록 데이터 전송 메커니즘을 구현합니다. 아날로그 출력의 경우, NI-DAQmx는 PC 버퍼의 데이터가 온보드 FIFO로 빠르게 전송되어 FIFO가 언더런되지 않도록 데이터 전송 메커니즘을 구현합니다. 아날로그 출력의 경우, PC 버퍼 사용 여부를 지정하고 온보드 FIFO에서 단일 웨이브폼을 재생성하기 위해 사용자가 선택할 수 있는 속성이 있습니다.

예

NI PXIe-6363의 입력 FIFO는 2,047개 샘플입니다. 이는 1,024 S/ch/s의 속도로 데이터를 수집하는 4개의 채널을 사용하는 입력 작업이 0.5초 이내에 온보드 FIFO를 오버런한다는 것을 의미합니다.

NI-DAQmx는 오버런을 피하기 위해 DMA를 사용하여 FIFO에서 버퍼라고 하는 온보드 컴퓨터 메모리로 데이터를 전송합니다.

또한 다음을 참조하십시오

NI-DAQmx에서 데이터 전송 요청 조건 프로퍼티 설정하기

웨이브폼 수집 (DI) FIFO

웨이브폼 생성 (DO) FIFO

입력 바이어스 전류

유한한 입력 임피던스를 갖고 있어 디바이스가 소량의 전류로도 신호를 감지할 수 있습니다. 이론적으로 이 값은 0 A여야하지만 실제로는 불가능합니다.

예

NI PXIe-6363의 입력 바이어스 전류는 ±100 pA입니다. 즉, NI PXIe-6363으로 측정되는 모든 센서가 정확히 디지털화되려면, 전체 전압 출력 범위에서 최소한 그 만큼의 전류를 공급할 수 있어야 합니다.

과전압 상태 중 입력 전류

디바이스가 과전압 상태에 있을 때 이것은 디바이스가 싱킹할 지정된 전류량입니다.

예

NI PXIe-6363은 과전압 상태에서 핀당 최대 ±20 mA를 싱킹합니다. 이 값을 초과하면 중요한 구성 요소가 손상될 수 있습니다.

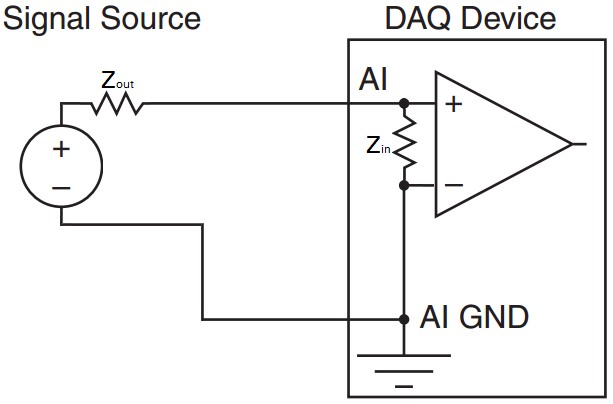

입력 임피던스

입력 임피던스는 입력 회로가 전류가 아날로그 입력 접지로 흐르는 것을 방해하는 값을 측정한 것입니다. 이상적인 ADC의 경우 이 값이 무한하며 따라서 입력에서 접지로 전류가 흐르지 않습니다. 그러나 실제로는 불가능합니다. 입력 임피던스가 유한하다는 것은 ADC가 회로, 특히 출력 임피던스가 큰 회로를 어느 정도 로드다운한다는 것을 의미합니다. 센서의 출력 임피던스가 낮은 것이 일반적입니다.

예

NI PXIe-6363의 입력 임피던스는 > 10 GΩ에서 Z입니다. 최저 입력 임피던스의 최악의 시나리오를 취할 경우, 출력 임피던스 Zout = 150 Ω인 센서를 가정하면 단일 종단 측정을 다음의 단순화된 회로로 볼 수 있습니다.

센서 출력과 DAQ 디바이스 입력의 직렬 조합은 전압이 두 개의 임피던스 값으로 나누어지고 이 중 더 큰 임피던스가 전압의 대부분을 지니게 되는 것을 의미합니다. 이는 이 센서의 감도가 20 °C/V이고 100 °C (5 V 출력)를 측정하는 경우 DAQ 디바이스에 의해 측정된 전압은 출력 전압에 DAQ 입력 및 센서 출력 임피던스의 합에 대한 입력 임피던스의 비율을 곱한 값임을 의미합니다.

이 75 nV의 측정값 차이는 임피던스로 인한 무시할 수 있는 05 °C의 측정 에러에 해당합니다.

입력 임피던스가 중요한 스펙이 되는 예로서, 센서의 출력 임피던스가 5 GΩ과 같이 매우 높은 가상의 경우를 가정해 보십시오. 매우 높은 출력 임피던스를 가진 이 DAQ 디바이스를 센서에 연결하면 센서의 5 V 공칭 출력이 3.33 V로 읽히거나 33.4 °C의 가설 측정 에러가 발생합니다.

최대 업데이트 속도

아날로그 출력의 경우, 업데이트 속도는 초당 DAC 대 아날로그 전압 또는 전류 값의 샘플 수를 지정합니다. 대부분의 NI 디바이스에는 아날로그 출력 채널당 하나의 DAC가 있지만 모두 아날로그 출력 데이터가 저장되는 FIFO를 공유합니다. 이 FIFO에서 데이터를 읽고 보드의 다른 DAC로 전송할 수 있는 속도로 인해, 동일한 디바이스에서 여러 AO 채널을 사용할 때 업데이트 속도가 제한되는 경우가 있습니다. 업데이트 속도는 단일 채널에서 출력할 때 초당 샘플 수(S/s) 또는 다중 채널에서 출력할 때 초당 샘플 수(S/s/ch)로 측정됩니다.

아날로그 입력에 대해서는 샘플 속도를 참조하십시오.

예

NI PXIe-6363에는 4개의 아날로그 출력 채널이 있습니다.

- 단일 채널을 사용하는 경우, 해당 채널의 업데이트 속도는 2.86 MS/s입니다.

- 3개의 아날로그 출력 채널을 사용하는 경우, 최대 업데이트 속도는 1.54 MS/s/ch입니다. FIFO에서 데이터를 읽고 다양한 DAC로 전송할 수 있는 속도는 더 많은 채널이 스캔 리스트에 추가될 때 업데이트 속도를 점진적으로 제한합니다.

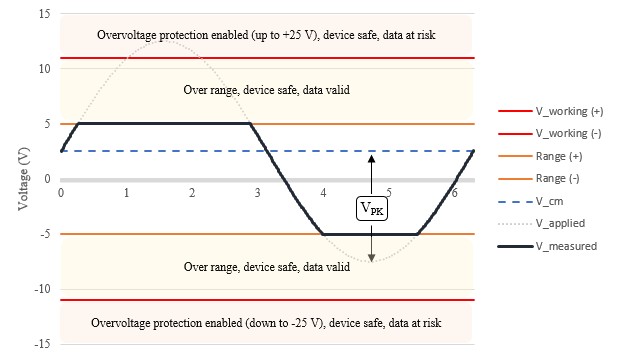

최대 작동 전압

최대 작동 전압은 다른 채널의 데이터 유효성이 문제가 되기 전까지 디바이스가 모든 아날로그 입력 채널에서 허용할 수 있는 총 전압 레벨을 지정합니다. AI GND와 관련하여 다른 채널에서의 정확도를 보장하기 위해서는 측정할 신호와 공통 모드 전압의 조합이 최대 작동 전압 스펙을 초과해서는 안 됩니다. 최대 작동 전압은 디바이스의 입력 범위와 무관합니다.

예

2.5 VDC 공통 모드의 10 Vpk 사인파는 PXIe-6363에서 측정되며, 아래에서 볼 수 있듯이 최대 작동 전압은 ±11 V입니다.

두 신호의 조합은 +12.5 V에서 피크이며 최대 작동 전압을 초과합니다. 최대 작동 전압을 초과하면 멀티플렉서의 과도한 충전으로 인해 안정화에 필요한 시간이 부족해 다른 멀티플렉싱된 채널의 데이터 유효성이 손상될 수 있습니다.

또한 다음을 참조하십시오

단조성(monotonicity)

단조성은 DAC 코드가 증가할 때 출력 전압도 증가하는 것을 보장합니다.

예

NI PXIe-6363은 DAC 코드가 증가할 때 출력 전압도 증가하는 것을 보장합니다. 예를 들어, 램프 기능은 램프의 방향에 따라 항상 증가하거나 감소합니다.

출력 전류 드라이브

아날로그 출력의 경우, 출력 전류 드라이브는 디바이스가 싱킹하거나 소싱할 수 있는 최대 전류량입니다. 프로그래밍된 전압과 결합된 출력 임피던스를 포함하여 연결된 부하는 프로그래밍된 출력 전압을 유지하는 데 필요한 전류를 결정합니다.

전류 드라이브가 지정된 출력 전류 드라이브 아래로 유지되면 프로그래밍된 출력 전압이 보장됩니다. 출력 전류 드라이브를 초과하면 디바이스가 오버드라이브 상태가 되어 출력 전압이 더 이상 보장되지 않습니다.

예

NI PXIe-6363은 모든 아날로그 출력 채널에서 ±5 mA를 구동할 수 있습니다. ±10 V 범위에서 이는 전체 스케일로 구동할 수 있는 가장 낮은 총 임피던스가 가장 높은 전력 출력, 즉 가장 큰 전류 및 전압에서 결정됨을 의미합니다.

PXIe-6363의 출력 임피던스를 고려할 때, 전체 스케일로 구동할 수 있는 가장 낮은 연결 임피던스는 최소 부하와 출력 임피던스의 차이입니다.

또한 다음을 참조하십시오

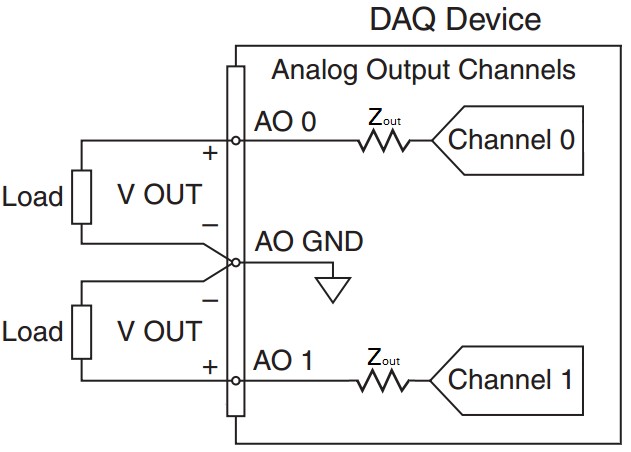

출력 임피던스

출력 임피던스는 아래 그림과 같이 아날로그 출력 채널과 효과적으로 직렬 연결된 임피던스입니다.

낮은 출력 임피던스는 생성된 더 많은 전압이 아날로그 출력의 부하에서 떨어질 수 있도록 합니다. 원하는 전압 레벨이 달성되도록 하려면 출력 임피던스를 고려하는 것이 중요합니다.

예

NI PXIe-6363의 출력 임피던스는 0.2 Ω입니다. 이는 연결된 부하의 임피던스가 500 Ω이고 사용자가 지정한 전압이 1 V인 경우 부하의 실제 전압은 예상보다 낮은 0.9996 V 또는 0.4 mV임을 의미합니다. 이 전압에서 디바이스로부터 1.99 mA의 전류도 인출됩니다.

오버드라이브(단락 회로) 전류

출력 및 부하 임피던스의 조합이 너무 낮아서 출력 전류 드라이브에 의해 지정된 것보다 더 많은 전류가 디바이스에서 인출되면 디바이스는 오버드라이브 상태가 됩니다. 오버드라이브 또는 단락 회로 전류는 드라이브가 손상없이 공급할 수 있는 최대 전류량입니다. 이 오버드라이브 상태에서는 전류 인출이 증가함에 따라 전압이 떨어집니다.

오버드라이브 전류를 초과하면 디바이스가 손상될 수 있습니다. 디바이스 손상을 방지하기 위해 항상 출력 전류 드라이브 스펙 내에서 디바이스를 사용하는 것이 좋습니다.

예

NI 6363의 오버드라이브 전류 스펙은 26 mA입니다. 단락 등의 경우 이 값을 초과하면 디바이스가 손상될 수 있습니다.

또한 다음을 참조하십시오

오버드라이브 보호

아날로그 출력의 경우, 오버드라이브 보호는 디바이스 손상이 발생하기 전까지 채널에서 허용되는 최대 전압입니다. 이 스펙은 우발적인 역구동 전압의 경우에 프로그래밍할 수 있는 실제 전압보다 높은 것입니다.

예

NI PXIe-6363은 각 아날로그 출력 채널에서 개별적으로 최대 ±25 V까지 보호됩니다. 이는 AO GND에 대한 핀의 전압이 ±25 V 내에 있는 한, 프로그래밍된 출력 전압에 관계없이 디바이스에 손상이 발생하지 않음을 의미합니다. 이 값을 초과하면 디바이스가 손상될 수 있습니다.

과전압 보호

아날로그 입력 회로에는 PGIA 또는 ADC와 같은 디바이스의 가장 중요한 컴포넌트를 손상시키지 않도록 대전압을 차단하는 보호 다이오드가 있습니다.

- 디바이스의 전원을 켜면 이러한 다이오드는 양의 전압과 음의 전압으로 바이어스됩니다. 즉, 다이오드에 과부하가 걸리고 손상이 발생하려면 바이어스와 역방향 전압의 합보다 큰 전압이 존재해야 합니다.

- 디바이스가 꺼지면 바이어스 전압이 제거되므로 다이오드를 반전시키는 데 필요한 전압이 낮아져 디바이스가 손상되기 쉽습니다.

과전압 상태에서 디바이스가 싱킹할 수 있는 최대 전류량은 과전압 상태에서의 입력 전류에 의해 지정됩니다.

예

NI PXIe-6363은 2개의 AI 핀에 대해 최대 ±25 V까지 보호합니다. 2개를 초과하는 AI 핀에 ±25 V보다 큰 과전압이 발생하면 디바이스가 손상될 수 있습니다. 디바이스가 꺼져 있는 경우, 보호 레벨은 ±15 V로 낮아집니다.

전원이 켜진 상태

전원 켜짐 상태는 디바이스의 전원이 켜졌을 때와 전원 켜짐/꺼짐 글리치라고 하는 글리치 기간 경과 후에 아날로그 출력 채널의 값을 지정합니다. 디바이스가 버스에서 전력을 받기 전 출력의 값은 전원 켜짐 글리치 스펙에 설명되어 있습니다.

예

NI PXIe-6363은 전원을 켤 때 아날로그 출력 채널에서 ±5 mV를 가집니다.

전원 켜짐/꺼짐 글리치

디바이스에서 전원을 인가하거나 제거할 때 아날로그 출력 채널에 글리치 신호가 있습니다.

- 글리치 에너지 크기 — 글리치 기간 동안 글리치 신호가 도달하는 피크 진폭

- 글리치 에너지 지속 시간 — 글리치 신호가 전원 켜짐 상태에서 가라앉는 시간

예

NI PXIe-6363에는 200ms 동안 지정된 글리치 1.5 Vpk가 있습니다. NI USB-6363에는 1.2초 동안 지정된 글리치 1.5 Vpk가 있습니다. USB 디바이스의 글리치 기간은 펌웨어 업데이트 및 USB 호스트 성능으로 인해 지정된 시간보다 길 수 있습니다.

범위(입력 또는 출력)

아날로그 입력의 경우, 이는 보장된 정확도로 측정할 수 있는 최대 양의 값 및 음의 값입니다. 아날로그 출력의 경우, 이는 생성 가능한 최대 양의 값 또는 음의 값입니다. 일부 디바이스에는 낮은 수준의 신호에서 더 높은 분해능을 제공하는 데 사용할 수 있는 여러 입력 또는 출력 범위가 있습니다.

예

NI PXIe-6363에는 4개의 입력 전압 범위가 있습니다: ± 0.1V, ± 0.2V, ± 0.5V, ± 1V, ± 2V, ± 5V, ± 10V. 또한, 1개의 출력 범위가 있습니다: ± 10V.

또한 다음을 참조하십시오

샘플 속도

샘플 속도는 ADC가 데이터를 아날로그에서 디지털 값으로 변환하는 빈도를 지정합니다. 일부 디바이스에는 ADC가 하나만 있으므로 샘플 속도는 채널 간에 공유되는 반면, 다른 디바이스에는 채널별 전용 ADC가 있습니다. 여러 채널을 동시에 측정할 때 샘플 속도는 초당 샘플 수(S/s) 또는 채널당 초당 샘플 수(S/s/ch)로 측정됩니다.

- 단일 채널 최대 — 채널 간 공유 샘플 속도의 경우, 단일 채널은 공유 시 허용되는 것보다 더 높은 속도로 데이터를 수집할 수 있습니다.

- 멀티 채널 최대 — 채널 전체에서 샘플 속도를 공유하는 디바이스의 경우, 이는 결합된 모든 채널이 데이터를 수집할 수 있는 최대 속도입니다.

- 최소 — 데이터를 수집할 수 있는 최소 속도

아날로그 출력에 대해서는 최대 업데이트 속도를 참조하십시오.

예

NI PXIe-6363은 멀티플렉싱된 디바이스이므로 아날로그 입력 채널이 단일 ADC로 멀티플렉싱됩니다. 단일 아날로그 입력 채널은 초당 최대 2백만 개의 샘플(2 MS/s)까지 아날로그 신호를 샘플링할 수 있습니다. 여러 채널을 사용하는 경우, 모든 채널의 결합 속도는 1 MS/s 미만이어야 합니다(2채널은 500 kS/s/ch에서 샘플링 가능, 4채널은 250 kS/s/ch에서 샘플링 가능). 이 디바이스의 최소 샘플 속도는 없습니다.

스캔 리스트 메모리

작업에서 스캔된 채널 수는 스캔 리스트 메모리로 지정됩니다. 아날로그 입력 작업에는 스캔 리스트라는 시퀀스로 많은 가상 채널이 포함될 수 있습니다. 스캔 리스트는 동일한 물리 채널을 여러 번 포함할 수 있으며, 샘플은 임의의 순서로 채취될 수 있습니다. 작업이 커밋되면 이 스캔 리스트가 일시적으로 DAQ 디바이스에 프로그래밍됩니다.

예

NI PXIe-6363에는 4,095개의 스캔 리스트 메모리가 있습니다. 즉, 모든 물리적 채널이 단일 작업에 포함되어 있을 때 한 번의 스캔 또는 한 번의 샘플 클럭 틱으로 최대 4,095개의 물리적 채널을 읽을 수 있습니다. 그러나 다중 채널 측정(일부 디바이스의 경우 변환 간격이라고도 함)에 대한 안정화 시간을 고려하면 샘플 클럭 속도가 최대 약 250 Hz로 제한됩니다.

안정화 시간

아날로그 출력 값이 특정 정밀도 내에서 안정화되는 데 걸리는 시간입니다.

예

NI PXIe-6363은 전체 스케일 단계의 안정화 시간을 1 LSB 또는 15 ppm 내에서 2 µs로 설정합니다. 따라서 ±5 V 범위(-5V, 5V, -5V, 5V 등)에서 전체 스케일 오실레이션의 경우 1 LSB 내에서 구동할 수 있는 최대 주파수는 1/(2 µs) = 500kHz입니다.

다중 채널 측정에 대한 안정화 시간

다중 채널 수집을 수행할 때 ADC가 각 채널에 연결되어야 하는 시간입니다.

예

±10 V 범위에서 NI PXIe-6363의 데이터를 수집할 때, 멀티플렉서는 NI-PGIA (Programmable Gain Instrumentation Amplifier)가 전체 스케일 단계 입력이 제공되었을 때 실제 값의 1 LSB (Least Significant Bit) 내에 안정되기 위해 최대 1.5 µs 동안 단일 채널에 있어야 합니다.

슬루 속도(slew rate)

슬루 속도는 디바이스에서 아날로그 출력 채널의 변화율을 지정합니다. 일반적으로 V/µs 단위로 측정됩니다. 출력에 대한 안정화 시간은 계산에 이미 포함된 슬루 시간으로 계산됩니다. 진폭이 큰 스윙은 디바이스에 대한 슬루 속도를 초과할 수 있으므로, 고주파 신호용 시스템을 설계할 때 슬루 속도를 고려해야 합니다.

예

NI PXIe-6363의 일반적인 슬루 속도는 20 V/µs이므로 생성할 수 있는 전체 스케일의 고주파수는 1 MHz입니다. 더 높은 진폭으로 전체 스케일 신호를 출력하려고 하면, 예기치 못한 왜곡이 발생할 수 있습니다.

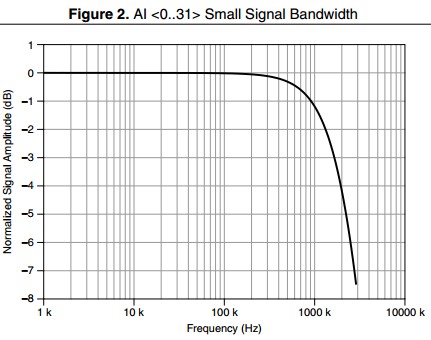

소신호 대역폭

감쇠가 –3 dB 미만으로 전달되는 주파수 범위. 소신호 대역폭에 대한 테스트는 저전압 신호로 수행됩니다. 그래야 슬루 속도 왜곡이 발생하지 않습니다.

예

NI PXIe-6363은 다음과 같이 1.7 MHz의 소신호 대역폭을 갖습니다.

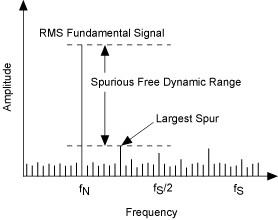

SFDR (Spurious-Free Dynamic Range)

스퓨리어스 없는 다이내믹 레인지는 스퓨리어스 노이즈가 기본 신호를 방해하거나 왜곡하기 전에 사용 가능한 다이내믹 레인지입니다. 아날로그 입력 및 아날로그 출력 회로에는 모두 비선형성이 있어 하모닉 왜곡이 발생합니다. SFDR은 주파수 영역에서 다음과 같이 쉽게 관찰할 수 있습니다.

예

PCI-6133의 SFDR은 약 95 dB입니다. 아래의 그래프를 예로 들면, 기본 신호가 0 dB로 적용된 경우 다음 최고 스퍼는 95 dB 더 낮아져 스퓨리어스 간섭 없이 가용 다이내믹레인지를 제공합니다.

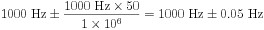

타이밍 정확도

타이밍 신호를 위해 NI DAQ 디바이스에서 클럭 신호를 생성할 때, 생성된 실제 주파수는 타이밍 정확도 내에 있습니다. 이 스펙은 온보드 수정 오실레이터의 전체 정확도에서 파생됩니다. 타이밍 정확도는 일반적으로 백만 분의 일(ppm) 단위로 측정됩니다. 이 정확도 값을 Hz로 변환하려면 정확도 값을 백만으로 나눈 값을 곱하십시오. 클럭의 주파수는 사이클별로 크게 달라지지 않을 것입니다.

예

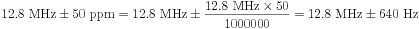

PXIe-6363의 타이밍 정확도는 50 ppm입니다. 업데이트 속도가 1,000 S/s 인 아날로그 출력 작업의 경우, 샘플 클럭은 1,000 Hz ± 50 ppm에서 실행됩니다. Hz에서 이것은 다음과 같습니다.

타이밍 분해능

온보드 타이밍 엔진을 사용할 때 아날로그 입력 및 출력 작업의 샘플 및 업데이트 속도가 이산 값으로 제한됩니다. 인접한 두 속도 사이의 클럭 주기 차이를 타이밍 분해능이라고 합니다. NI-DAQmx는 사용자가 지정한 정확한 주파수를 생성할 수 없는 경우 선택한 주파수를 사용 가능한 다음 주파수까지 강제 변환합니다.

예

NI PXIe-6363의 지정된 타이밍 분해능은 10 ns입니다. 즉, 10 ns의 정수 배수로 데이터를 생성하거나 수집할 수 있습니다. 예를 들어, 32,000.00 Hz 및 32,010.2432 ... 클럭 주기가 각각 31.250 µs 및 31.240 µs이므로 Hz는 인접한 두 주파수입니다. 사용 가능한 다음 주파수를 찾으려면 알려진 클럭 주기에 타이밍 분해능을 더하거나 빼십시오.

전체 하모닉 왜곡(THD)

ADC 및 DAC 컴포넌트의 고유한 비선형성으로 인해, 측정 또는 생성된 신호에 하모닉 주파수가 나타납니다. 기본 전력에 대한 이러한 하모닉 전력의 합의 비율을 총 하모닉 왜곡이라고합니다.

예

PCI-6133의 지정된 THD는 약 -101 dB입니다. 이는 주어진 테스트 신호에 대해, 이 경우 전체 스케일에서 10 kHz 사인파에 대해, 하모닉 왜곡으로 인한 신호의 전력이 0.001 % 미만임을 의미합니다. 반대로, 측정되는 전력의 99.999% 이상이 기본 톤 또는 관심 신호에 기인할 수 있습니다.

디지털 서브시스템 스펙

NI MIO DAQ 디바이스 및 모듈은 디지털 입력, 디지털 출력 또는 두 시스템이 혼합된 형태를 지원합니다. 또한 PFI (Programmable Function Interface) 라인을 지원하여 백플레인을 통해 디지털 신호를 라우팅할 수 있습니다. 다음은 일반 스펙, 정의 및 해당 스펙이 실제 환경에서 사용되는 방법의 목록입니다.

DI 샘플 클럭 주파수

디지털 웨이브폼 데이터를 수집하는 속도를 결정합니다. 이 스펙은 디바이스가 USB 기반인지 아니면 PCI 기반인지(PCI, PCI Express, PXI 및 PXI Express 포함)에 따라 다릅니다. 일반적으로 PCI 기반 디바이스는 버스의 높은 처리량, 짧은 대기 시간, 그리고 DMA (직접 메모리 액세스) 데이터 전송의 구현으로 인해 더 높은 디지털 웨이브폼 전송 속도를 허용합니다.

예

NI 6363은 세 가지 폼 팩터로 제공됩니다: USB, PCI Express, PXI Express.

- USB - 샘플 클럭 주파수는 버스에서 다른 디바이스의 활동에 따라 0에서 1 MHz 사이입니다. 예를 들어, 이 디바이스와 동일한 USB 허브에 연결된 USB 외장 하드 드라이브에 데이터를 기록하는 경우, 1 MHz의 수집 속도에 미치지 못할 수 있습니다. 최대 성능을 얻기 위해서는 USB 루트 허브에 USB DAQ 디바이스 이외의 다른 디바이스는 연결하지 않을 것을 권장합니다.

- PCI Express 및 PXI Express - 샘플 클럭 주파수는 버스에서 다른 디바이스의 활동에 따라 0에서 10 MHz 사이입니다. 예를 들어, 수집하는 동안 병렬 처리를 위해 대량의 데이터가 GPU로 전송되는 경우, 전체 10 MHz의 수집 속도에 미지치 못할 수 있습니다. 최대 성능을 얻기 위해 PCI Express 또는 PXI Express 디바이스가 다른 디바이스와 동일한 스위치에 있을 때 모든 디바이스가 같은 방향으로 데이터를 전송하는 것을 권장합니다.

DO 샘플 클럭 주파수

대부분의 NI 디바이스에서 포트 0의 디지털 웨이브폼 데이터를 출력할 수 있는 속도를 결정합니다. 이 스펙은 디바이스가 USB 기반인지 아니면 PCI 기반인지(PCI, PCI Express, PXI 및 PXI Express 포함), 그리고 데이터가 어디에서 오는지에 따라 다릅니다.

- FIFO에서 재생성 - 사용자가 디바이스에 데이터를 한 번 쓰면, 디바이스에서 데이터가 재생성됩니다. 이 방법은 버스 트래픽 문제를 없애고 더 높은 출력 속도를 제공합니다.

- 메모리에서 스트리밍 - 디바이스는 데이터를 재생성하지 않으므로 언더플로우 에러를 피하기 위해서는 항상 사용자의 어플리케이션에서 사용 가능한 새 데이터가 있어야 합니다. 이 방법을 사용하면 버스를 통해 지속적인 통신이 이루어지므로 처리 속도가 낮은 버스에서는 업데이트 속도가 더 제한됩니다.

예

NI 6363은 세 가지 폼 팩터로 제공됩니다: USB, PCI Express, PXI Express.

- USB - PCI Express나 PXI Express에 비해 처리량이 적고 대기 시간이 긴 버스입니다. FIFO에서 출력 웨이브폼을 재생성할 때 최대 업데이트 속도 10 MHz를 실현할 수 있습니다. 메모리에서 스트리밍할 때는 USB를 통해 데이터를 스트리밍해야 하므로 더 느린 최대 속도 1 MHz가 지정됩니다.

- PCI Express 및 PXI Express - 이 버스는 더 빠르고 더 높은 처리량을 유지하여 지정된 10 MHz의 최대 업데이트 속도를 제공합니다.

디바운스 필터 셋팅

디지털 라인은 상태를 변경할 때(로우-하이 또는 하이-로우) 가끔씩 새로운 상태가 안정화되기 전에 두 상태 사이에 바운스가 발생합니다. 이러한 바운스를 무시하고 안정화된 후에 값을 읽도록 디바운스 필터를 구현할 수 있습니다. 정적 디지털 입력 라인(PFI/Port 1/Port 2)의 경우 디지털 디바운스 필터는 푸시 버튼과 같은 물리적 인터페이스에서 자주 나오는 종류와 같은 노이즈나 글리치가 있는 신호를 디바운스하는 데 사용됩니다. 이 필터는 디지털 라인 필터와 달리 모든 필터 길이에 대해 사용자 정의가 가능합니다.

예

PXIe-6363은 필터에 90 ns, 5.12 µs, 2.56 ms 또는 사용자 정의 간격 타이밍을 허용합니다. 또한 입력 라인마다 선택 가능할 뿐만 아니라 프로그래밍 가능한 하이/로우 전이도 지원합니다. 이 필터 시간은 PXIe-6363의 온보드 오실레이터에서 파생됩니다.

델타 VT 히스테리시스 (VT+ - VT-)

히스테리시스는 값의 증가 또는 감소에 따라 다른 전이 임계값을 갖는 프로퍼티입니다. 이 경우 관찰된 전이는 하이에서 불확정 상태로, 그리고 로우에서 불확정 상태로의 전이입니다. 양의 방향 임계값과 음의 방향 임계값 사이의 차이는 전압 임계값 히스테리시스입니다. 이 스펙은 불확정 상태로 재진입하기 전에 전압 레벨이 임계 하한값 또는 상한값을 초과할 수 있는 정도를 나타냅니다.

예

NI PXIe-6363은 최소 0.2 V의 히스테리시스를 지정합니다. 이는 신호가 0 V에서 5 V로 전이되는 경우 로직 레벨이 낮게 간주되기 전에 VT+ 값보다 최대 0.2 V 아래로 떨어질 수 있음을 의미합니다. 이 변동 기간 동안 값은 불확정 상태를 통과합니다.

디지털 라인 필터

포트 0의 모든 라인에서 라인 필터가 활성화된 경우, 해당 라인은 지정된 필터 시간 동안 안정적인 로직 레벨을 유지해야만 해당 로직 레벨로 등록될 수 있습니다. 긴 케이블을 통해 또는 시끄러운 환경에서 디지털 데이터를 전송하는 데 유용한 도구입니다. 일반적으로 소프트웨어에서는 여러 필터 시간을 선택할 수 있습니다(짧은 필터, 중간 필터, 긴 필터 등). 시스템의 노이즈 특성에 따라 이러한 필터 시간 중 하나가 어플리케이션에 적합할 수 있습니다.

예

PXIe-6363에는 3개의 내장 디지털 라인 필터 시간이 있습니다: 160 ns, 10.24 µs, 5.12 ms. 이 필터는 포트 0의 라인에만 적용됩니다. 포트 1 및 2, PFI 라인 또는 PXI용 라인의 필터링 옵션은 디바운스 필터 셋팅을 참조하십시오.

방향 컨트롤

디지털 또는 PFI 라인을 입력 또는 출력 라인으로 구성할 수 있는지 여부를 결정합니다.

예

PXIe-6361을 사용하면 각 디지털 또는 PFI 라인을 입력 또는 출력으로 구성할 수 있습니다.

접지 참조(디지털)

디지털 신호가 측정되거나 생성될 참조점을 지정합니다. 예를 들어, 로직 하이 디지털 출력은 출력 핀과 지정된 접지 참조 사이에서 5 볼트를 측정할 수 있습니다.

예

PXIe-6361은 디지털 접지(D GND) 신호를 디지털 입력, 디지털 출력 및 PFI 라인 신호의 접지 참조로 사용합니다. 서로 다른 레벨과 주파수의 믹싱 신호로 인한 간섭을 피하기 위해 디지털 접지는 아날로그 접지와 분리됩니다. 디지털 접지와 아날로그 접지는 모두 섀시 접지로 참조됩니다. 아날로그 및 디지털 접지는 USB 케이블의 쉴드를 통해 컴퓨터의 섀시 접지로 참조되므로 USB 디바이스에 특별한 주의를 기울여야 합니다.

입력 고전류 / 입력 저전류(I IH / I IL )

이상적으로 디바이스의 입력 임피던스는 무한하며 전류가 인출되지 않지만, 실제로는 달성할 수 없습니다. 0 V 또는 5 V의 디지털 값을 읽을 때 NI 디바이스의 디지털 입력 회로에 의해 소량의 전류가 인출됩니다. 고전압 레벨을 측정하는 동안 인출되는 전류량은 입력 고전류이며, 저전압 레벨을 측정하는 동안 인출되는 전류량은 입력 저전류입니다. 측정 중인 디지털 신호에 지정된 전류 값을 견딜 수 있는 기능이 있는지 확인하는 것이 중요합니다.

예

NI PXIe-6363은 Vin = 0 V일 때 최대 10 µA를 소싱하거나 Vin = 5 V일 때 최대 250 µA를 소싱합니다. 이는 모든 디지털 및 PFI 라인에 적용됩니다.

입력 고전압 / 입력 저전압 (VIH / VIL)

로직 하이 또는 로직 로우를 등록하기 위한 입력 신호의 권장 작동 전압 범위입니다. 이 스펙은 사용자가 필요한 신호의 값을 확인하도록 권장 작동 조건을 정의하는 반면, VT + 및 VT-는 디바이스 자체의 스펙입니다.

예

NI PXIe-6363은 낮은 신호 범위로 기록될 전압 입력의 범위를 0 ~ 0.8 V로 지정합니다. 높은 신호의 경우 이 범위는 2.2 ~ 5.25 V입니다. 0 V 미만 및 5.25 V 초과의 경우 디바이스는 과전압 보호 상태가 됩니다. 로우에서 하이로 또는 하이에서 로우로의 변경이 VIH 또는 VIL을 초과할 때까지 등록되지 않는 불확정 범위도 존재합니다.

또한 다음을 참조하십시오

입력 전압 보호(디지털)

개별 디지털 입력 라인에는 정전기 방전(ESD) 및 과전압 조건에 대한 전용 I/O 보호 기능이 있습니다. 디바이스의 추가 안전을 위해 모든 디지털 및 PFI 라인에서 공유되는 두 번째 수준의 보호 기능이 있습니다. 동시에 여러 라인에서 과전압이 발생하면 이 공유 보호 회로에 스트레스가 가해져 디바이스가 손상될 수 있습니다.

예

NI PXIe-6363은 최대 2개의 핀에서 동시에 ±20 V의 입력 전압 보호 기능을 제공합니다. 즉, 각 라인은 개별적으로 최대 ±20 V의 과전압을 안전하게 처리할 수 있지만, 한 번에 2개를 초과하는 라인이 공칭 전압 입력을 초과할 수는 없습니다.

또한 다음을 참조하십시오

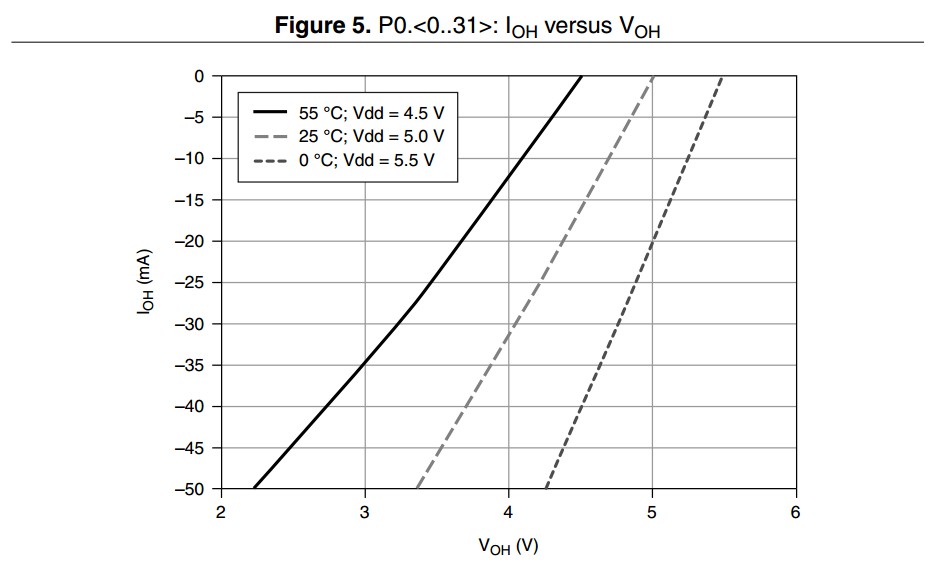

출력 고전류 / 출력 저전류 (I OH / I OL )

높거나 낮은 값을 출력할 때, NI 디바이스의 공칭 전압은 대부분 0 V와 5 V입니다. 그러나 상대적으로 낮은 임피던스 부하가 연결되면 더 높은 전류 요구가 발생하며, 이 공칭 전압은 0 V에서 상승하거나 5 V에서 하강합니다. 이 스펙은 출력 전류와 출력 전압 간의 관계를 나타냅니다.

예

PXIe-6363은 핀에 높은 값이 기록되는지 또는 낮은 값이 기록되는지에 따라 전류를 소싱하거나 싱킹할 수 있습니다. 포트 0의 경우, 전류 소싱 및 싱킹에 대한 최대 권장 값은 라인 당 24 mA입니다. 전류가 디바이스에서 나가는 경우(소싱) 전류는 -24 mA로 표시됩니다. 전류가 디바이스에 들어가는 경우(싱킹) 전류는 +24 mA로 표시됩니다. 주어진 온도와 출력 전압에서 인출 가능한 전류량의 특성은 아래 그래프를 참조하십시오.

포트/샘플 크기

디지털 웨이브폼을 수집하거나 생성할 때 포트 0의 라인 수는 샘플의 크기를 정의합니다. 버스의 트래픽 양을 제한하기 위해, 샘플에 라인 0에서 7까지의 조합이 포함된 경우 샘플의 크기는 1 바이트입니다. 마찬가지로 샘플에 라인 0~15만 포함된 경우 샘플 크기는 2 바이트로 줄어듭니다. 이는 포트의 전체 크기, 포트의 최대 라인 수까지 이어집니다.

예

NI PXIe-6363에는 포트 0에 32개의 라인이 있습니다. 즉, 단일 디지털 샘플의 길이는 최대 32비트(4바이트)입니다.

양의 방향 임계값(VT +) / 음의 방향 임계값(VT-)

디바이스에 로직 신호를 입력할 때 신호가 불확정 범위에서 로직 하이 범위로 변경되는 값을 양의 방향 임계값이라고 합니다. 반대로 음의 방향 임계값은 로직 로우를 등록하기 위해 교차해야 하는 전압 레벨입니다. 양의 방향 임계값은 항상 음의 방향 임계값보다 큽니다. 디지털 상태를 정확하게 등록하려면 신호가 이 두 레벨을 확실히 통과하도록 하는 것이 중요합니다. 이 스펙은 디바이스 자체에 적용되는 반면, 입력 전압 하이 및 로우는 권장 작동 조건에 적용됩니다.

예

NI PXIe-6363의 VT+는 최대 2.2 V이고 VT-는 최소 0.8 V입니다.

또한 다음을 참조하십시오

풀다운/풀업 저항

일부 NI 디바이스는 프로그래밍 방식을 통해 디지털 또는 PFI 라인을 입력, 출력 또는 고임피던스로 구성할 수 있습니다. 풀 저항은 플로팅이 될 수 있는 핀이 접지 또는 전압 소스와 같은 알려진 신호를 참조하도록 하기 위해 사용됩니다. 풀다운 저항은 플로팅 신호를 접지 상태 또는 로직 로우로 풀링하고, 풀업 저항은 플로팅 신호를 로직 하이 전압 값으로 풀링합니다.

예

PXIe-6361은 50 kΩ의 풀다운 저항을 사용하여 능동적으로 하이 또는 로우로 구동되지 않는 터미널이 로우 상태로 플로팅되도록 합니다.

웨이브폼 수집 (DI) FIFO

디지털 웨이브폼 데이터를 읽을 때, FIFO라고 하는 데이터를 버퍼링하는 임시 저장 소자가 디바이스에 내장되어 있습니다. DAQmx는 이 FIFO의 데이터를 PC 버퍼라고 하는 RAM의 메모리 블록으로 복사합니다. 여기에서 LabVIEW와 같은 ADE는 데이터를 어플리케이션 메모리에 복사합니다. 이 FIFO의 크기와 데이터가 저장되는 속도에 따라 DAQmx 드라이버가 오버플로우 조건을 피하기 위해 데이터를 복사하는 빈도가 결정됩니다.

예

NI PXIe-6363은 255개 샘플의 디지털 웨이브폼 수집 FIFO를 가지고 있습니다. 이는 100 kbit/s의 속도로 데이터를 수집하는 경우 DAQmx 드라이버가 PC 버퍼에서 데이터를 전송하지 않으면 온보드 FIFO가 약 2.5 ms 내에 오버플로우된다는 것을 의미합니다.

웨이브폼 생성 (DO) FIFO

FIFO로 알려진 선입선출(first-in-first-out) 데이터 구조에서 데이터 포인트를 버퍼링하는 임시 스토리지 온보드 MIO 디바이스가 있습니다. 이 스토리지는 많은 디바이스가 동일한 USB 루트 허브를 공유하는 경우 버스를 통한 전송이 더 오래 걸리는 USB 디바이스에 특히 유용합니다. 단일 디지털 패턴만 필요한 경우, 버스를 통해 데이터를 여러 번 전송하지 않도록 이 패턴을 이 FIFO에 로드할 수 있습니다. DAQmx API를 사용하여 사용자는 이러한 경우 중 하나에 대해 프로그래밍할 수 있습니다.

예

NI PXIe-6363에는 2,047개 샘플의 디지털 웨이브폼 생성 FIFO가 있습니다. 예를 들어, 100 kbit/s의 데이터 속도로 I2C 통신을 위해 디지털 출력을 사용하는 경우, 전체 FIFO는 20 ms로 출력됩니다. 이는 사용자가 FIFO로 데이터를 계속 스트리밍하기 위해 DAQmx Write를 더 자주 호출해야 한다는 것을 의미합니다. 데이터 속도 테스트를 수행하는 경우, DAQmx API를 사용하여 단일 패턴을 FIFO에 로드하고 PCI Express 버스에서 새 데이터를 작성할 필요없이 다른 데이터 속도로 출력할 수 있습니다.

카운터 스펙

베이스 클럭 정확도(범용 카운터)

내부 베이스 클럭의 정확도는 범용 카운터에서 측정 또는 주파수 생성의 정확도에 직접적인 영향을 줍니다. 이 정확도는 전체 디바이스 타임베이스 정확도에서 상속되므로, 더 높은 정확도의 마스터 타임베이스가 외부에 제공되는 경우 이 클럭의 정확도를 향상시킬 수 있습니다.

예

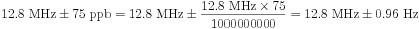

PXIe-6363의 베이스 클럭 정확도는 50 ppm입니다. 사용자가 이 모듈로 12.8 MHz 프리 런 클럭을 생성하려면 다음 계산을 사용하여 정확도를 결정할 수 있습니다.

이 에러는 더 높은 정확도의 외부 베이스 클럭 또는 PXIe-6614와 같은 더 나은 베이스 클럭 정확도를 가진 디바이스를 사용하면 개선될 수 있습니다. PXIe-6614는 최악의 경우 베이스 클럭 정확도가 75 ppb인 온도 변화에 덜 영향을 받는 더 정확하고 안정적인 오븐 제어 수정 오실레이터(OCXO)를 사용합니다. 이 모듈에서 동일한 신호가 생성되는 경우 실제 주파수는 다음과 같습니다.

카운터 분해능

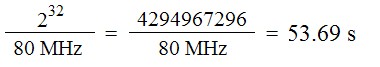

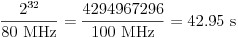

카운터가 숫자를 나타내는 데 사용할 수 있는 비트 수입니다. 범용 카운터가 펄스를 출력하도록 구성된 경우, 펄스가 활성화되는 시간은 카운터의 레지스터 값으로 표시됩니다. 이 값과 카운터가 카운트하는 속도(카운터의 베이스 클럭으로 설정)의 조합은 달성 가능한 최대 펄스 폭을 결정합니다. 마찬가지로 카운터를 사용하여 신호의 펄스 폭을 측정할 때, 등록할 수 있는 최대 펄스 폭은 카운터 베이스 클럭과 카운터의 분해능에 의해 결정됩니다. 신호가 최대 펄스 폭을 초과하면 카운터가 롤오버되고 NI-DAQmx API가 에러를 반환합니다. 따라서, 최대 신호 매개 변수를 계산하는 방법을 알아야 합니다.

분해능이 높은 카운터는 분해능과 측정/생성 길이 간 트레이드오프를 이룰 때 더 많은 유연성을 제공합니다. 이 트레이드오프에 대한 자세한 내용은 아래 그래프를 참조하십시오.

예

PXIe-6614는 카운터 입력 및 카운터 출력 작업에 32비트 카운터를 사용합니다. 카운터 입력 작업이 펄스 폭을 측정하도록 구성된 경우, 최대 카운터 값을 계산하고 카운터의 내부 베이스 클럭 속도로 나누어 측정할 수 있는 최대 펄스 폭을 계산할 수 있습니다. 100 MHz 카운터 베이스 클럭은 10 ns의 정밀도를 허용하므로 이 예에서는 이 베이스 클럭이 선택됩니다.

외부 베이스 클럭 주파수 (범용 카운터)

특정 베이스 클럭 속도가 필요한 경우, 대부분의 NI MIO 디바이스는 외부 베이스 클럭 사용을 허용합니다. 이 클럭은 내부 베이스 클럭과 동일한 목적으로 사용되지만 사용자가 외부에서 제공합니다. 외부 베이스 클럭의 최대 속도는 대역폭 제한 때문에 디바이스의 버스에 따라 달라집니다.

예

NI 6363은 다양한 폼 팩터로 제공되며, 외부 베이스 클럭에 대한 요구사항이 저마다 다릅니다.

- PCI Express 및 USB - 외부 베이스 클럭의 주파수 범위는 0 ~ 25 MHz이며 모든 PFI 라인에 입력됩니다. 최대 주파수에 대한 제한은 PFI 라인의 대역폭 때문입니다.

- PXI Express - PXIe-6363은 PXI Express 섀시의 고급 기능을 활용하고 차동 스타 라인(DSTAR)에서 최대 100 MHz 신호를 허용합니다.

FIFO(범용 카운터)

온보드 MIO 디바이스의 선입선출(FIFO) 메모리 소자는 입력 또는 출력 어플리케이션의 데이터 샘플을 버퍼링하는 데 사용됩니다. 카운터 입력 어플리케이션의 경우, DAQmx가 자동으로 데이터를 사전 할당된 PC RAM 블록으로 전송하기 전에 특정 간격의 카운터 값과 같은 데이터 포인트가 FIFO에 저장됩니다. FIFO는 카운터 출력 어플리케이션에서 듀티 사이클 시퀀스와 주파수 값을 저장하여 생성되는 웨이브폼의 모양을 변경하는 데 사용됩니다. 더 큰 FIFO는 더 작은 FIFO를 가진 디바이스보다 더 큰 데이터 블록이 덜 빈번하게 전송될 수 있기 때문에 데이터 버스의 트래픽 양을 줄이므로 유용합니다.

예

PXIe-6614에는 127개의 샘플을 저장하는 각 카운터에 대한 FIFO가 있으므로 버스를 통한 추가 전송이 필요해지기 전에 펄스 트레인 생성을 위해 127개의 서로 다른 매개 변수를 구성할 수 있습니다.

내부 베이스 클럭(범용 카운터)

카운터의 내부 베이스 클럭은 게이트 터미널의 상태에 따라 카운터 값이 증가/감소하는 신호입니다. 이 클럭의 주기는 측정 또는 생성되는 신호의 분해능을 초 단위로 결정하지만 긴 펄스를 측정하거나 생성할 때 카운터가 얼마나 빨리 롤오버되는지도 결정합니다. 모든 카운터 측정 또는 어플리케이션에 대해 ±1 타임베이스 주기 양자화 에러가 있습니다. 양자화 에러의 양을 최소화하려면 어플리케이션에 가장 빠른 베이스 클럭을 선택하는 것이 중요합니다.

예

PXIe-6614를 사용하여 측정을 수행할 때 사용할 수 있는 3개의 내부 베이스 클럭 속도는 각각 100 kHz, 20 MHz 및 100 MHz입니다. 이 베이스 클럭은 10 µs ~ 10 ns 범위의 분해능을 제공합니다. 125 kHz의 PWM 신호와 35% 듀티 사이클이 적용되는 경우, 실제 펄스 폭(초)은 2.8 µs입니다. 이것은 100 kHz 베이스 클럭의 분해능보다 낮으므로 이 측정에는 사용할 수 없습니다. 20 MHz 클럭의 분해능은 50 ns이므로 이 신호의 지속 시간 ±1 베이스 클럭 펄스를 완벽하게 측정할 수 있습니다. 결과적으로 2.8 µs ± 0.05 µs의 측정 결과, 또는 약 1.8%의 에러가 발생합니다. 100 MHz 클럭에서 이와 동일한 측정을 수행하면 0.36%의 에러에 대해 2.8 µs ± 0.01 µs의 측정 결과가 나타납니다. 이 경우, 100 MHz 클럭은 카운터가 롤오버되기 전에 최대 약 43초의 펄스 폭을 측정할 수 있으므로 2.8 µs의 이 펄스 폭은 최대 한도보다 훨씬 낮습니다.

또한 다음을 참조하십시오

기타 스펙

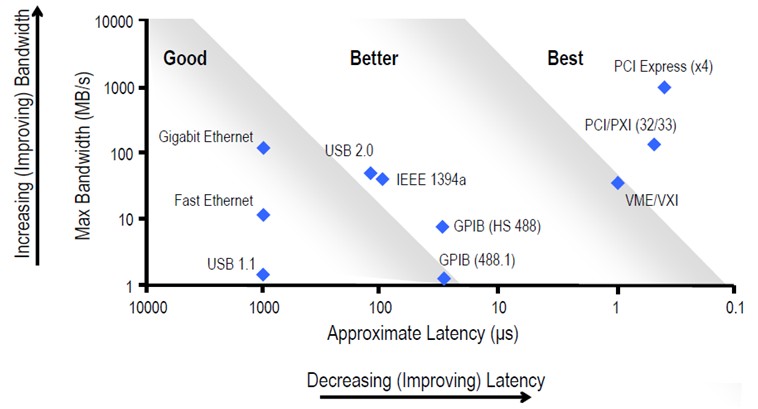

버스 인터페이스

PCI, PCI Express, PXI, PXI Express 및 USB는 모두 MIO DAQ 디바이스가 사용할 수 있는 버스 인터페이스의 예입니다. 이 버스는 데이터 처리량, 대기 시간, 이식성 및 채널 수 사이의 일부 중요한 트레이드오프를 제공합니다.

예

NI 6363은 USB, PXI Express 및 PCI Express 기반으로 제공됩니다. 이 디바이스와 모듈들은 기능이 유사하지만, PXI Express 모듈과 PCI Express 디바이스는 USB 디바이스에 비해 대기 시간이 짧고 처리량이 높습니다. PXI Express 모듈은 PXI Express 시스템의 추가 이점을 제공합니다. USB 디바이스는 핫스왑을 지원하고 더 소형화되어 모바일 어플리케이션에 적합하다는 이점이 있습니다.

교정

모든 테스트 및 측정 장비와 마찬가지로 디바이스가 지정된 정확도 셋팅 범위 내에서 작동하도록 일상적인 보정을 수행하는 것이 중요합니다. 이 디바이스에는 일정량의 자체 가열 기능이 있으므로 측정 전 지정된 예열 시간을 허용하여 안정적인 온도에 도달하는 것이 중요합니다. 이때 자기 교정 기능이 지원되는 경우에는 디바이스의 자기 교정을 실시할 것은 권장합니다. NI가 제공하는 교정 서비스에 대한 더 자세한 정보는 교정 서비스 를 참조하십시오.

예

USB-6363의 예열 시간은 15분이며 교정 주기는 2년입니다. 최적의 정확도를 보장하기 위해 15분 동안 전원을 켠 후 디바이스의 자기 교정을 실시할 것을 권장합니다. 디바이스 사용 후 2년이 경과하면 외부 교정을 맡길 것을 권장합니다.

전류 제한

모든 MIO 디바이스에는 싱킹 또는 소싱할 수 있는 최대 전류량이 있습니다. 이 섹션의 스펙은 싱킹 및 소싱 전류의 조합입니다. 일부 디바이스의 경우 서지 발생에 대비해 +5 V 사용자 라인에 셀프 리셋 퓨즈가 있습니다. 최대 전류 스펙을 초과하면 디바이스가 손상될 수 있습니다.

예

PXIe-6363이 포트 0의 모든 32 DIO 라인에서 최대 전류를 구동하는 경우(라인당 24 mA), 포트 0에서의 총 전류 인출량은 0.768 A입니다. 또한 커넥터 0과 1의 +5 V 사용자 라인에 연결되어 각 커넥터로부터 0.25 A를 인출하는 회로가 있는 경우, 모듈은 모두 1.268 A를 공급합니다. 0.25 A는 각 전원 커넥터의 최대 1 A 내에 있고, DIO 라인에서 인출되는 0.768 A와 +5 V 사용자 라인으로부터의 0.5 A의 합은 전체 출력의 최대 2 A 범위 내에 있습니다. 이 동일한 어플리케이션을 PCIe-6363에서 사용하는 경우, 디바이스가 최대 전류 제한 내에서 작동하도록 하려면 옵션인 디스크 드라이브 커넥터를 연결해야 합니다.

환경 관리

NI가 환경적으로 책임 있는 방식으로 제품을 설계하고 제조하기 위해 어떤 노력을 하고 있는지 자세히 알고 싶으시다면 환경 영향을 참조하십시오.

외부 디지털 트리거

MIO 디바이스는 모든 PFI 라인에서 디지털 트리거 신호를 가져오고 동기화 목적으로 디바이스에서 사용되는 가장 일반적인 신호 중 일부도 내보낼 수 있습니다. 샘플 클럭과 시작 트리거와 같은 신호는 MIO 디바이스에서 출력될 수 있습니다. DAQmx API를 사용하여 디지털 필터를 이러한 신호에 적용할 수 있습니다. 이 트리거 경로에 대한 자세한 정보는 NI MAX에서 디바이스의 라우팅 테이블을 참조하십시오.

- 극성 - 내보내거나 가져오는 신호가 활성 하이인지 활성 로우인지를 나타냅니다.

예

PXIe-6363은 아날로그 입력 시작 트리거를 아직 다른 작업이나 디바이스에서 사용하도록 예약되지 않은 PFI, PXIe_DSTARA, PXIe_DSTARB, PXI_TRIG 또는 PXI_STAR 라인으로 라우팅할 수 있습니다. MAX에서 디바이스 경로를 살펴보면 이 라우팅도 양방향이므로 디바이스가 동일한 소스 중 하나에서 아날로그 입력 시작 트리거를 수용할 수 있습니다.

주파수 생성기

MIO 디바이스에 존재하는 범용 카운터 외에도 주파수 발생기로 사용할 수 있는 기능이 제한된 별도의 카운터가 있습니다. 일반적인 MIO 디바이스에는 생성할 수 있는 제한된 수의 주파수로 제한되는 단일 주파수 생성기가 있습니다. 생성될 수 있는 주파수는 디바이스의 다른 서브시스템에 클럭 신호를 제공하는 데 사용되거나 외부 회로가 사용하도록 내보낼 수 있습니다.

예

PXIe-6363에는 3개의 베이스 클럭(20 MHz, 10 MHz 및 100 kHz) 중 하나를 사용하여 1에서 16까지의 제수로 나눌 수 있는 주파수 생성기 채널이 있습니다. 사용자가 50.0 kHz 신호를 생성하려면 100 kHz 베이스 클럭과 2의 제수를 선택할 수 있습니다. 다음 표는 가능한 주파수의 잘린 버전을 보여줍니다.

| 제수 | 베이스 클럭 | ||

|---|---|---|---|

| 20 MHz | 10 MHz | 100 kHz | |

| 1 | 20 MHz | 10 MHz | 100 kHz |

| 2 | 10 MHz | 5 MHz | 50 kHz |

| 3 | 6.67 MHz | 3.33 MHz | 33.3 kHz |

| ... | |||

| 15 | 1.33 MHz | 0.67 MHz | 6.67 kHz |

| 16 | 1.25 MHz | 0.63 MHz | 6.25 kHz |

작동 온도

MIO 디바이스가 작동하도록 설계된 주변 온도 범위를 지정합니다. 이 온도는 온보드 온도 센서인 DAQmx API를 사용하여 보고된 온도와 다릅니다.

예

PXIe-6363의 작동 온도 범위는 0°C ~ 55°C입니다. 정상적인 사용 중에 PCB 온도 센서가 더 높은 온도를 보고하면 허용됩니다.

PLL (Phase-Locked Loop)

일부 MIO 디바이스에는 위상 잠금 루프 회로가 내장되어 있어 디바이스가 해당 참조 클럭을 외부 참조 클럭에 고정할 수 있습니다. 디바이스가 외부 베이스 클럭에 잠기면 디바이스는 잠긴 클럭의 속도, 드리프트 및 정확도를 상속합니다. PXI 또는 PXI Express 디바이스는 PXI_CLK10 또는 PXI_CLK100 참조 클럭에 자동으로 고정됩니다. NI-DAQmx API를 사용하여 PFI 라인과 같은 다른 참조 클럭 소스에 고정할 수 있습니다.

예

USB-6363에는 하나의 PLL 회로가 내장되어 있으며 0에서 15까지의 PFI 라인에 있을 경우 10 MHz 클럭에 고정할 수 있습니다. DAQmx API를 사용하여 작업을 구성할 때, 참조 클럭을 외부 클럭이 연결된 PFI 라인으로 설정하십시오. PXIe-6363은 유사한 PLL 회로를 갖지만 DAQmx API를 사용하여 참조 클럭 소스를 셋팅하여 달리 지정하지 않는 한 PXI Express 섀시의 여러 디바이스에서 동기화하기 위해 PXI_CLK100 100 MHz 클럭에 자동으로 고정됩니다. PCIe-6363에는 모든 PFI 또는 RTSI 라인에 유사하게 잠글 수 있는 PLL 회로가 있습니다. PCI Express 또는 USB 디바이스에는 자동 잠금이 없습니다.

물리적 특성

NI는 디바이스를 구매하거나 시스템 모델을 생성하기 전에 클리어런스를 확인하는 데 사용할 수 있는 대부분의 제품의 치수 도면을 게시합니다. 치수 외에도 NI는 포괄적인 맞춤형 케이블, 커넥터 및 나사 목록을 제공합니다.

또한 다음을 참조하십시오

전원 요구사항

올바른 양의 전원을 공급할 수 있도록 USB 및 PCI 디바이스 또는 PXI 모듈의 전원 요구사항을 알아야 합니다. 이 섹션에 표시된 값은 정상적인 사용을 기준으로 하며, 스펙을 벗어나서 사용하는 경우 디바이스 또는 모듈이 인출할 수 있는 최대 전력을 나타내지 않습니다. USB 디바이스의 경우, NI 제공 전원 공급 장치가 권장 스펙을 충족하지만, 필요한 경우 타사 또는 맞춤형 공급 장치를 사용할 수 있습니다. PCI 또는 PCI Express 디바이스의 경우, 더 많은 전력이 필요한 경우 사용할 수 있는 보조 전원 커넥터가 있습니다. 이는 외부 회로에 전원을 공급하기 위해 +5 V 사용자 레일을 사용할 때 가장 일반적입니다. 자세한 내용은 전류 제한 [전류 제한 링크]을 참조하십시오. PXI 또는 PXI Express 모듈의 경우,이 스펙은 전력 예산을 수립할 때 유용합니다. 자세한 정보는 관련 링크를 참조하십시오.

예

옵션인 디스크 드라이브 전원 커넥터가 설치되지 않은 경우 PCIe-6363은 +3.3 V 레일에서 4.6 W, +12 V 레일에서 5.4 W를 인출합니다. 디스크 드라이브 커넥터는 디바이스에 최대 15 W를 공급할 수 있는 +5 V 레일을 추가하는 한편, +3.3 V 레일의 전력 인출량을 1.6W로 줄여줍니다.

또한 다음을 참조하십시오

안전성, 전자파 적합성 및 CE 규정

MIO 디바이스가 테스트되고 준수하는 기준은 스펙 매뉴얼의 세 섹션에 나와 있습니다. 모든 기준에 대한 자세한 내용을 보려면 제품 인증을 방문하십시오.

예

인증 검색을 사용하여 PXIe-6363의 컴플라이언스 스펙을 볼 수 있습니다. NI PXIe-6363 - 제품 인증

충격 및 진동

MIO 디바이스는 특정 산업 기준에 따라 테스트되어 스펙 및 디바이스 무결성에 따라 명시된 충격 및 진동 스펙에 대해 명시된 정확도가 유지되는지 확인합니다. 디바이스를 올바르고 정확하게 작동시키려면 이 지정된 값을 초과하지 않아야 합니다.

예

PCIe-6363은 IEC 60068-2-27, 그리고 MIL-PRF-28800F에 따라 개발된 테스트 프로파일에 따라 테스트되었습니다.