Open Dynamic Bitfile Reference Function

- Updated2025-01-28

- 3 minute(s) read

Open Dynamic Bitfile Reference Function

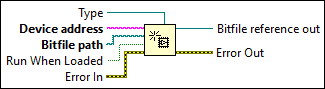

Opens a reference to an FPGA bitfile at run time and returns a dynamic FPGA interface. Use this function in place of the Open FPGA VI Reference function when you want to open a bitfile by path at run time.

You must open a reference to the FPGA target before the host VI can communicate with the FPGA VI. Only targets that use NI-RIO driver software support the Open Dynamic Bitfile Reference function.

Inputs/Outputs

Type

—

Type

—

Type specifies the reference data type to which you want to convert the dynamic interface reference. Wire any constant or control to Type to set the reference data type to which you want to convert the dynamic FPGA interface. Right-click the control or constant and select Configure FPGA VI Reference to configure the interface. The reference this function returns is cast to the data type you wire to Type. If you do not specify a data type, this function returns an empty dynamic interface reference.  Device address

—

Device address

—

Device address specifies the address of the FPGA target.  Bitfile path

—

Bitfile path

—

Bitfile path specifies the path to the bitfile. Bitfiles must have a .lvbitx extension.  Run When Loaded

—

Run When Loaded

—

Run When Loaded specifies whether the bitfile runs automatically after downloading. The availability of this option varies by FPGA target. The default is TRUE. If you set the value to FALSE, the FPGA VI waits to execute until you set the value to TRUE.  Error In

—

Error In

—

error in describes error conditions that occur before this node runs. This input provides standard error in functionality.  Bitfile reference out

—

Bitfile reference out

—

Bitfile reference out returns a reference to a bitfile.  Error Out

—

Error Out

—

error out contains error information. This output provides standard error out functionality. |

You can download and run only one FPGA VI at a time on a single FPGA target. If you attempt to download a second VI to the FPGA target while the first FPGA VI is still in use, LabVIEW reports an error and the download fails.

Place and wire a Close FPGA VI Reference function for every Open Dynamic Bitfile Reference function in a host VI. When the Open Dynamic Bitfile Reference function first executes, the function checks whether the compiled FPGA VI already exists on the FPGA target. If the compiled FPGA VI is not on the FPGA target, the Open Dynamic Bitfile Reference function downloads the compiled FPGA VI to the FPGA target.

Use this function with an FPGA Interface Dynamic Refnum wired to Type to specify the interface for the FPGA VI reference. The interface can contain elements such as controls, indicators, DMA channels, and target-specific methods.