Not Function

- Updated2025-03-14

- 2 minute(s) read

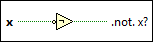

Computes the logical negation of the input. If x is FALSE, the function returns TRUE. If x is TRUE, the function returns FALSE.

The connector pane displays the default data types for this polymorphic function.

Inputs/Outputs

x

—

x

—

x can be a scalar Boolean value or number, array or cluster of Boolean values or numbers, array of clusters of Boolean values or numbers, and so on. If x is an error cluster, only the status parameter of the error cluster passes to the input terminal.  .not. x?

—

.not. x?

—

.not. x? is the logical negation of x. |

Not Truth Table

| x | .not. x? |

|---|---|

| F | T |

| T | F |

FPGA Module Details

The following details apply when you use this object in an FPGA VI.

| Single-Cycle Timed Loop | Supported. |

| Usage | For maximum time and resource efficiency, use Boolean functions inside a single-cycle Timed Loop. |

| Timing | Inside single-cycle Timed Loop--When you use Boolean functions inside a single-cycle Timed Loop, each Boolean operation adds slightly to the combinatorial logic delay of the single-cycle Timed Loop. Outside single-cycle Timed Loop--When you use Boolean functions outside a single-cycle Timed Loop, each Boolean operation requires one clock cycle. |

| Resources | Boolean functions consume significant FPGA resources only when you wire a large array to the input. Consider limiting arrays to conserve FPGA resources. |

Examples

Refer to the following example files included with LabVIEW.

- labview\examples\Booleans\Boolean Functions.vi