Add Function

- Updated2025-03-14

- 3 minute(s) read

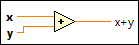

Add Function

Computes the sum of the inputs.

Inputs/Outputs

x

—

x

—

x can be a scalar number, array or cluster of numbers, array of clusters of numbers, and so on.  y

—

y

—

y can be a scalar number, a fixed-point number, an array or cluster of numbers, an array of clusters of numbers, a time stamp, and so on.  x+y

—

x+y

—

x+y is the sum of x and y. Note You can manually configure this function to output data of a type you want. To specify the output data type, right-click the function and select Properties to display the Object Properties dialog box. On the Output Configuration page, click the Representation icon and select the data type you want. A blue coercion dot appears on the output terminal of the function to indicate that you have configured the output data type.

|

Matrix Details

When you wire matrix data as an input to this function, a VI that includes subVIs that work with the matrix data type replaces the function. The resulting VI has the same icon but contains a matrix-specific algorithm. The node remains a VI if you disconnect the matrix from the inputs. Wire other data types as inputs to restore the original function. If you wire a data type to a function and that data type causes a basic math operation to fail, the function returns a NaN.

You also can add two or more values using the Compound Arithmetic function.

Fixed-Point Details

If you wire fixed-point values to Numeric functions such as Add, Subtract, Multiply, and Square, the functions usually return values that do not lose any bits of word length. However, if the operation creates a value that exceeds the maximum word length that LabVIEW accepts, overflow or rounding conditions can occur. LabVIEW accepts a maximum word length of 64 bits. Use the Numeric Node Properties dialog box to configure how LabVIEW handles overflow or rounding of fixed-point data.

FPGA Module Details

The following details apply when you use this object in an FPGA VI.

| Single-Cycle Timed Loop | Supported. |

| Usage | If you use this function with the single-precision floating-point data type, refer to the Using the Single-Precision Floating-Point Data Type and Deciding Which Data Type to Use in FPGA Designs topics for resource use, latency, and single-cycle Timed Loop support implications. |

| Timing | Inside single-cycle Timed Loop--When you use this function inside a single-cycle Timed Loop, the combinatorial logic delay is proportional to the number of bits in x or y, whichever data type is larger. Outside single-cycle Timed Loop--When you use this function outside a single-cycle Timed Loop, it takes one clock cycle and uses one register. If you use this function with the fixed-point data type, the overflow and rounding modes might impact timing. |

| Resources | This function requires FPGA resources proportional to the number of bits in x or y, whichever data type is larger. If you use this function with the fixed-point data type, the overflow and rounding modes might impact resources. |

Examples

Refer to the following example files included with LabVIEW.

- labview\examples\Numerics\Numeric Functions.vi