规范说明:NI多功能I/O (MIO) DAQ

概览

内容

引言

本指南与大多数NI规范手册的章节划分相同。以下术语和定义按字母顺序列出,并且在规范手册中可能会以不同的顺序出现。本指南仅适用于60xx、61xx、62xx和63xx系列(以前为B、E、S、M和X系列)MIO DAQ设备和模块。其他NI产品系列(如cDAQ和cRIO机箱与控制器,91xx、92xx、94xx C系列模块,多功能RIO 78xx R系列,数字万用表,示波器/数字化仪和其他仪器)的规范可能会采用不同的术语或方法。因此,除MIO DAQ系列中的设备和模块外,本指南不应用作其他设备和模块的参考。

本指南全篇将采用NI 6361和NI 6363设备作为参考。如果要同时查看这些产品规范,可以访问以下链接:NI 6361和NI 6363规范。

了解规范术语

首先,请务必注意不同规范之间的绝对差异。NI将其测试和测量仪器的功能与性能定义为“规范”、“典型规范”和“特有规范或补充规范”。有关保证规范或典型规范的更多详细信息,请参阅设备的规范手册。

- 规范描述了仪器在建议的校准周期及规定的工作条件下保证达到的性能。

- 典型规范是大多数仪器在建议的校准周期及规定的工作条件下可达到的规范。典型规范不受保证。

- 特有规范或补充规范描述了仪器在设计或开发时所构建,但未在验证或调整过程中进行评估的基本功能和属性。这些规范提供了上述定义中未包含的适当使用仪器相关的信息。

模拟子系统规范

NI MIO DAQ设备和模块可能具有模拟输入系统、模拟输出系统或同时具有两种系统。一些规范为各子系统的独有规范,但也有一些规范同时适用于两种子系统。本节分为三个部分,涵盖通用规范、特定于模拟输入的规范和特定于模拟输出的规范。

模拟输入和模拟输出

Absolute Accuracy at Full Scale(全量程绝对精度)

精度是指测量值与正确值的接近程度。全量程绝对精度是假设被测值为给定范围内支持的最大电压,从而计算得出的理论精度。测量的精度会随测量值的变化而变化,因此为了能够在设备之间进行比较,采用全量程精度。请注意,全量程绝对精度会假设环境变量(如25 °C运行环境温度),可能会与实际情况有所不同。

- 额定正向量程 — 可以在特定量程内测量的最大理想正值

- 额定负向量程 — 可以在特定量程内测量的最大理想负值

- 残余增益误差 — 仪表放大器固有的增益误差,一般存在于自校准后

- 增益温度系数 — 一种温度系数,描述与上一次自校准时的温度相比,温度对放大器的增益造成的影响

- 残余偏移误差 — 仪表放大器固有的偏移误差,一般存在于自校准后

- 参考温度系数 — 一种温度系数,描述与上一次外部校准时的温度相比,特定温度下的测量精度

- INL误差(相对精度分辨率)— ADC的电压输出与理想输出之间的最大偏差。可以认为是最坏情况下的DNL。另见:DNL

- 偏移温度系数 — 一种温度系数,描述与上一次自校准时的温度相比,温度对ADC转换中的偏移造成的影响

- 随机/系统噪声 — 模拟前端产生的其他系统噪声,通过将输入通道接地进行测量

示例

NI PXIe-6363的电压范围为±0.5 V。全量程绝对精度在假设被测信号为0.5 V的前提下计算得出。±0.5 V范围的全量程绝对精度为100 µV。

另见

Analog-to-Digital Converter (ADC) Resolution(模数转换器(ADC)分辨率)

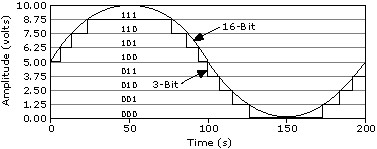

分辨率是指设备或传感器能检测到的输入信号的最小变化。ADC的分辨率由用于表示模拟信号的位数确定。

示例

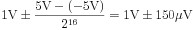

NI PXIe-6363是16位设备,即在±5 V范围内可以检测到的最小幅值变化为0.152 mV。在±0.1 V范围内,该值为3.05 µV。

Common Mode Rejection Ratio (CMRR)(共模抑制比(CMRR))

当放大器的正输入和负输入显示相同的信号时,CMRR会指定最终输出对该信号的抑制量(通常以dB为测量单位)。理想的放大器将消除100%的共模信号,但在实际中无法实现这一点。

示例

NI PXIe-6363的CMRR为100 dB。这意味着它会将共模电压衰减100,000倍。如果被测信号为5 Vpk正弦波,并且正负输入之间的偏移或常用电压为5 VDC,则最终输出会将5 VDC输入抑制或衰减至5 µV。精度推导中不包含CMRR,如果测得的信号包含共模电压,则应单独考虑CMRR。

Coupling(耦合)

两个电路的接口属性,用于定义从接口的一侧传输到另一侧的信号类型。通常有两种选择:

- 直流耦合:将传输交流和直流信号

- 交流耦合:仅传输交流信号,在硬件上实现消除信号的直流偏移

一些设备具有可选的软件耦合功能,而一些设备则具有交流或直流耦合功能。

示例

NI PXIe-6363的模拟输入和模拟输出均具有直流耦合功能,不支持交流耦合功能。

另见

Crosstalk(串扰)

测量一个通道上的信号对相邻通道的耦合或影响程度。只要在物理上靠近另一条导线或PCB迹线的导线或PCB迹线上存在幅度变化信号,就会存在串扰。

示例

NI PXIe-6363的串扰规范为,相邻通道-75 dB,非相邻通道-95 dB。这意味着通道ai2与通道ai1和ai3之间的串扰规范为-75 dB,而与所有其他ai通道的串扰规范为-95 dB。

Data Transfer Mechanisms(数据传输机制)

NI设备双向传输数据,从设备到计算机(输入),以及从计算机到设备(输出)。不同的总线(USB、PXI Express等)将使用不同的数据传输机制。一些总线可以支持多种传输机制。有关特定机制的更多信息,请参阅NI-DAQmx帮助文档。

示例

USB-6341支持USB Bulk(信号流)和编程控制I/O数据传输。NI PXIe-6363支持直接内存访问(DMA)和编程控制I/O。

另见

Differential Non-Linearity (DNL)(微分非线性(DNL))

DAC的理想步长(有关如何计算步长的信息,请参阅数模转换器(DAC)分辨率)与输出的实际值之间的差值(通常以LSB为测量单位)。在理想的DAC中,DNL为0 LSB。

示例

NI PXIe-6363的DNL为±1 LSB,即对于DAC输出的任何值,实际值可能与编程值相差±1 LSB。例如,如果用户对DAC进行编程,从而在±5 V的范围内输出1 V的值,则输出(不考虑精度的影响)的范围可以是:

INL是DNL的复合效应,因此INL规范经常用于精度计算中。对于NI PXIe-6363,精度表中的INL规范在所用范围为64 ppm或4 LSB。

Digital-to-Analog Converter (DAC) Resolution(数模转换器(DAC)分辨率)

从数字值转换时代表模拟信号的位数。

示例

NI PXIe-6363使用16位DAC,即有216个离散值可以在±5 V、±10 V或提供的用户电压之间输出。

另见

FIFO Size (Analog)(FIFO容量(模拟))

在执行模拟输入或模拟输出任务时,NI DAQ设备可以将数据存储在板载FIFO中。

- 对于输入任务,此FIFO用于在NI-DAQmx驱动程序软件将数据传输到RAM中预先分配的位置(称为PC缓冲区)之前缓冲数据。

- 对于输出任务,可以结合使用FIFO和PC缓冲区缓存用户请求生成的数据。

对于具有输入和输出通道的设备,每个子系统都有一个专用的FIFO。但是,此FIFO内的所有通道都共享此FIFO。对于模拟输入,NI-DAQmx实现了数据传输机制,从而确保将存储在FIFO中的数据尽快传输到PC缓冲区,使板载FIFO不会超限运行。对于模拟输出,NI-DAQmx实现了数据传输机制,从而确保将PC缓冲区中的数据尽快传输到板载FIFO,使FIFO不会欠载运行。对于模拟输出,用户可选属性可用于指定是否使用PC缓冲区,以及是否仅从板载FIFO重新生成单一波形。

示例

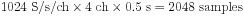

NI PXIe-6363的输入FIFO支持2,047个样本。这意味着使用四个通道以1,024 S/ch/s的速率采集数据的输入任务将在不到半秒的时间内使板载FIFO超限运行:

NI-DAQmx使用DMA将数据从FIFO传输到板载计算机内存(称为缓冲区),以避免超限。

另见

在NI-DAQmx中配置数据传输请求条件属性

Waveform Acquisition (DI) FIFO(波形采集(DI) FIFO)

Waveform Generation (DO) FIFO(波形生成(DO) FIFO)

Input Bias Current(输入偏置电流)

如果输入阻抗有限,设备需要少量电流才能检测到信号。理论上,该值应为0 A,但实际上这是不可能的。

示例

NI PXIe-6363的输入偏置电流为±100 pA。这意味着NI PXIe-6363测量的所有传感器必须能够在其整个电压输出范围内拉电流至少达到此水平,才能正确完成数字化。

Input Current During Overvoltage Condition(过压时的输入电流)

当设备处于过压状态时,该值为指定的设备灌电流量。

示例

NI PXIe-6363在过压状态下每个引脚灌电流最高达±20 mA。超过该值可能会损坏关键组件。

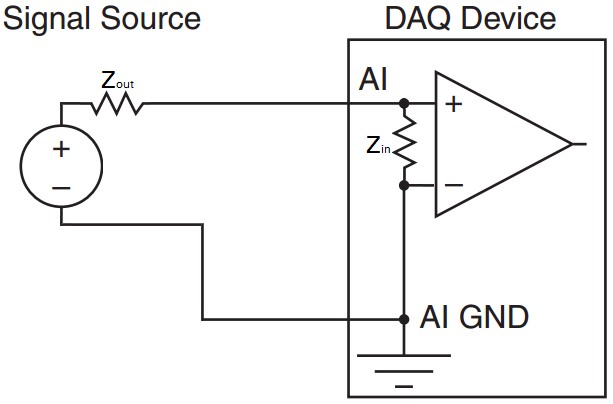

Input Impedance(输入阻抗)

输入阻抗用以衡量输入电路阻止电流流向模拟输入地的程度。对于理想的ADC,该值应为无穷大,表示没有电流从输入端流向地面,但实际上这是不可能的。有限输入阻抗表示ADC将给电路带来一定程度的负荷,特别是具有高输出阻抗的电路。传感器的输出阻抗通常较低。

示例

NI PXIe-6363的输入阻抗为Zin > 10 GΩ。以最低输入阻抗的最坏情况为例,您可以将单端测量视为以下简化电路,假设传感器的输出阻抗Zout = 150 Ω。

传感器输出和DAQ设备输入的串联组合意味着电压将在两个阻抗值之间分配,其中较大的阻抗将承受大部分电压。这表示,如果该传感器的灵敏度为20 °C/V,并且测量值为100 °C(输出5 V),那么DAQ设备测得的电压将是输出电压乘以输入阻抗与DAQ输入和传感器输出阻抗之和的比值:

75 nV的测量差值对应因阻抗而几乎可以忽略的0.5 °C测量误差。

为了说明输入阻抗成为重要规范的示例,以传感器具有极高输出阻抗(如5 GΩ)的假设情况为例。将DAQ设备连接到具有这一极高输出阻抗的传感器,会导致传感器的5 V额定输出读取值为3.33 V,或假设的测量误差为33.4 °C。

Maximum Update Rate(最大更新速率)

对于模拟输出,更新速率是指每秒DAC对模拟电压或电流值的采样次数。大多数NI设备在每个模拟输出通道上都有一个DAC,但将共享存储模拟输出数据的FIFO。当在同一设备上使用多个AO通道时,从此FIFO读取数据并将其传输到板载不同DAC的速率有时会限制更新速率。更新速率按照从单一通道输出的每秒样本数(S/s)或者从多个通道输出的每通道每秒样本数(S/s/ch)进行测量。

有关模拟输入等效值,请参见采样速率。

示例

NI PXIe-6363有四个模拟输出通道。

- 使用单个通道时,该通道上的更新速率为2.86 MS/s。

- 使用三个模拟输出通道时,最大更新速率为1.54 MS/s/ch — 当更多通道添加到扫描列表中时,从FIFO读取数据并发送到各个DAC的速率会逐渐限制更新速率。

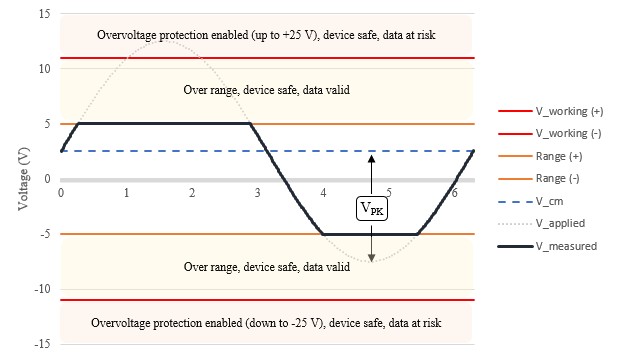

Maximum Working Voltage(最大工作电压)

最大工作电压是指在其他通道出现数据有效性问题之前,设备在任何模拟输入通道上可以承受的总电压水平。待测信号电压和AI GND有关的任何共模电压之和不应超过此最大工作电压规范,如此可确保其他通道上的精度。 请注意,最大工作电压与设备的输入范围无关。

示例

PXIe-6363上正在测量2.5 VDC共模的10 Vpk正弦波,其最大工作电压为±11 V,如下所示:

两个信号电压之和的峰值为+12.5 V,超出了最大工作电压。超出最大工作电压会使其他多路复用通道上的数据有效性受到威胁,这是因为没有足够的时间来稳定多路复用器上的多余电荷。

另见

Monotonicity(单调性)

单调性可保证当DAC代码增加时,输出电压也增加。

示例

NI PXIe-6363保证输出电压会随DAC代码的增加而增加。例如,斜坡函数将始终根据斜坡的方向增加或减少。

Output Current Drive(输出驱动电流)

对于模拟输出,输出驱动电流是设备灌电流或拉电流的最大量。连接的负载(包括输出阻抗)与编程电压相结合,确定了维持编程输出电压所需的电流。

如果驱动电流仍然低于指定的输出驱动电流,则可以保证提供编程输出电压。输出驱动电流过大会使设备进入过驱状态,输出电压无法再得到保证。

示例

NI PXIe-6363能够从任何模拟输出通道驱动±5 mA电流。在±10 V范围内,这意味着在全量程驱动的最低总阻抗取决于最大功率输出或最大电流和电压:

考虑到PXIe-6363的输出阻抗,在全量程驱动的最低连接阻抗为最小负载与输出阻抗之差:

另见

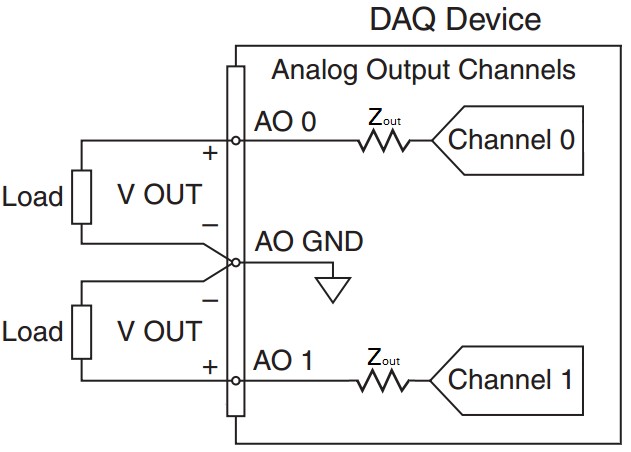

Output Impedance(输出阻抗)

输出阻抗是与模拟输出通道有效串联的阻抗,如下所示:

低输出阻抗允许将产生的更多电压分配给模拟输出的负载。请务必将输出阻抗考虑在内,从而确保达到所需的电压水平

示例

NI PXIe-6363的输出阻抗为0.2 Ω。即如果连接的负载阻抗为500 Ω,并且用户指定的电压为1 V,则负载上的实际电压为0.9996 V,比预期低0.4 mV。在该电压下,还将从设备流入1.99 mA的电流。

Overdrive (Short Circuit) Current(过(短路)电流)

如果输出阻抗和负载阻抗的总和太低,导致从设备流入的电流大于输出驱动电流指定的值,设备将进入过驱状态。过电流或短路电流是设备在不受损的情况下能够提供的最大电流量。在这种过驱状态下,电压将随电流流入的增加而下降。

超出过电流可能会损坏设备。NI建议始终在输出驱动电流规范内使用设备,以免损坏设备。

示例

NI 6363的过电流规范为26 mA。超过该值(例如在短路期间)可能会损坏设备。

另见

Overdrive Protection(过驱保护)

对于模拟输出,过驱保护是指在设备受到损坏之前通道上可以承受的最大电压。该规范高于在意外反向驱动电压的情况下可以编程的实际电压。

示例

NI PXIe-6363的每个模拟输出通道上分别受到高达±25 V的保护。即无论编程输出电压值为多少,只要引脚上AO GND有关的电压在±25 V以内,就不会对设备造成损坏。超出该值可能会损坏设备。

Overvoltage Protection(过压保护)

模拟输入电路中设有保护二极管,将对大电压进行限制,以免损坏设备的最关键组件,如PGIA或ADC。

- 当设备上电时,这些二极管会偏置一定的正电压和负电压,这意味着必须有大于偏置电压和反向电压之和的电压存在,才会使这些二极管过载而损坏。

- 当设备断电时,偏置电压将消除,因此使二极管反向所需的电压更低,从而使设备更容易受到损坏。

处于过压状态时,设备灌电流最大量由过压条件下的输入电流决定。

示例

NI PXIe-6363的两个AI引脚具有高达±25 V的保护。如果超过两个AI引脚的过压大于±25 V,可能会损坏设备。当设备断电时,保护电平较低,为±15 V。

Power-on State(上电状态)

上电状态指明了当设备上电时,以及在称为上电/断电毛刺的毛刺周期之后,模拟输出通道的值。在设备通过总线接收功率之前,可在上电毛刺规范中查看输出上的值。

示例

上电后,NI PXIe-6363模拟输出通道的电压为±5 mV。

Power-on/off Glitch(上电/断电毛刺)

设备接通和断开电源时,模拟输出通道上会出现毛刺信号。

- 毛刺能量幅值 — 毛刺信号在毛刺周期内达到的峰值幅度

- 毛刺能量持续时间 — 毛刺信号在上电状态下消退的时长

示例

NI PXIe-6363的指定毛刺为1.5 Vpk,时长200 ms。NI USB-6363的指定毛刺为1.5 Vpk,时长1.2 s。受固件更新和USB主机性能的影响,USB设备上的毛刺周期可能会比指定周期更长。

Range (Input or Output)(范围(输入或输出))

对于模拟输入,该值为可在保证精度的情况下测量的最大正值和负值。对于模拟输出,该值为可以生成的最大正值或负值。一些设备具有多个输入或输出范围,可用于在较低电平信号上提供更高的分辨率。

示例

NI PXIe-6363有四个输入电压范围:±0.1 V、±0.2 V、±0.5 V、±1 V、±2 V、±5 V、±10 V,有一个输出范围:±10 V。

另见

Analog-to-Digital Converter (ADC) Resolution(模数转换器(ADC)分辨率)

Digital-to-Analog Converter (DAC) Resolution(数模转换器(DAC)分辨率)

采样速率

采样速率指定了ADC将数据从模拟值转换为数字值的频率。某些设备只有一个ADC,因此,采样速率在通道之间共享,而另一些设备的每个通道都有专用的ADC。采样速率按照每秒样本数(S/s)或者每通道每秒样本数(S/s/ch)(从多个通道采集样本时)进行测量。

- 单通道最大值 — 对于在通道之间共享的采样速率,单通道采集数据的速率比共享时允许的速率高

- 多通道最大值 — 对于在通道之间共享采样速率的设备,该值为所有通道结合起来采集数据的最大速率

- 最小值 — 采集数据的最小速率

有关模拟输出等效值,请参见最大更新速率。

示例

NI PXIe-6363是多路复用设备,即模拟输入通道在一个ADC中实现多路复用。单个模拟输入通道对模拟信号的采样速率高达200万个/秒(2 MS/s)。在使用多通道时,所有通道结合在一起的速率必须小于1 MS/s(2个通道以500 kS/s/ch的速率进行采样,4个通道以250 kS/s/ch的速率进行采样,以此类推)。此设备没有最低采样速率。

Scan List Memory(扫描列表内存)

一个任务中扫描的通道数被指定为扫描列表内存。一个模拟输入任务可以在称为扫描列表的序列中包含许多虚拟通道。扫描列表可以多次包含相同的物理通道,并且可以按任意顺序进行采样。提交任务后,此扫描列表将被临时编程到DAQ设备。

示例

NI PXIe-6363的扫描列表内存有4,095个条目。即当单个任务中包含所有物理通道时,一次扫描或采样时钟的一个刻度便可以触发最多读取4,095个物理通道。但是,请牢记多通道测量的稳定时间(某些设备也称为转换间隔),该值会将采样时钟速率限制为最大250 Hz左右。

Settling Time(稳定时间)

模拟输出值稳定在一定精确度范围内所花费的时间。

示例

NI PXIe-6363的全幅跳变稳定时间在1 LSB或2 µs的15 ppm之内。即对于±5 V范围(-5 V、5 V、-5 V、5 V等)的全幅振荡,可以驱动到1 LSB以内的最大频率为1/(2 µs) = 500 kHz。

Settling Time for Multichannel Measurements(多通道测量的稳定时间)

执行多通道采集时,ADC必须连接到每个通道的时间。

示例

以±10 V的范围在NI PXIe-6363上采集数据时,多路复用器必须在单个通道上保持长达1.5 µs的时间,以便可编程增益仪表放大器(NI-PGIA)在提供全幅跳变输入的情况下,稳定在实际值的1个最低有效位(LSB)内。

Slew Rate(边沿斜率)

边沿斜率是指给定设备中模拟输出通道的变化速率。通常以V/µs为测量单位。输出的稳定时间使用计算中已包含的边沿时间计算得出。在设计用于高幅度高频信号的系统时,务必要考虑边沿斜率,因为幅度的大幅摆动可能会超出给定设备的边沿斜率。

示例

NI PXIe-6363的典型边沿斜率为20 V/µs,即可以产生的全量程高频为1 MHz。尝试输出幅度更大的全量程信号会导致不必要的失真。

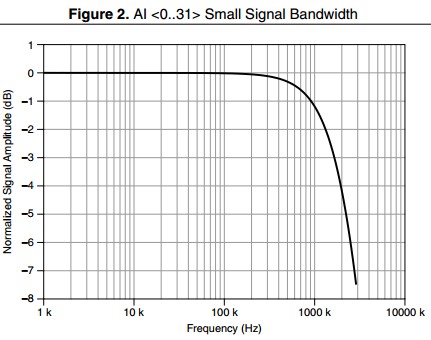

Small Signal Bandwidth(小信号带宽)

衰减小于–3 dB时通过的频率范围。小信号带宽的测试采用的是低压信号,因此不会出现边沿斜率失真。

示例

NI PXIe-6363的小信号带宽为1.7 MHz,如下所示:

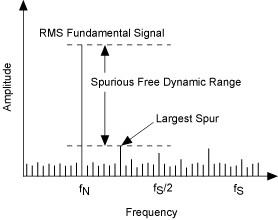

Spurious Free Dynamic Range (SFDR)(无杂波动态范围(SFDR))

无杂波动态范围是在杂波噪声干扰或导致基本信号失真之前的可用动态范围。模拟输入和模拟输出电路均具有会导致谐波失真的非线性特点。SFDR在频域中很容易观测到,如下所示:

示例

PCI-6133的SFDR约为95 dB。以下图为例,如果在0 dB时应用基本信号,则下一个最高杂波将在低于95 dB时出现,提供无杂波干扰的可用动态范围。

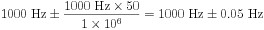

Timing Accuracy(定时精度)

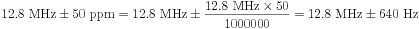

在NI DAQ设备上针对定时信号生成时钟信号时,产生的实际频率将处于定时精度范围内。该规范源自板载晶体振荡器的整体精度。定时精度通常以百万分之一(ppm)为测量单位。要将该精度值转换为Hz,请乘以精度值,再除以100万。时钟的频率不太可能在不同周期发生大幅度变化。

示例

PXIe-6363的定时精度为50 ppm。对于更新速率为1,000 S/s的模拟输出任务,采样时钟将以1,000 Hz ± 50 ppm的频率运行。以Hz为单位,结果为:

Timing Resolution(定时分辨率)

使用板载定时引擎时,模拟输入和输出任务的采样和更新速率限制为离散值。两个相邻速率之间的时钟周期之差称为定时分辨率。如果NI-DAQmx无法生成用户指定的准确频率,就会将所选频率强制提高到下一个可用频率。

示例

NI PXIe-6363的指定定时分辨率为10 ns。即它能够以10 ns的整数倍生成或采集数据。例如,32,000.00 Hz和32,010.2432...Hz是两个相邻的频率,因为它们的时钟周期分别为31.250 µs和31.240 µs。要查找下一个可用频率,请将定时分辨率与已知的时钟周期相加或相减。

Total Harmonic Distortion (THD)(总谐波失真(THD))

由于ADC和DAC组件固有的非线性特点,测量或生成的信号中将出现谐波频率。这些谐波功率之和与基波功率的比值称为总谐波失真。

示例

PCI-6133的指定THD约为-101 dB。即对于给定的测试信号(在本例中为全量程的10 kHz正弦波),信号中造成谐波失真的功率占比小于0.001%。相反,超过99.999%的测量功率由基音或特定的信号产生。

数字子系统规范

NI MIO DAQ设备和模块可支持数字输入、数字输出或同时具有两种系统。它们还支持可编程函数接口(PFI)线路,提供了可在背板上路由数字信号的方法。下文列出了常见规范及其定义,以及该规范的实际使用方法。

DI Sample Clock frequency(DI采样时钟频率)

确定可以采集数字波形数据的速率。对于基于USB的设备和基于PCI(包括PCI、PCI Express、PXI和PXI Express)的设备,此规范会有所不同。通常,基于PCI的设备支持更高的数字波形传输速率,因为其总线的持续吞吐量更高,延迟更低,且实现了直接内存访问(DMA)数据传输。

示例

NI 6363有三种组成结构:USB、PCI Express和PXI Express。

- USB — 采样时钟频率范围为0到1 MHz,具体取决于总线上其他设备的活动。例如,如果您要将数据记录到与设备位于同一USB集线器的USB外部硬盘上,可能无法达到1 MHz的全采集速率。为了获得最佳性能,NI仅建议在USB根集线器上使用USB DAQ设备。

- PCI Express和PXI Express — 采样时钟频率范围为0到10 MHz,具体取决于总线上其他设备的活动。例如,如果在采集过程中有大量数据被发送到GPU进行并行处理,可能无法达到10 MHz的全采集速率。为了获得最佳性能,NI建议当PCI Express或PXI Express设备与其他设备位于同一台交换机上时,所有设备都沿同一方向发送数据。

DO Sample Clock frequency(DO采样时钟频率)

确定在大多数NI设备上可以从端口0输出数字波形数据的速率。对于基于USB的设备和基于PCI(包括PCI、PCI Express、PXI和PXI Express)的设备,以及数据的来源不同,此规范会有所不同。

- 从FIFO重新生成 — 用户一次性向设备写入数据,然后数据在设备上重新生成。这种方法消除了总线通信量的问题,提高了输出率。

- 从内存流式传输 — 设备不会重新生成数据,因此用户的应用中必须一直提供可用的新数据,以避免发生下溢错误。此方法会使总线上的通信持续不断,因此更新速率在吞吐量较低的总线上受到的限制更大。

示例

NI 6363有三种组成结构:USB、PCI Express和PXI Express。

- USB — 与PCI Express和PXI Express相比,吞吐量较低且总线延迟较高。从FIFO重新生成输出波形时,可以达到10 MHz的最大更新速率。从内存进行流式传输时,必须通过USB流式传输数据,因此指定的最大速率较低,为1 MHz。

- PCI Express和PXI Express — 这些总线速度更快,可以维持更高的吞吐量,并提供10 MHz的指定最大更新速率。

Debounce Filter Settings(去抖动滤波设置)

当数字线路状态变化时(从低到高,或从高到低)时,有时会在两个状态之间抖动,然后再稳定到新状态。可以实现去抖动滤波来忽略抖动,仅在稳定后才读取数值。对于静态数字输入线路(PFI/端口1/端口2),数字去抖动滤波用于对噪声或毛刺信号(如通常来自开关按钮等物理接口的信号)进行去抖动。与数字线路滤波器不同,用户可以定制这些滤波器,设置任意滤波器长度。

示例

PXIe-6363支持90 ns、5.12 µs、2.56 ms或自定义滤波器的间隔定时。还支持可编程的高低转换,且每条输入线路均可选。这些滤波器时间取决于PXIe-6363上的板载振荡器。

Delta VT Hysteresis (VT+ - VT-)(迟滞差值(VT+ - VT-))

迟滞是基于值的增加或减少而具有不同转换阈值的属性。在这种情况下,观测到的转换为从高状态到不确定状态,以及从低状态到不确定状态。正向和反向阈值之间的差值为电压阈值迟滞。本规范说明了在再次进入不确定状态之前,电压水平可以低于或高出阈值的量。

示例

NI PXIe-6363规定的迟滞至少为0.2 V。即如果信号从0 V转换为5 V,则在逻辑电平被认为是低电平之前,它最多可以低于VT+值0.2 V。在这段变化期间,该值将处于不确定状态。

Digital Line Filter(数字线路滤波器)

在端口0的任意线路上启用线路滤波器后,该线路必须在指定的滤波器时间内保持稳定的逻辑电平,才能被记录为逻辑电平。这款工具对于通过长电缆或在嘈杂环境中传输数字数据十分有用。通常可以在软件中选择不同的滤波器时间:短、中和长。根据系统噪声的特性,其中可能会有一种滤波器时间更适合您的应用。

示例

PXIe-6363具有三种内置的数字线路滤波器时间:160 ns、10.24 µs和5.12 ms。请注意,这些滤波器仅适用于端口0中的线路。有关端口1和2、PFI线或PXI专用线路上的滤波选项,请参见去抖动滤波设置。

Direction Control(方向控制)

确定是否可以将数字线路或PFI线路配置为输入线路或输出线路。

示例

PXIe-6361支持将每条数字线路或PFI线路配置为输入或输出。

Ground Reference (Digital)(接地参考(数字))

是指测量或生成数字信号有关的参考点。例如,逻辑高数字输出可以在输出引脚和指定的接地参考之间测量5 V。

示例

PXIe-6361使用数字接地(D GND)信号作为数字输入、数字输出和PFI线路信号的接地参考。数字接地与模拟接地分开,从而避免不同电平和频率的信号混合造成干扰。数字接地和模拟接地均以机箱接地为参考。应格外留意USB设备,因为模拟接地和数字接地通过USB电缆的屏蔽层以计算机机箱接地为参考。

Input High Current/Input Low Current (IIH/IIL)(输入高电流/输入低电流(IIH/IIL))

理想情况下,设备的输入阻抗无限大,并且不会流入电流,但实际上无法实现。当在0 V或5 V下读取数字值时,NI设备的数字输入电路将流入少量电流。测量高电压水平时流入的电流量为输入高电流,同样,测量低电压水平时流入的电流量为输入低电流。请务必确保被测数字信号具有承受指定电流值的能力。

示例

当Vin = 0 V时,NI PXIe-6363拉电流将达10 μA;当Vin = 5 V时,灌电流将达250 μA。这适用于所有的数字线路和PFI线路。

Input High Voltage/Input Low Voltage (VIH/VIL)(输入高压/输入低压(VIH/VIL))

为了记录逻辑高压或逻辑低压,输入信号应处于建议的工作电压范围。该规范定义了建议的工作条件,以便用户知道其信号应该是什么值,而VT+和VT-是设备本身的规范。

示例

NI PXIe-6363将被记录为低信号的电压输入范围指定为0 V至0.8 V。对于高信号,该范围为2.2 V至5.25 V。如果低于0 V和高于5.25 V,设备将处于过压保护状态。也存在不确定的范围,即如果从低到高或从高到低的变化不超过VIH或VIL,则不记录。

另见

Positive-going Threshold (VT+)/Negative-going Threshold (VT-)(正向阈值(VT+)/反向阈值(VT-))

Input Voltage Protection (Digital)(输入电压保护(数字))

Input Voltage Protection (Digital)(输入电压保护(数字))

各个数字输入线路都有专门的I/O保护,可防止出现静电放电(ESD)和过压情况。为了提高设备的安全性,所有数字线路和PFI线路都共享第二级保护。多条线路上同时出现过压情况,会给此共享保护电路造成压力,并可能导致设备损坏。

示例

NI PXIe-6363同时最多在两个引脚上提供±20 V的输入电压保护。即每条线路可以安全地承受高达±20 V的过压,但不得有两条以上线路同时超过额定电压输入。

另见

Input High Voltage/Input Low Voltage (VIH/VIL)(输入高压/输入低压(VIH/VIL))

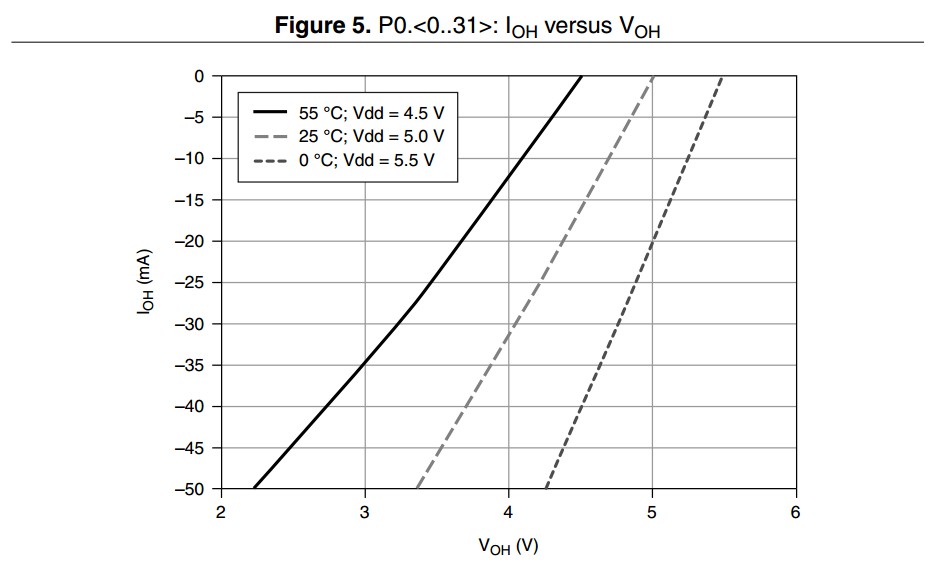

Output High Current/Output Low Current (IOHIOL)(输出高电流/输出低电流(IOH/IOL))

在输出高电流值或低电流值时,大多数NI设备的额定电压为0 V和5 V。但是,如果连接了阻抗相对较低的负载,电流需求会更高,而该额定电压将从0 V升高或从5 V降低。此规范体现了输出电流与输出电压之间的关系。

示例

根据向引脚写入的高值或低值,PXIe-6363能够具有拉电流或灌电流能力。对于端口0,建议的最大拉电流和灌电流值为每条线路24 mA。当电流离开设备(流出)时,电流显示为-24 mA。当电流进入设备(灌入)时,电流显示为+24 mA。请参见下图,了解在给定的温度和输出电压下流入电流量的特性。

Port/Sample Size(端口/采样容量)

采集或生成数字波形时,端口0中的线路数决定了采样的容量。为了限制总线上的通信量,如果采样包含线路0到7的任意组合,则采样容量将为1个字节。同样,如果采样仅包含线路0至15,则采样容量将减少至2个字节。这取决于端口中的最大线路数,也取决于端口的总容量。

示例

NI PXIe-6363在端口0中有32条线路。即单个数字采样最长为32位(4个字节)。

Positive-going Threshold (VT+)/Negative-going Threshold (VT-)(正向阈值(VT+)/反向阈值(VT-))

在向设备输入逻辑信号时,信号将从不确定范围变为逻辑高范围时所处的值称为正向阈值。相反,反向阈值是必须超过该值才能记录逻辑低值的电压水平。正向阈值将始终大于反向阈值。请务必确保您的信号确实超过这两个水平,从而准确记录数字状态。这些规范针对设备本身,而高低输入电压为建议的工作条件。

示例

NI PXIe-6363的VT+最高为2.2 V,VT-最低为0.8 V。

另见

Input High Voltage/Input Low Voltage (VIH/VIL)(输入高压/输入低压(VIH/VIL))

Pull-down/Pull-up Resistor(下拉/上拉电阻)

一些NI设备能够以编程方式将其数字线路或PFI线路配置为输入、输出或高阻抗。拉电阻用于确保原本可浮接的任意引脚参考一个已知的信号,如接地或电压源。下拉电阻会将浮接信号拉至接地状态或逻辑低电压值,而上拉电阻会将浮接信号拉至逻辑高电压值。

示例

PXIe-6361使用50 kΩ的下拉电阻,可确保未被主动驱动为高电压或低电压的接线端会浮接至低电压状态。

Waveform Acquisition (DI) FIFO(波形采集(DI) FIFO)

读取数字波形数据时,设备上有一个可缓冲数据的临时存储元素,称为FIFO。DAQmx将数据从该FIFO复制到RAM中的内存块中,该内存块称为PC缓冲区。诸如LabVIEW等ADE将数据从缓冲区复制到应用内存中。该FIFO的容量和在其中存储数据的速率决定了DAQmx驱动程序为避免溢出而复制数据的频率。

示例

NI PXIe-6363的数字波形采集FIFO有255个样本。即如果您以100 kbit/s的速率采集数据,而DAQmx驱动程序未在PC缓冲区中传输数据,则板载FIFO将在约2.5 ms内溢出。

Waveform Generation (DO) FIFO(波形生成(DO) FIFO)

板载MIO设备上有临时存储,可在称为FIFO的先进先出数据结构中缓冲数据点。对于通过总线传输历时较长的USB设备(尤其是当许多设备共享同一USB根集线器时),此存储特别有用。如果只需要一个数字模式,可以将此模式加载到此FIFO上,从而避免多次通过总线传输数据。用户可以使用DAQmx API,针对这两种情况进行编程。

示例

NI PXIe-6363的数字波形生成FIFO有2,047个样本。例如,如果您以100 kbit/s的数据速率将数字输出用于I2C通信,则整个FIFO将在20 ms内输出。这意味着用户应更加频繁地调用DAQmx写入,才能继续将数据流式传输到FIFO。如果进行数据速率测试,可以使用DAQmx API将单个模式加载到FIFO中,并以不同的数据速率输出,而不必通过PCI Express总线写入新数据。

计数器规范

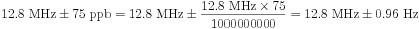

Base Clock Accuracy (general-purpose counters)(基准时钟精度(通用计数器))

内部基准时钟的精度直接影响通用计数器的任何测量或频率生成的精度。该精度还继承了设备的整体时基精度,即如果从外部提供更高精度的主时基,就可以提高该时钟的精度。

示例

PXIe-6363的基准时钟精度为50 ppm。如果用户希望使用此模块生成12.8 MHz的自由运行时钟,可以使用以下计算来确定精度:

使用精度更高的外部基准时钟或具有更高基准时钟精度的设备(如PXIe-6614)可以改进此错误。PXIe-6614使用更精确、更稳定的恒温晶体振荡器(OCXO),不易受到温度变化的影响,在最坏情况下,其基准时钟精度为75 ppb。如果要在此模块上生成相同的信号,实际频率将为:

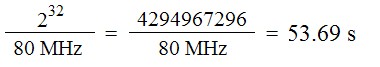

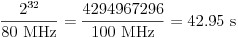

Counter Resolution(计数器分辨率)

计数器可用于表示数字的位数。将通用计数器配置为输出脉冲时,该脉冲有效的时间长度由计数寄存器中的值表示。该值与计数器计数的速率(由计数器的基准时钟设置)共同决定了可以实现的最大脉冲宽度。同样,在使用计数器测量信号的脉冲宽度时,可以记录的最大脉冲宽度由计数器的基准时钟和计数器的分辨率决定。如果信号超过了最大脉冲宽度,计数器将溢出,NI-DAQmx API将返回错误。因此,了解如何计算最大信号参数十分重要。

在平衡分辨率和测量/生成长度时,分辨率较高的计数器灵活性更大。有关平衡的更多详情,请参见下图。

示例

PXIe-6614使用32位计数器执行计数器输入和计数器输出任务。如果将计数器输入任务配置为测量脉冲宽度,我们可以计算最大计数器值并除以计数器的内部基准时钟速率,以此方式来计算可测量的最大脉冲宽度。100 MHz计数器的基准时钟支持10 ns的精确度,因此本示例中将选择该基准时钟。

External Base Clock Frequency (general-purpose counters)(外部基准时钟频率(通用计数器))

如果需要特定的基准时钟速率,大多数NI MIO设备都支持使用外部基准时钟。该时钟与内部基准时钟的用途相同,但由用户从外部提供。由于带宽限制,外部基准时钟的最大速率取决于设备的总线。

示例

NI 6363有多种组成结构,对外部基准时钟有不同的要求。

- PCI Express和USB — 外部基准时钟的频率范围为0至25 MHz,可在任何PFI线路上输入。最大频率的限制由PFI线路的带宽决定。

- PXI Express — PXIe-6363利用了PXI Express机箱的先进功能,差分星形线路(DSTAR)上支持高达100 MHz的信号。

FIFO (general-purpose counters)(FIFO(通用计数器))

板载MIO设备上的先进先出(FIFO)存储器元素用于缓冲输入或输出应用的数据样本。对于计数器输入应用,在DAQmx自动将数据传输到PC RAM的预分配块之前,数据点(如特定时间间隔的计数器值)将存储在FIFO中。FIFO用于计数器输出应用,用于存储占空比和频率值序列,从而更改正在生成的波形形状。较大的FIFO可以减少数据总线上的通信量,实用性较强,因为与具有较小FIFO的设备相比,它能以更低的频率传输较大的数据块。

示例

PXIe-6614的每个计数器都有一个相应的FIFO,可存储127个样本,支持在需要通过总线进行额外传输之前为脉冲序列的生成配置127个不同的参数。

Internal Base Clocks (general-purpose counters)(内部基准时钟(通用计数器))

计数器的内部基准时钟是一种信号,将导致计数器的值根据栅极接线端的状态而增加/减少。该时钟的周期不仅确定了将测量或生成的信号的分辨率(以秒为单位),也确定了在测量或生成长脉冲时计数器溢出的速度。对于任何计数器测量或应用,都存在±1时基周期量化误差。为了最大程度地减少量化误差,请务必为您的应用选择尽可能快的基准时钟。

示例

使用PXIe-6614执行测量时,可以使用的三种内部基准时钟的速率分别为100 kHz、20 MHz和100 MHz。这些基准时钟的分辨率范围为10 µs至10 ns。如果采用125 kHz的PWM信号和35%的占空比,以秒为单位的实际脉冲宽度为2.8 µs。由于该值低于100 kHz基准时钟的分辨率,因此不能用于本测量。由于20 MHz时钟的分辨率为50 ns,因而可以完美测量此信号的持续时间±1个基准时钟脉冲。测量结果为2.8 µs ± 0.05 µs,或误差约为1.8%。在100 MHz时钟上进行同样的测量时,测量结果将为2.8 µs ± 0.01 µs,误差为0.36%。在这种情况下,100 MHz时钟在计数器溢出之前,可以测量长达约43秒的脉冲宽度,因此2.8 µs的脉冲宽度远低于最大限值。

另见

其他规范

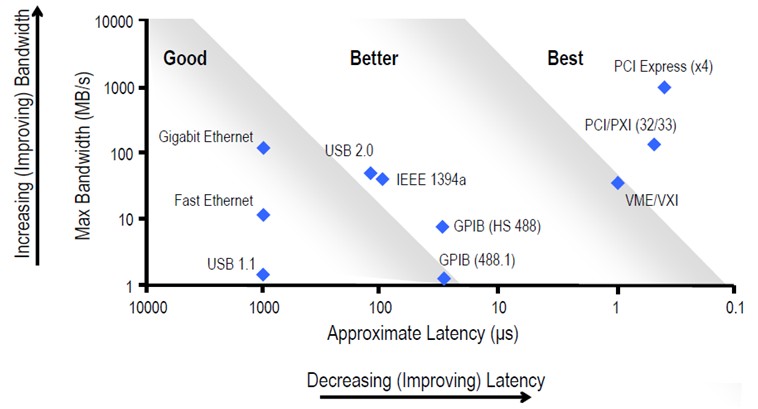

Bus Interface(总线接口)

PCI、PCI Express、PXI、PXI Express和USB均为MIO DAQ设备可能采用的总线接口示例。这些总线在平衡数据吞吐量、延迟、可移植性和通道数方面起到了关键作用。

示例

NI 6363采用USB、PXI Express和PCI Express。尽管这些设备和模块具有相似的功能,但与USB设备相比,PXI Express模块和PCI Express设备的延迟更低,吞吐量更高。PXI Express模块具有PXI Express系统的额外优点。USB设备具有支持热插拔和更紧凑的优点,更适合移动应用。

Calibration(校准)

与所有测试和测量设备一样,执行常规校准来确保设备在指定的精度设置内运行十分重要。由于设备会自行散发一定热量,因此在进行任何测量之前,请务必按指定的时间进行预热,从而确保达到稳定的温度。对于这种情况,如果支持,建议对设备进行自校准。有关NI提供的校准服务的更多信息,请参见校准服务。

示例

USB-6363的预热时间为15分钟,校准周期为2年。NI建议在上电15分钟后对设备进行自校准,从而确保达到最佳精度。使用两年后,NI建议寄回设备进行认证校准。

Current Limits(电流限制)

每个MIO设备都有最大灌电流或拉电流量。本部分中的规范包含了灌电流和拉电流。某些设备在+5 V用户线路上配备了自复位保险丝,以防出现意外电涌。如果超过最大电流规范,可能会损坏设备。

示例

如果PXIe-6363从端口0的所有32条DIO线路驱动最大电流(每条线路24 mA),则从端口0流入的总电流将为0.768 A。如果连接器0和连接器1上的+5 V用户线路还连接了电路,且从每个连接器流入0.25 A,则模块总计将提供1.268 A的电流。0.25 A的电流未超过每个电源连接器的最大电流1 A,且从DIO线路流入的0.768 A电流加上+5 V用户线路流入的0.5 A电流,也未超过总输出的最大电流2 A。如果要在PCIe-6363上使用相同的应用,需要连接可选的磁盘驱动连接器,从而确保设备运行时不超过最大电流限制。

Environmental Management(环境保护)

有关NI致力于以环保的方式设计和制造产品的更多信息,请访问环境影响。

External Digital Triggers(外部数字触发)

MIO设备能够从任何PFI线路导入数字触发信号,并能够导出设备上为了同步而使用的一些最常见的信号。采样时钟和开始触发等信号可以从MIO设备输出。使用DAQmx API可以将数字滤波器应用于其中任何信号。有关这些触发路由的更多信息,请参见NI MAX中设备的路由表。

- 极性 — 表明要导出或导入的信号是有效高电平还是有效低电平

示例

PXIe-6363能够将模拟输入开始触发路由到尚未保留供其他任务或设备使用的任何PFI、PXIe_DSTARA、PXIe_DSTARB、PXI_TRIG或PXI_STAR线路。查看MAX中的设备路由,该路由也是双向的,这意味着该设备可以接受来自任何相同来源的模拟输入开始触发。

Frequency Generator(频率发生器)

除了MIO设备上的通用计数器外,还有一个功能有限的独立计数器可用作频率发生器。典型的MIO设备配备一个频率发生器,其仅限于生成有限数量的频率。所生成的频率可用于为设备上的另一个子系统提供时钟信号,或者可以导出以供外部电路使用。

示例

PXIe-6363有一个频率发生器通道,可以从三个基准时钟(20 MHz、10 MHz和100 kHz)中选择一个,并将其除以1到16的分频数。如果用户希望生成50.0 kHz的信号,可以选择100 kHz基准时钟和分频数2,下表显示了部分可能得到的频率。

| 分频数 | 基准时钟 | ||

|---|---|---|---|

| 20 MHz | 10 MHz | 100 kHz | |

| 1 | 20 MHz | 10 MHz | 100 kHz |

| 2 | 10 MHz | 5 MHz | 50 kHz |

| 3 | 6.67 MHz | 3.33 MHz | 33.3 kHz |

| ... | |||

| 15 | 1.33 MHz | 0.67 MHz | 6.67 kHz |

| 16 | 1.25 MHz | 0.63 MHz | 6.25 kHz |

Operating Temperature(运行环境温度)

是指MIO设备计划运行的环境温度范围。该温度不同于使用板载温度传感器DAQmx API报告的温度。

示例

PXIe-6363的运行环境温度范围为0至55 °C。如果PCB温度传感器在正常使用期间报告的温度较高,也可以接受。

Phase-Locked Loop (PLL)(锁相环(PLL))

某些MIO设备具有板载锁相环电路,使设备能够将其参考时钟锁定为外部参考时钟。当设备锁定到外部参考时钟时,将沿用其锁定时钟的速率、漂移和精度。PXI或PXI Express设备可自动锁定到PXI_CLK10或PXI_CLK100参考时钟。NI-DAQmx API可用于锁定另一个参考时钟源,例如PFI线路。

示例

USB-6363有一个板载PLL电路,并且在0至15任意PFI线路(如存在)上都可以锁定到10 MHz时钟。使用DAQmx API配置任务时,应将参考时钟设置为外部时钟所连接的PFI线路。PXIe-6363有类似的PLL电路,但是除非使用DAQmx API设置参考时钟源另行指定,否则会自动锁定到PXI_CLK100 100 MHz时钟,以便在PXI Express机箱中的多个设备之间进行同步。PCIe-6363有PLL电路,同样可以锁定到任何PFI或RTSI线路。PCI Express或USB设备没有自动锁定功能。

Physical Characteristics(物理特性)

NI发布了大多数产品的尺寸图,可用于在购买设备或创建所建系统的模型之前检查空间情况。除了尺寸之外,NI还提供了完整的定制线缆、连接器和螺丝列表。

另见

Power Requirements(电源要求)

请务必了解USB和PCI设备或PXI模块的电源要求,以便提供正确的功率。本部分提供的值适用于正常使用的情况,并未列出在规范外使用设备或模块可能消耗的最大功率。对于USB设备,NI提供的电源符合建议规范,但是如果需要,您可以使用第三方电源或定制电源。对于PCI或PCI Express设备,如果需要更多电源,可以使用辅助电源连接器。这在使用+5 V用户导轨为外部电路供电时最为常见。有关更多信息,请参阅电流限制[链接到电流限制]。对于PXI或PXI Express模块,该规范在制定电源预算时很有用。详细信息见相关链接。

示例

如果未安装可选的磁盘驱动电源连接器,PCIe-6363在+3.3 V导轨消耗4.6 W功率,在+12 V导轨消耗5.4 W功率。磁盘驱动连接器添加了一个+5 V导轨,可以为设备提供高达15 W的功率,同时将+3.3 V导轨的功耗降低到1.6 W。

另见

Safety, Electromagnetic Compatibility, CE Compliance(安全性、电磁兼容性、CE规范)

我们规范手册的三个部分中列出了MIO设备测试和遵循的标准。有关任何标准的更多信息,请访问产品认证。

示例

认证搜索可用于查看PXIe-6363的合规性规范:NI PXIe-6363 — 产品认证

Shock and Vibration(冲击和振动)

MIO设备已按照特定的行业标准进行了测试,确保规定的精度符合规范,且设备完整性保持在规定的冲击和振动规范内。请务必不要超过这些指定值,从而确保设备正确、准确地运行。

示例

PCIe-6363已根据IEC 60068-2-27进行了测试,且已根据MIL-PRF-28800F制定了测试配置文件。