NI SourceAdapt次世代SMUテクノロジ

概要

ソースメジャーユニット (SMU) は、は、トランジスタなどの電子部品からポータブル音楽プレーヤ、医療機器といった統合電子製品まで、さまざまなデバイスの電流-電圧 (I-V) 特性をテストするために使用される重要クラスの計測器です。NIのNI SourceAdaptテクノロジは、4チャンネルNI PXIe-414x高精度SMUに初めて搭載された、従来のアナログ制御ループの代わりにデジタル制御ループを使用する次世代テクノロジです。NI SourceAdaptテクノロジを使用することで、あらゆる負荷に対する応答をカスタマイズでき、立ち上がり時間を最小化し、オーバーシュートや発振のない理想的な応答を実現できます。NI SourceAdaptは、すべてのNI高精度システムSMU、PXI電子負荷モジュール、PXIプログラマブル電源の一部のオプションに搭載されています。 SourceAdaptテクノロジの裏側を見てみましょう。この記事では、主にSMUに関連するSourceAdaptの操作について説明しますが、PXI電子負荷モジュールまたはPXIプログラマブル電源にも同じように当てはまります。

内容

- 概要

- 従来のアナログ制御ループの限界

- SourceAdaptテクノロジの基礎となるアーキテクチャについて

- 無効負荷による処理

- フィードバック補償器の使用

- SMUで理想的な応答を実現

- まとめ

- 次のステップ

概要

SMUは、閉ループフィードバック制御を利用して、プログラム済みのソース値 (設定値) を確実にテスト対象負荷へと正しく適用します。従来のSMUはアナログハードウェアで制御ループを実装してきましたが、これにはトレードオフがあります。たとえば、高速テスト向けの高帯域SMUは通常、高い安定性が求められる高容量性負荷のテストには適していません。その一方、高容量性負荷のテスト向けのSMUは、高速テストに最適であるとは言えません。実際、ほとんどの従来型SMUは、高速テストと高安定性テストのいずれかに最適化されています。それでも、最適な応答を得るのは簡単ではありません。負荷のさまざまな範囲に適した応答のみが得られる回路を設計するのは非常に難しいからです。

NI SourceAdaptテクノロジは、特定の負荷に対するSMUの応答をカスタム調整しやすくすることで、この問題に根本から対処するものです。これにより、最小限の整定時間で最適なSMU応答が実現できるので、待機時間が短縮されると同時にテストを高速化できます。またオーバーシュートが除去されることでテスト対象デバイス (DUT) を保護し、発振を防ぐことでシステムの安定性を確保できます。

SMU応答の調節をプログラミングによって行えるため、高速テスト向けに構成されたSMUを高安定性テスト向けに再構成するといったことも簡単に行えます – これは、テスト装置の投資収益率の最大化と、より良好なテスト結果の獲得の両立につながります。

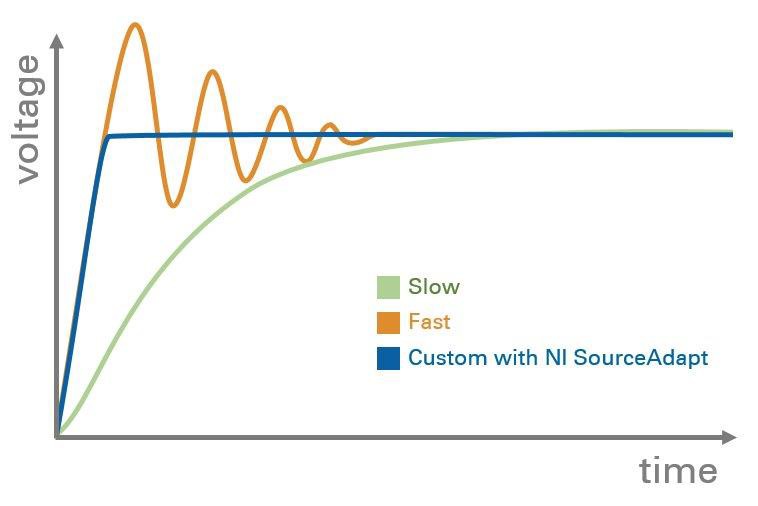

図1.容量性負荷に対するSMUの応答。NI SourceAdaptテクノロジによって応答をカスタマイズし (赤い線)、最大の安定性と最小の過渡応答時間を実現。

従来のアナログ制御ループの限界

従来、テスト計測器のベンダは、さまざまな手法で、構成可能な伝達関数を提供していました。従来、そうした手法の1つに、制御ループのフィードバックパスの内外でリアクタンス素子を切り替えるというものがあります。この手法には、構成可能な範囲や拡張性の面で効果が限定的だという問題があります。SourceAdaptテクノロジで得られるような真のカスタム補正を実現するには、SMU制御ループのアーキテクチャについて抜本的に見直す必要がありました。

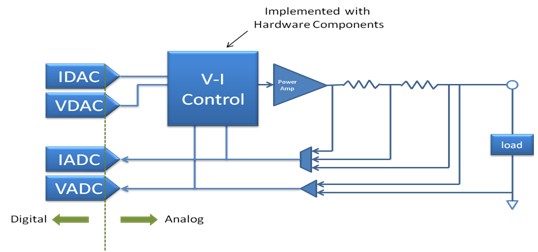

SMUの制御ループは、2つの閉ループを重ね合わせたものです。1つは電流用、もう1つは電圧用です。図2aは従来型SMUアーキテクチャの概念図を示しています。

図2a.従来型SMUアーキテクチャの簡略図。アナログハードウェアコンポーネントを用いて制御ループ (V-I制御) を実装するので、構成可能性は極めて限定的なものとなる点に留意してください。

V-I制御では電圧と電流の設定値が規定されており、その閉ループフィードバックにより、出力電圧と電流を正確に制御して、こうした設定値に一致させることができます。この制御ループはすべて、増幅器などのアクティブアナログハードウェアで実装されます。高精度の測定を可能とするために、フィードバック信号は、A/Dコンバータ (ADC) によってでも読み取られます。このアーキテクチャの補正を変更するには、リアクタンス素子を1つずつ追加する必要があります。スイッチを用いることで、ある程度はプログラムによる調整が行えますが、調整範囲が限定されます。せいぜい、数少ない選択肢の中から構成を1つ選ぶことぐらいでしょうか。所与の負荷に合わせてSMUの応答を最適化するには十分とは言えません。では、どうすれば任意に構成できる制御ループを実現できるのでしょうか?その答えは、図2bの新しいアーキテクチャに示されています。

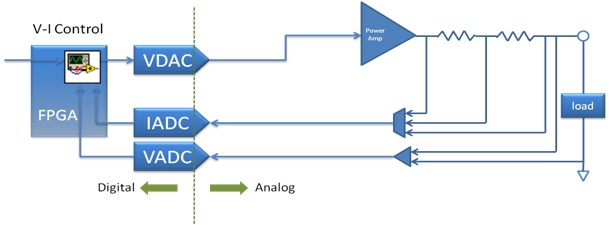

図2b.新しいNI SMUアーキテクチャ。制御ループ (V-I制御) が、フィールドプログラマブルゲートアレイ (FPGA) 内のデジタルドメインに移動したことに留意してください。

この新たなアーキテクチャでは、V-I制御がデジタルドメインに移行し、FPGAの内部に常駐しています。このデジタル制御ループは、アナログ制御ループとは異なり、ソフトウェアで完全に構成が可能であるので、負荷に対して、迅速に制御ループの最適化を行い、理想的な応答を得ることができます。このSourceAdaptテクノロジにより、制御ループを極めて多くの用途で使用できるようになります。つまり、あらゆる負荷に対して、SMU応答をカスタマイズできるということです。

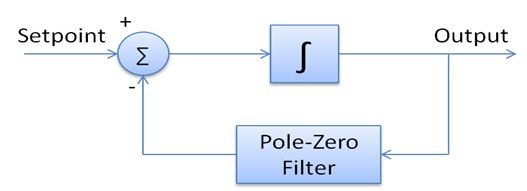

図3.新しいデジタルV-I制御の実装

V-I制御には、DC確度とループの全般的な調整を提供する積分器と、カスタム補正を可能にする極-零点フィルタが含まれています。これらのブロックは、ユーザーによって構成が行うことができ、構成の範囲は、アナログ制御ループでは不可能なレベルです。また、高速ADCとDACを活用し、更に、FPGAの処理能力を利用することで、ループ全体で高精度のソース測定機器を完璧に処理できます。その結果、性能に関して妥協のない任意に構成できるアーキテクチャが完成します。

SourceAdaptテクノロジの基礎となるアーキテクチャについて

SourceAdaptテクノロジの特長である新しいアーキテクチャは、以下の2つの方法で伝達関数を調整できます。1つは積分器のゲイン帯域幅積 (GBW) を調整する方法、もう1つはフィードバック補償器を位相進相補償器もしくは位相遅相補償器として用い、伝達関数における任意の周波数に極と零点のペアを追加する方法です。

ゲイン帯域幅の調整

出力パスの積分器は、ボードマグニチュードプロット (ゲインマージン[1]) と位相マージン[2]プロット上で、オペアンプと同様の開ループ伝達関数を提供します。

図4a.積分器の開ループ伝達関数 (ゲインマージン:左、位相マージン:右)

図4b.無負荷出力での対応する1 Vステップ応答 (図4aの伝達関数の場合)

ループのGBW (積分器のゲイン) を調整することで、動作させるループ全体の応答を調整することができます

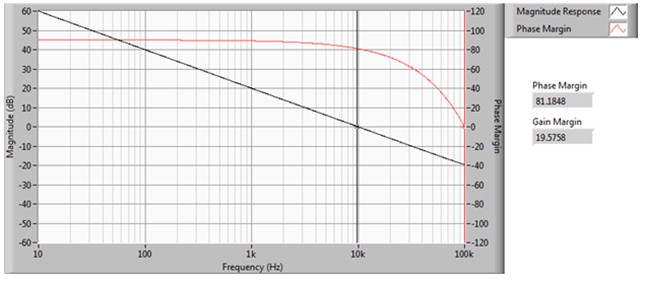

- たとえば、GBWが3 kHz、位相マージンが87.34の場合では、より遅く、より安定します (図5aおよび5bを参照)。

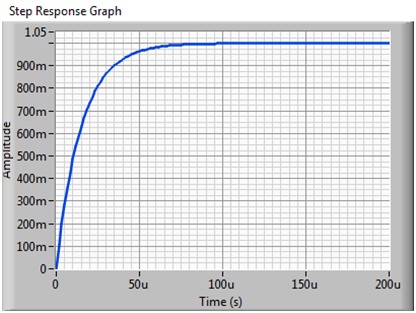

- たとえば、GBWを20 kHzとすると、速くなります (図6aと図6bを参照)。

図5a.GBWが3 kHz、位相マージンが87.34の場合、低速ではあるものの、安定性の高い応答が得られます

図5b.無負荷出力での対応する1 Vステップ応答 (図5aの伝達関数の場合)

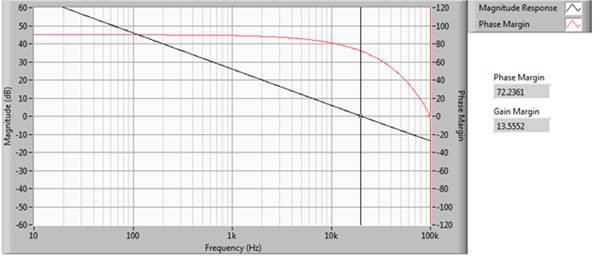

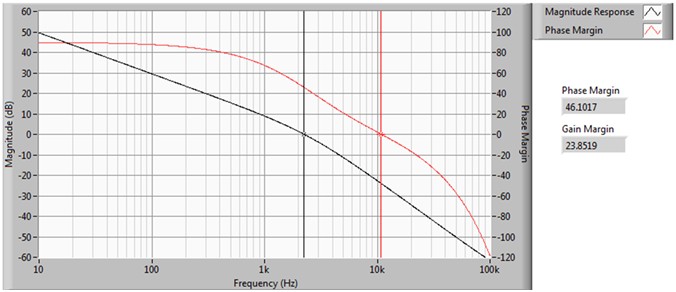

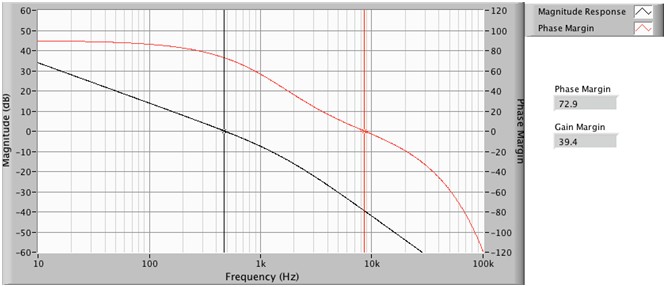

図6a.GBWが20 kHz、位相マージンが72.23の場合、高速の応答が得られます

図6b.無負荷出力での対応する1 Vステップ応答 (図6aの伝達関数の場合)

無効負荷による処理

ループ速度を低下させるだけで安定性を損なう、扱いにくい無効負荷にも対応可能です。図7aと図7bは、コンデンサを負荷として用いた場合の制御ループの特性を示しています。コンデンサは、キャパシタンスと出力段のシャント抵抗値に反比例する周波数で極を発生させ、ゲインと位相の双方に影響を与えます。図7aは0.1 μFのコンデンサを用いた場合の開ループの周波数応答、図7bはこの条件におけるステップ応答を示しています。

図7a.0.1 μFのコンデンサを負荷として使用した場合、開ループ伝達関数は、かろうじて安定している状態となります。

図7b.0.1 μFのコンデンサを負荷として使用した場合の対応する1 Vステップ応答

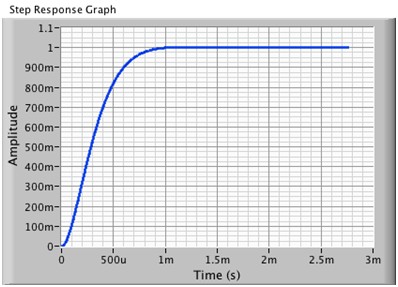

図7bからわかるように、応答は減衰不足で、オーバーシュートが発生しており、長い整定時間を要しています。GBWを調整することにより、このシステムの動作が改善します。オーバーシュートを完全に無くすことを最重視する場合には、オーバーシュートを発生させずに応答が得られるようになるまで、ループ速度を下げても良いです。図8aと図8bは、オーバーシュートを完全に無くすために、GBWを500 Hzに設定して、応答速度を下げた結果を示しています。

図8a.500 Hz GBWの開ループ伝達関数 (負荷:0.1 μFコンデンサ)

図8b.500 Hz GBWでの対応する1 Vステップ応答 (立ち上がり時間~1 ms)

オーバーシュートはなくなっていますが、今は、システムの応答が非常に遅いです。最適な応答を得るには、伝達関数の2つ目の調整方法を使用します。すなわち、フィードバック補償器を (位相進相補償器または位相遅相補償器として) 使用する方法です。

フィードバック補償器の使用

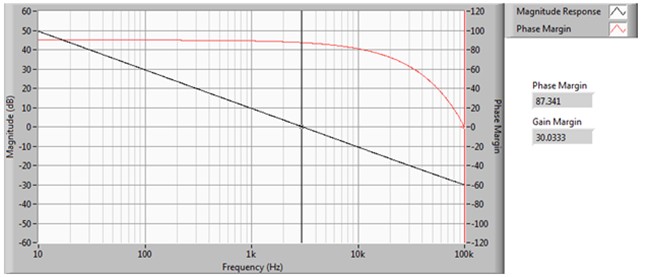

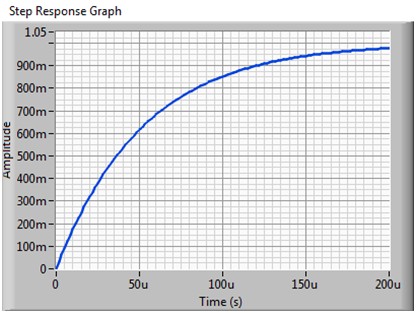

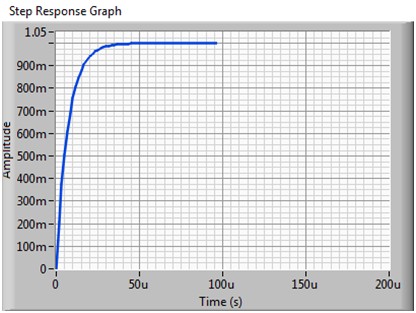

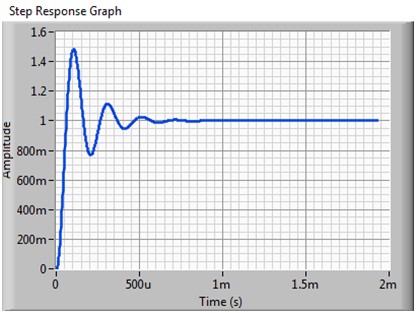

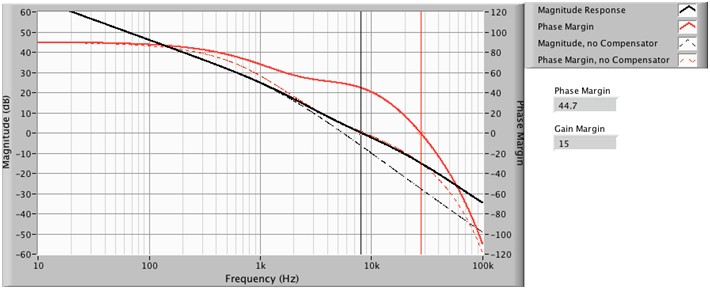

SourceAdaptテクノロジでは、応答を最適化する2つ目の手段として、フィードバック補償器を使用します。上記セクションの例に続いて、オーバーシュートと発振を防ぎながら、立ち上がり時間の短縮を目指します。これは、フィードバック補償器を用いて、コンデンサが発生させた極の影響を相殺することで実現します。この制御方法を用いれば、高い安定性を維持しながら、GBWを一層高め、立ち上がり時間を短縮することが可能です。図9aは、GBWを20 kHzまで高めて、補償器を使用した場合と使用しない場合の振幅と位相応答を比較しています。

図9a.補償器を使用した場合と使用しない場合の開ループ伝達関数 (GBW:20 kHz、負荷:0.1 μFコンデンサ)

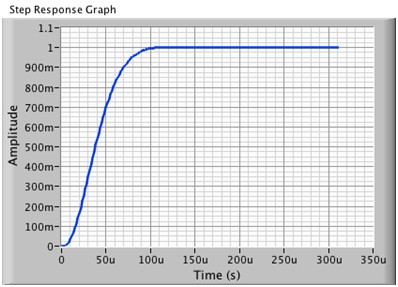

図9b.20 kHz GBWと補償器での対応する1 Vステップ応答 (立ち上がり時間~100 μs)

図9bで見られるように、応答は理想的です。立ち上がり時間が10分の1に短縮され、オーバーシュートがなく、約45度の位相マージンで安定性に優れています。

SMUで理想的な応答を実現

負荷がソースメジャーユニット (SMU) 制御ループの伝達関数に直接影響するので、理想的な応答を実現するには、所与の負荷について、構成可能性が求められます。NI SourceAdaptテクノロジを使用すれば、あらゆる負荷に対するSMUの応答をカスタマイズできますので、立ち上がり時間を極力減らし、オーバーシュートや発振のない理想的な応答を実現できます。これは、潜在的なテスト対象デバイスの損傷やシステムの安定性に関する問題のリスクなしに、テストをより迅速に実装できることを意味します。

まとめ

本書では、さまざまな負荷について理想的な応答を得る上でSMU伝達関数が構成可能となる必要性と、新しいNI SourceAdaptテクノロジで完全な構成可能性を実現する方法について説明します。SourceAdaptテクノロジを導入すると、SMUの応答をあらゆる負荷に対して完全にカスタマイズして、立ち上がり時間を最小限に抑え、オーバーシュートや発振のない理想的な応答が得られます。事故による破損や、システムの安定性にかかわる問題を回避し、DUTをより短時間でテストできます。

SourceAdaptテクノロジは、LabVIEWグラフィカル開発環境のFPGAへの拡張であるNI LabVIEW組込技術の最新の進化によって実現したものです。

[1] ゲインマージンは、システムが不安定になるまでに、開ループゲインにある余裕として定義されます。

[2] 位相マージンは、閉ループシステムが不安定になるまでに、開ループ位相シフトにある余裕として定義されます。