FPGA VisionでのNI Vision Development Moduleの使用の概要

概要

FPGAテクノロジとNI Vision Development Moduleを使用すれば、カメラから入力された画像に高速FPGA (Field-Programmable Gate Array) 処理を施すことができます。FPGA処理は、特に、画像の入力から処理までのレイテンシを抑える必要がある用途で役に立ちます。このドキュメントでは、FPGAを使用した画像処理の概要と、典型的なユースケースを紹介しています。

内容

FPGAプログラミングの概要

NI LabVIEW FPGAモジュールは、LabVIEWグラフィカルプログラミング環境を自然な形で拡張したものです。VHDLなどの低レベル言語を使用せずに、複雑なFPGAプログラミングを行うことができます。LabVIEWを扱った経験があれば、LabVIEW FPGAの操作も容易に習得できます。これによって、FPGAプログラミングに必要なアプリケーションでの開発作業に要する時間が大幅に短縮され、カスタムハードウェアの設計が不要になります。HDLでプログラミングする代わりに、LabVIEWのブロックダイアグラムでアプリケーションを作成し、LabVIEW FPGAでグラフィカルコードをコンパイルして、FPGAハードウェアに実装します。

FPGAでの画像処理

多くの画像処理アルゴリズムは本質的に並列的であるため、FPGAによる実装に適しています。このようなアルゴリズムで扱われるのはピクセル、ライン、および関心領域に対する操作で、パターンなどの高レベルの画像情報は不要です。このような機能を、画像の中の小さなビット領域と複数の領域に対して同時に実行することができます。画像データの処理にはセントラルプロセッサが使用されないため、画像データをFPGAに並列的に渡して同時に処理できます。NI Vision Development Moduleには50種類以上の画像処理機能が搭載されており、NI LabVIEW FPGAモジュールと組み合わせて使用することでFPGA上で画像を処理できます。 FPGA上で使用できるVision Development Moduleの画像処理機能の例を、以下に紹介します。

前処理

| 特徴抽出

測定

|

Vision Development ModuleのFPGA機能の概要

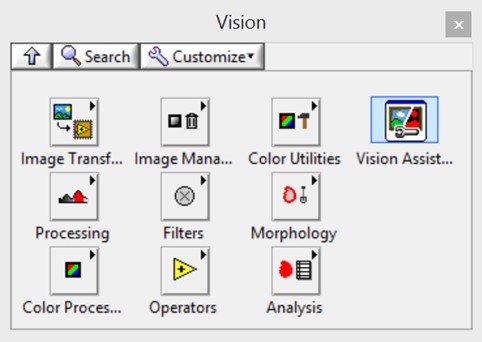

Vision Development ModuleをNI LabVIEW FPGAモジュールにインストールすると、VisionパレットにFPGA画像処理アプリケーションで使用できる機能が表示されます。

図1. VisionパレットにFPGA画像処理アプリケーションで使用できる機能が多数表示される

VisionパレットにはFPGAとCPU間で画像をストリーミングできる画像転送VIが含まれています。セクション2「FPGA Visionのユースケース」では、さまざまなユースケースを紹介し、それがCPUとの間での画像転送に必要となる理由について説明しています。

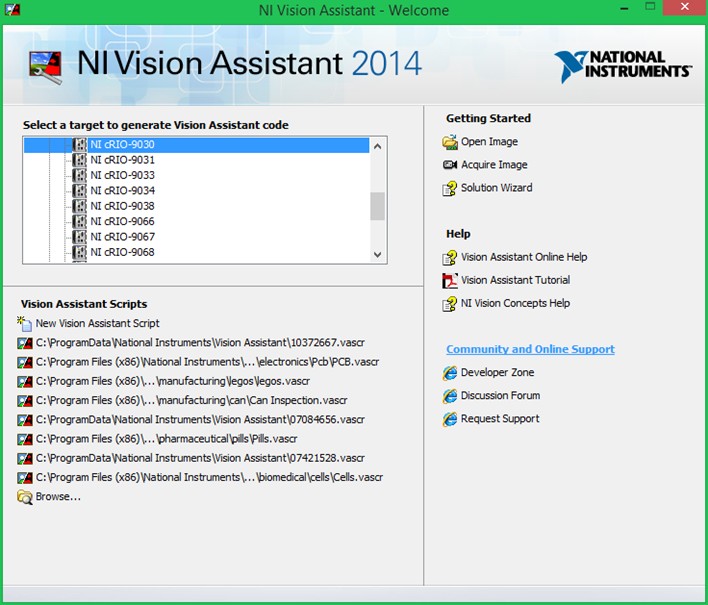

NI Vision Development Moduleに含まれるVision Assistant Express VIでは、LabVIEW FPGA画像処理コードをハンドシェイクと同期によって自動生成できるため、低レベルの同期コードを作成する必要がなくなります。Vision AssistantはLabVIEWブロックダイヤグラムから開くこともできますが、スタンドアロンプログラムとして起動して、特定のNIハードウェアを対象としたLabVIEWプロジェクトを作成することもできます。

図2. Vision Assistantをスタンドアロンプログラムとして開いて、特定のハードウェアターゲット向けのコードを生成

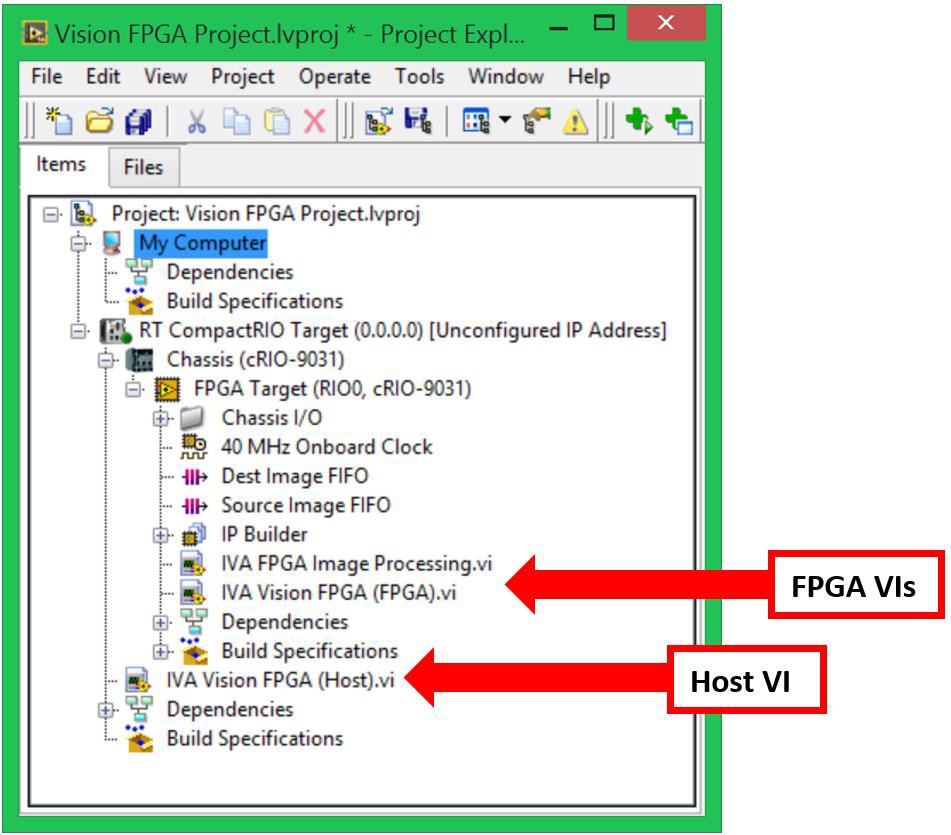

ハードウェアターゲットを選択すると、Vision Assistantが画像処理スクリプトに必要なFPGAターゲットリソースの量を見積もります。次にVision Assistantは、画像の処理と転送のためのホストVIとFPGA VIを含むLabVIEWプロジェクトを生成します。

図3. 画像処理スクリプトの作成が終わると、Vision Assistantによって、画像の処理と転送に必要なハードウェアターゲット、ホストVI (指定した場合)、FPGA VIを含むLabVIEWプロジェクトが自動的に生成される

FPGA Visionのユースケース

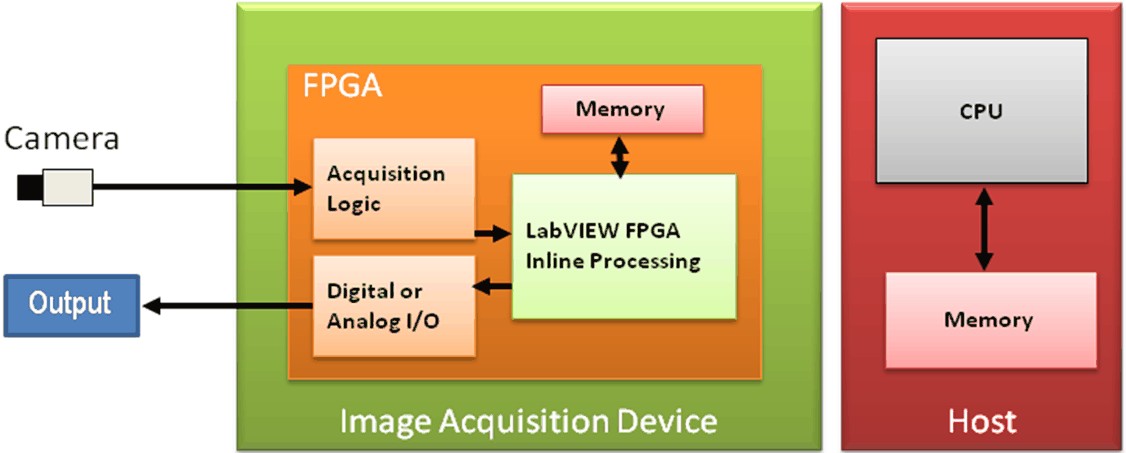

ユースケース1:FPGAのみの処理で高速制御

FPGA画像処理によって、画像解析に必要な計算リソースを少なくすることができます。FPGAはハードウェアリソースのため、CPUを解放して、他の処理をさせることができます。解析を実行する際にCPUの介入が不要になるため、画像の処理から制御信号の出力までのレイテンシが大幅に短縮されます。図4に、FPGAを使用してCPUのリソースを解放する方法の例を示しています。このケースでは、画像の処理から出力信号の生成まで、すべてがFPGAによって実行されます。これにより、システムレイテンシが最小限に抑えられ、制御信号を迅速に生成することができます。

図4.すべての処理がターゲットのFPGA上で実行されるため、解放されたCPUで他のタスクを実行でき、システムレイテンシを最小限に抑えられる

このユースケースの例としては、高速ソート、視線トラッキング、レーザーアライメントなどがあります。 FPGAのみの処理をフレームグラバに実装することで、入力される画像データのパス上にFPGAを直接配置することができます。Camera LinkフレームグラバとCamera Linkアダプタモジュールの例を示します。

図5. Camera LinkフレームグラバとCamera Linkアダプタモジュールは、どちらもFPGAが画像パス上に配置されるため、オンボードでの前処理や高速制御の用途に適している

ユースケース2:FPGA処理

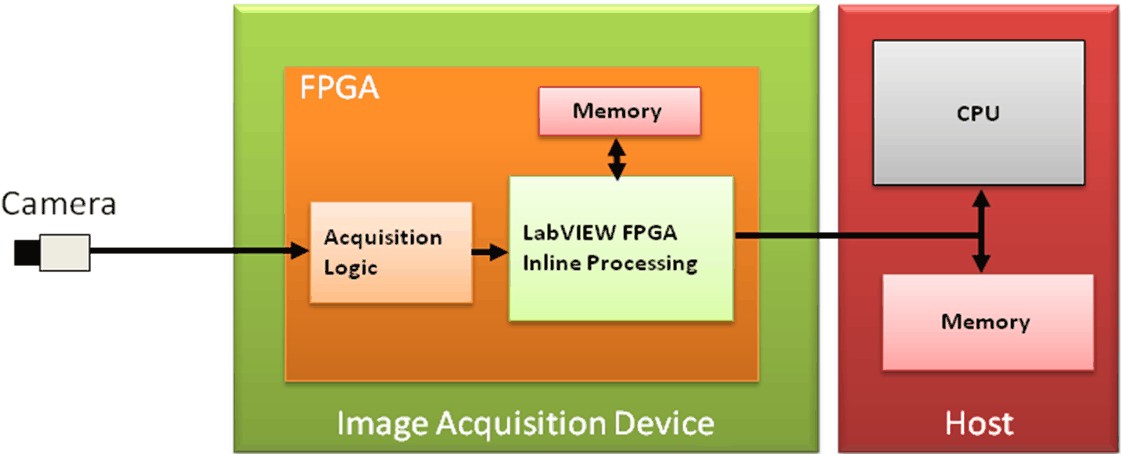

FPGAによるビジョンシステムプロセッサを使用した追加処理を実行できます。図6は、FPGAで前処理を行い、CPUではもっと高度な処理アルゴリズムを実行する方法を示しています。この例では、FPGAがフィルタ処理やエッジ検出などのビットレベル処理を実行します。次に、前処理を施された画像がCPUに送信され、パターン認識などの画像レベル処理が実行されます。この例でも、CPUで実行される機能の数が従来型ビジョンシステムの場合よりも少なくなるため、システムレイテンシが低く抑えられます。

図6.FPGAで画像入力と前処理が実行された後、画像データがCPUに渡され、CPUでパターンマッチングや分類といったさらに複雑な画像解析が実行される

FPGA画像処理は、高速ビットレベル処理が必要な用途で特に役立ちます。FPGAが画像データを受け取り、高速オンボードクロック (最高クロック速度100 MHz) を使用して個々のビットを処理します。データの転送およびハードウェアでの処理が1回のクロックサイクルで実行されます。多数のビジョンアルゴリズムを複数の反復タスクに分割した後、さらにそのタスクを分割して、FPGAで並列処理できます。

このタイプのアーキテクチャが適用できる例としては、表面検査、Web検査、光コヒーレンス断層撮影法 (OCT) などの用途が挙げられます。 図5に、FPGA前処理に対応するフレームグラバの例を2つ示しています。

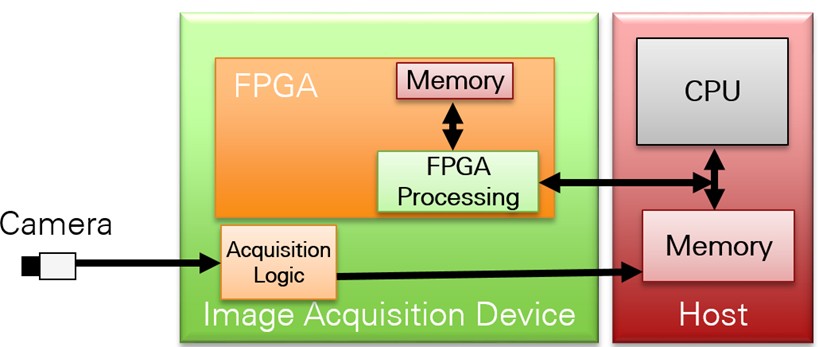

ユースケース3:FPGAコプロセッシング

画像処理アルゴリズムが複数のステップで構成されている場合もあります。その中でも2値化などのステップは、FPGAに実装することができます。パターンマッチングなどのステップは、多くの場合、CPUの方が適しています。このような場合、FPGAを使用してプロセッサの負担を軽減することができます。 図7に示すように、CPUに送られた入力画像はピクセルごとにFPGAにストリーミングされ、ビットレベルで処理されます。FPGA上で処理されたピクセルがCPUに送り返されて、さらに処理が加えられる場合があります。

アルゴリズムの処理がFPGA上で完結する場合、ピクセルをCPUに送り返す必要はありません。その場合、画像処理アルゴリズムの結果に基づいてFPGAを使用して出力を生成するか、処理結果をCPUに送り返して、システムの他の部分で使用できるようにします。結果として出力されるデータの例としては、距離測定、粒子のカウントなど、画像処理ステップで得られる任意の結果が考えられます。FPGAコプロセッシングによってCPUで実行される機能の数を最小限に抑えることで、システムレイテンシが低減されます。

図7. 画像入力と前処理がFPGA上で実行された後、画像データがCPUに送られ、CPUがパターンマッチングや分類といったさらに複雑な画像解析を実行する

FPGAコプロセッシングは、CompactRIOコントローラに加え、Camera LinkフレームグラバやCamera Linkアダプタモジュールにも実装できます。

FPGAコプロセッシングが有益な用途の例としては、品質検査における粒子のカウントがあります。この用途では、粒子のカウントをFPGAで実行し、粒子の数とそのサイズを判断します。次にその情報をプロセッサに共有することで、オペレータにそれを表示したり、別のプロセスへの入力として使用したりできます。

まとめ

まとめると、高速操作と並列処理というFPGAの特性を利用することで、画像処理に要する時間を減らし、システムレイテンシを短縮してスループットの増大につなげることができます。さらに、FPGAで画像処理を行うことで、高速ソーターなどのシステム向けコントローラで入力画像に基づく意思決定を迅速に下せるようになります。また、組込処理におけるイノベーションの結果、幅広いマシンオートメーション用途で3Dビジョンが用いられるようになっています。