NI does not actively maintain this document.

This content provides support for older products and technology, so you may notice outdated links or obsolete information about operating systems or other relevant products.

This guide provides information and guidance for migrating existing LabVIEW Communications 1.1 applications to LabVIEW Communications 2.0 for General Projects. If you prefer to migrate over an existing application, this guide addresses known issues that may arise in the process. It is recommended to start with a new project in 2.0 and duplicate the original project in the newer version.

This document covers LabVIEW Communications 1.1 to 2.0 Migration Guide for General Projects.

The guide is made up five documents covering the following topics:

Each section discusses the required steps to migrate that specific type of project. For example, if you would like to migrate a USRP streaming project, you should navigate to the USRP Projects section for guidance. If your project does not fall into the first three categories listed above, you should navigate to the General Projects section. Each section is meant to be self-contained and used independently of the others, so redundant information may be included in multiple sections.

Note: Always back up a copy of the original project before attempting any migration efforts.

This section describes the necessary changes needed if you want to reuse a general project that was created based on projects in LabVIEW Communications 2.0. For details specific to USRP or the Application Frameworks, refer to those sections.

This section includes the following parts:

It is generally recommended that project migration should be limited to a single target at a time to reduce complexity and to make migration efforts easier. If a project does contain multiple targets, there may be issues if the same resource name is shared between these targets. For example, top-level VIs, subVIs, or common resource names that are shared between targets. To address this, remove all but one of the targets, migrate, and, if necessary, add the additional targets back into the newer project. Additionally, any broken VIs must be fixed by manually selecting the correct FPGA resources.

Projects using 579x targets will have broken VIs that reference the “Sample Clock”. This clock has been renamed to the “Data Clock” and must be reconfigured.

For additional details, or information on migrating one of the NI-579xR streaming projects, see the FlexRIO Projects topic.

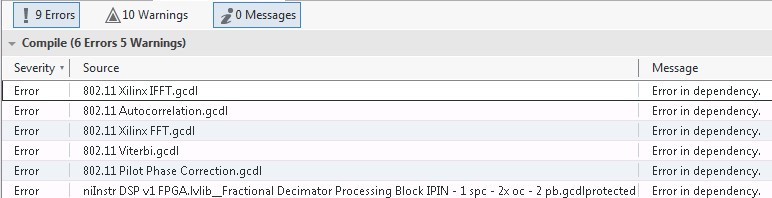

Xilinx IP needs to be reconfigured due to the new Vivado version used in LabVIEW Communications 2.0.

To find the affected files and make the necessary updates, follow these steps:

Figure 107: Example error list showing affected files for Xilinx IP Core reconfiguration

Figure 108: How to reconfigure a Xilinx IP Core (1)

Figure 109: How to reconfigure a Xilinx IP Core (2)

Figure 110: "Not Ready" warning because Xilinx tool is processing the IP in the background

The FIFO resource names in the Host VIs which interface with DMA FIFOs must be updated. In LabVIEW Communications 2.0, the FIFO resource contains additional prefixes for the FPGA resource file name along with the FIFO name itself. For example, in the USRP Streaming projects, “Rx Stream 0” becomes “USRP Resources.grsc\Rx Stream 0.” Because of this, all FIFO node instances (Start/Stop, Configure, and Read/Write), along with any FPGA reference terminals, must be updated.

If the host is not updated correctly, runtime errors can occur after migrating over a previous project. These errors may persist even after a recompile in the newer version. A typical error is shown in Figure 111.

Figure 111: Typical Error if Host Not Updated

Note: The bitfile may need to be recompiled in version 2.0 to make use of any changes in resource files that may have been added during migration of the project. This must be done prior to any host-side changes that reference that bitfile.

To update FPGA refnums, complete the following steps:

Note: If the application uses FPGA terminals, or constants, then they may need to be updated to the latest bitfile.

1. Select the FPGA reference and click Configure in the right-hand rail.

Figure 112: Configure Dialog in Right-Hand Rail

Figure 113: Import Bitfile

To update DMA FIFO nodes, complete the following steps:

Figure 114: Select Appropriate Resource

Several changes have been made to the USRP API. For a list of these changes, and needed adjustments, see the Host API section under the USRP Projects topic.

The USRP RIO 40 MHz target will be deprecated in future versions of LabVIEW Communications. Previous projects built for these targets will still be usable in version 2.0 but you should consider migration efforts in future designs. Please see the USRP Projects topic for instructions on how to update to the latest USRP targets.

Continue onto other sections of the LabVIEW Communications 1.1 to 2.0 Migration Guide for:

The LabVIEW Communications product documentation provides detailed information in addition to the tasks discussed in this guide. Hardware manuals also contain valuable information about the features and performance characteristics of NI RIO devices.

The main NI support page, ni.com/support, provides quick access to manuals, KnowledgeBase documents, tutorials, example code, community forums, technical support, and customer service.