Der Controller für FlexRIO: Ein ausführlicher Einblick in verteilbare Messgeräte

Überblick

Der Controller für FlexRIO ist eine kommerzielle Standardlösung (Commercial off-the-shelf, COTS) von NI für Anwendungen, die leistungsstarke I/O und Echtzeit-Signalverarbeitung in einem kompakten, eigenständigen Formfaktor erfordern. Dank der Kombination aus modularen I/O, einem mit LabVIEW programmierbaren FPGA und einem integrierten Prozessor können Ingenieure die Hardware für spezifische Anwendungen vollständig neu konfigurieren, wodurch sich der Controller für FlexRIO von den meisten COTS-Geräten abhebt. Der Controller verfügt über die gleichen Adaptermodule, FPGAs und Software-Erfahrungen wie FlexRIO on PXI, was ihn zu einer idealen Lösung für die Bereitstellung von auf der PXI-Plattform entwickelten Lösungen macht. Trotz der vielen Gemeinsamkeiten mit FlexRIO in PXI zielt das Gerät auf Embedded-Anwendungen ab, bei denen kleinere, leichtere und stromsparende Lösungen bevorzugt werden.

Inhalt

- Interne Architektur

- FlexRIO-Adaptermodul-Schnittstelle

- FPGA

- Serielle Hochgeschwindigkeitsübertragung

- Takte

- Prozessor

- Konnektivität

- Physikalische Verpackung

- Zusammenfassung

- Nächste Schritte

Abbildung 1: Der Controller für FlexRIO ist ein eigenständiges Erfassungs- und Signalverarbeitungsgerät mit hochleistungsfähiger I/O und einem großen Kintex-7 FPGA.

Interne Architektur

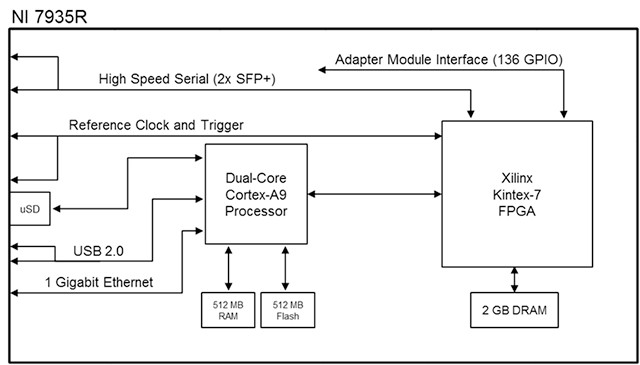

Der Controller für FlexRIO wird auf einem großen Kintex-7 FPGA aufgebaut, der mit einer modularen I/O-Schnittstelle, einem Prozessor und 2 GB DDR3 DRAM verbunden ist. Mit über 400.000 logischen Sektoren, 1540 Sektoren für die Verarbeitung von Digitalsignalen (DSP) und 28 MB BRAM lässt sich ein beträchtlicher Teil der Signalverarbeitung auf d0em FPGA implementieren. Der Dual-Core-ARM-Prozessor sorgt für Netzwerk- und USB-Konnektivität für den Anschluss an andere Geräte sowie für Onboard-Speicher zur Parameter- und Datenaufzeichnung.

Eine Kombination aus einem großen FPGA und einem stromsparenden Prozessor ist besonders wertvoll, wenn die meisten Algorithmen auf dem FPGA implementiert werden können, wodurch der Dual-Core ARM-Prozessor für die Konfiguration beim Einschalten und die Systemüberwachung verwendet werden kann. Mithilfe dieser Architektur werden die intelligenten Funktionen näher an die Grenzen herangeführt, wo ein Hochleistungs-FPGA verwendet werden kann, um Hochgeschwindigkeitsdaten in aussagekräftige Informationen umzuwandeln.

Abbildung 2: Dank des großen Kintex-7 FPGA eignet sich der Controller für FlexRIO ideal für Anwendungen, bei denen Signalverarbeitungsalgorithmen in Echtzeit ausgeführt werden müssen.

Die Modelle NI 7932R und NI 7935R verfügen über zwei serielle Hochgeschwindigkeits-Ports für das Streamen von Daten direkt aus dem FPGA über 10-Gigabit-Ethernet-UDP, Xilinx Aurora oder benutzerdefinierte Protokolle, wenn Daten mit hoher Bandbreite an einem zentralen Speicherort aggregiert werden müssen.

FlexRIO-Adaptermodul-Schnittstelle

Abbildung 3: Das NI 5772 ist ein 2-Kanal-Hochgeschwindigkeits-Digitizer-Adaptermodul, das sowohl bei Zeit- als auch bei Frequenzbereichsmessungen eingesetzt wird.

Weitere Informationen zum FlexRIO Module Development Kit

FPGA

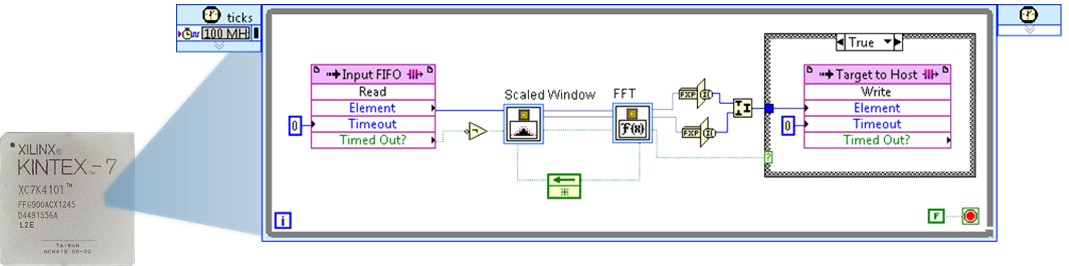

Benutzer können den FPGA mithilfe der Systemdesignsoftware LabVIEW und dem LabVIEW FPGA Module programmieren, wodurch sowohl eine LabVIEW-basierte Algorithmenerfassung als auch eine VHDL/Verilog-Integration möglich ist. Vorhandene LabVIEW-Bibliotheken lassen sich zur Entwicklungsbeschleunigung mit Datenbewegungsinfrastruktur, fortschrittlichen Signalverarbeitungsfunktionen wie einer Ultra-Breitband-FFT (Fast Fourier Transformation) und parallelen Resampling-Algorithmen sowie verwaltetem DMA-Streaming zum Host einsetzen. Schaltungen können in LabVIEW simuliert werden, um sie anschließend lokal oder über den NI Compile Cloud Service zu kompilieren. Nachdem die FPGA-Bitdatei mit LabVIEW FPGA und Xilinx Vivado kompiliert wurde, werden die Bitdateien über LabVIEW auf dem Entwicklungsrechner bereitgestellt. Dies geschieht mittels Echtzeitanwendungen, die mit LabVIEW oder C/C++ erstellt wurden und auf dem Controller ausgeführt werden, oder über den Flash-Speicher In vielen FlexRIO-Schaltungen wird die Logik mit Hunderten von Megahertz getaktet, was die Einhaltung von Timing-Bedingungen erschweren kann. NI rät neueren LabVIEW-FPGA-Entwicklern, sich zunächst im Handbuch High-performance LabVIEW FPGA Developers Guide über empfohlene Methoden zur Timing- und Ressourcenoptimierung zu informieren.

Abbildung 4: LabVIEW vereinfacht die FPGA-Programmierung durch die Bereitstellung einer integrierten, grafischen Entwicklungsumgebung für das Design, die Simulation, die Fehlerbehandlung und die Bereitstellung.

Ingenieure können zwischen zwei FPGA-Optionen auswählen: einem Xilinx Kintex-7 K325T und einem größeren K410T. Für die Erstentwicklung bietet die Verwendung des größten verfügbaren FPGAs erhebliche Vorteile. Dadurch können nicht nur Funktionen während der Entwicklung flexibel hinzugefügt werden, sondern es besteht auch die Möglichkeit, denselben Programmcode auf einem größeren FPGA zu kompilieren, was in der Regel die Kompilierzeiten während des Entwurfs verkürzt und eine schnellere Iteration ermöglicht. Mit den von NI bereitgestellten I/O-Schnittstellen kann LabVIEW-FPGA-Programmcode, der für ein Hardwareziel geschrieben wurde, schnell auf andere NI-Hardware portiert werden, auch auf Hardware mit anderen FPGAs und I/O-Funktionen.

FPGA | Sektoren | LUTs | Flipflops | DSP-Sektoren | Block-RAM (kb) | Onboard-DRAM |

Kintex-7 K410T | 63.550 | 254.200 | 445.200 | 1540 | 28.620 | 2 GB |

Kintex-7 K325T | 50.950 | 203.800 | 407.600 | 840 | 16.020 | 2 GB |

Abbildung 5: Der Controller für FlexRIO bietet zwei verschiedene Xilinx FPGAs, so dass der Benutzer den richtigen Baustein für seine Anwendung auswählen kann. NI empfiehlt die Verwendung des größten FPGAs für die anfängliche Entwicklung, noch bevor versucht wird, das Design für die Bereitstellung zu optimieren.

DRAM ist eine Ressource, die in mehrstufigen Signalverarbeitungsalgorithmen und bei der Datenpufferung über nicht deterministische Busse einen erheblichen Mehrwert bietet. Um diese Art von Operationen zu ermöglichen, ist bei allen drei Varianten des Controllers für FlexRIO eine DDR3-DRAM-Bank mit 2 GB an das FPGA angeschlossen. Die DRAM-Schnittstelle verfügt über eine Datenbreite von 512 Bit und kann mit Taktraten von bis zu 166 MHz effizient angesteuert werden. Daraus ergibt sich eine maximale theoretische Bandbreite von 10,6 GB/s zwischen dem DRAM und dem FPGA. Lese- und Schreibvorgänge mit zufälligem Zugriff senken den DRAM-Durchsatz. NI hat jedoch sequenzielle Lese- und Schreibvorgänge mit über 9 GB/s getestet. DRAM kann mithilfe des LabVIEW-Speicherobjekts in LabVIEW FPGA oder als FIFO mithilfe der Memory Instrument Design Library (IDL) adressiert werden.

Serielle Hochgeschwindigkeitsübertragung

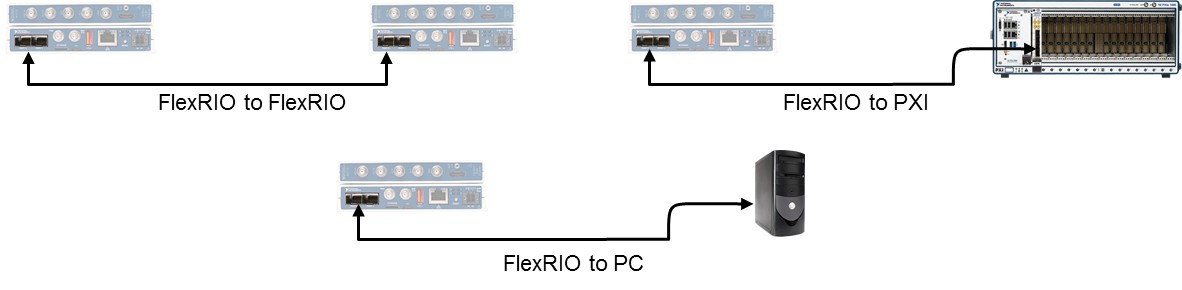

Um Anwendungen zu ermöglichen, die nach dem Erfassen und Verarbeiten von Signalen ein Datenstreaming mit hoher Bandbreite erfordern, sind die Geräte NI 7932R und NI 7935R mit zwei seriellen Hochgeschwindigkeits-Transceivern ausgestattet, die jeweils Daten mit bis zu 10,3125 Gb/s streamen können Diese Technologie basiert auf Multigigabit-Transceivern (MGTs) von Xilinx GTX, die vom FPGA zu zwei SFP+-Anschlüssen auf dem Frontpanel geleitet werden. NI bietet LabVIEW-FPGA-Beispielprojekte für 10-Gigabit-Ethernet-UDP- und Xilinx-Aurora-Protokolle an. Mit VHDL vertraute Benutzer können andere Protokolle wie Serial RapidIO oder benutzerdefinierte Protokolle implementieren.

Zu den Beispielen für Daten-Streaming-Konfigurationen, die diese seriellen Hochgeschwindigkeits-Ports verwenden, gehören die gemeinsame Datennutzung zwischen mehreren Controllern mithilfe von Xilinx Aurora, das Daten-Streaming zurück zu PXI mithilfe von Aurora oder 10-Gigabit-Ethernet und das Daten-Streaming zu einem Desktop-PC, Datenaufzeichnungsgerät, NAS (Network Area Storage) oder Server mithilfe von 10 Gigabit Ethernet.

Abbildung 6: Die seriellen Hochgeschwindigkeits-Ports sind für das Streamen von Daten mit hoher Bandbreite an eine Vielzahl von Geräten vorgesehen. Die Kommunikationsprotokolle werden in LabVIEW FPGA festgelegt und jeder Transceiver kann mit bis zu 10,3125 Gb/s ausgeführt werden.

Erfahren Sie mehr über serielle Hochgeschwindigkeitstechnologie in NI-Produkten

Takte

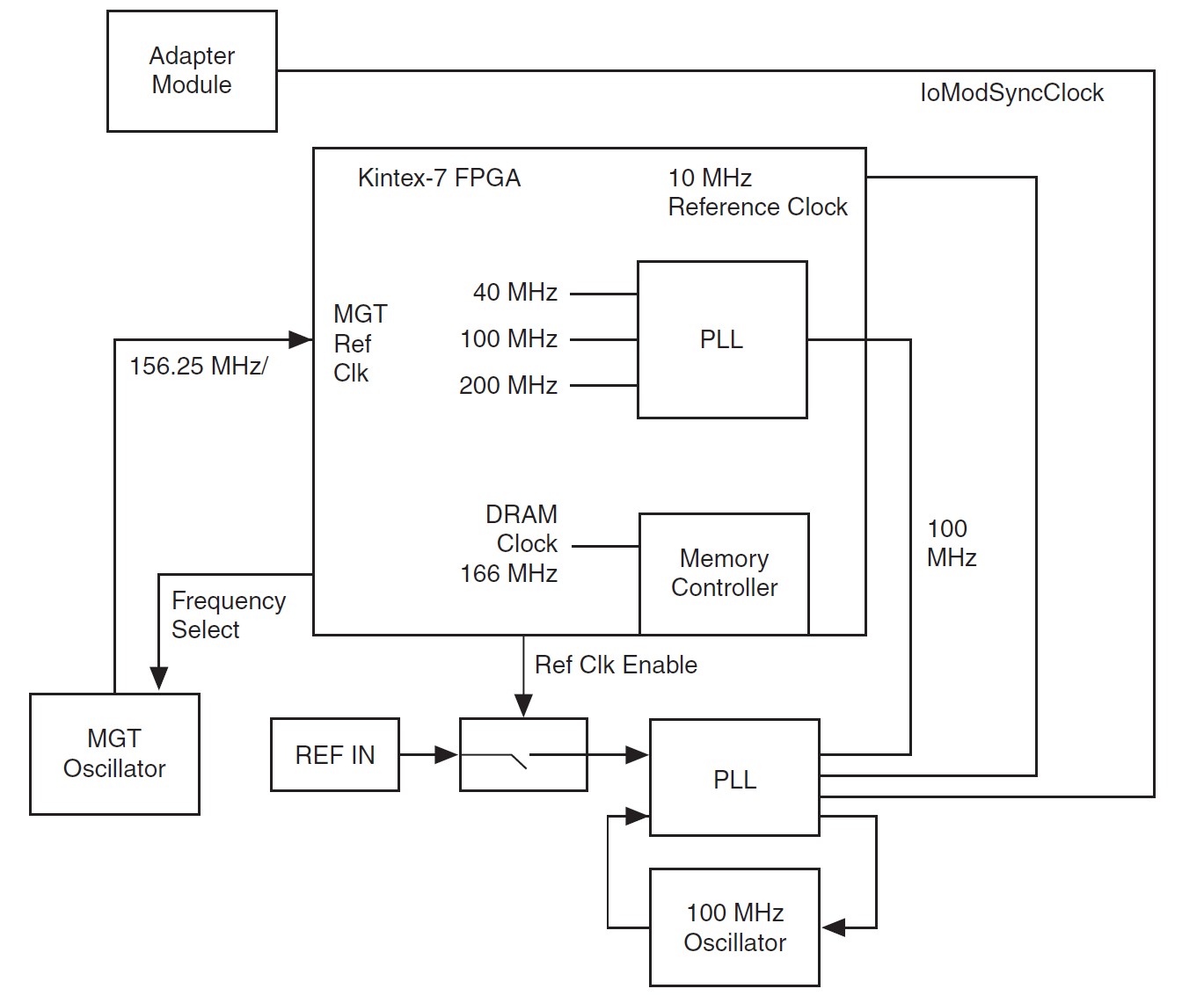

Ingenieure, die an FPGAs und Hochgeschwindigkeits-I/O arbeiten, investieren oft viel Zeit in die Implementierung der richtigen Takt- und Synchronisationsarchitektur. Zur Vereinfachung dieses Prozesses bietet der Controller für FlexRIO eine Reihe von Taktoptionen, darunter einen externen 10-MHz-Referenztakteingang, eine bidirektionale Trigger-Leitung, einen integrierten 100-MHz-Oszillator und die Möglichkeit der Synchronisierung mit einer externen Referenz. Um eine synchrone Datenübertragung zwischen dem I/O-Modul und dem FPGA zu gewährleisten, wird die Sample-Taktung des I/O-Moduls gemeinsam mit dem Controller für die FlexRIO-Taktung verwendet. Zusätzliche Takte können auch auf dem FPGA hergeleitet werden.

Abbildung 7: Mit der Taktschaltung des Controllers für FlexRIO kann der Benutzer mehrere Geräte mit einer Genauigkeit im Bereich der Unterabtastung synchronisieren.

Bei verteilten Systemen und Zeitstempeln lässt sich ein GPS-Empfänger anschließen, der einen 10-MHz-Takt an den Referenztakteingang und einen 1-Puls-pro-Sekunde-Eingang an den Trigger-SMA liefert. Bei weniger strengen Synchronisationsanforderungen unterstützt der NI Linux Real-Time Host auch das softwarebasierte IEEE 1588. Bei Systemen, bei denen eine elektrische Synchronisierung möglich ist, kann eine 10-MHz-Quelle wie die Ettus Octoclock als gemeinsamer Referenztakt verwendet werden. Wenn mehrere Geräte nebeneinander aufgestellt werden, empfiehlt es sich, die erweiterten Takt- und Synchronisierungsfunktionen der PXI-Plattform zu nutzen.

Prozessor

Der Dual-Core ARM Cortex-A9-Prozessor bietet die Flexibilität und Konnektivität, die für den Einsatz des Controllers für FlexRIO im praktischen Einsatz erforderlich sind. Er kann dazu genutzt werden, um Daten an ein Netzwerk zu übermitteln, Konfigurationsparameter anzupassen, Daten und Meldungen zu protokollieren oder sogar die Software und FPGA-Firmware auf dem Gerät zu aktualisieren. Der Prozessor führt das NI Linux Real-Time OS aus, das neben den üblichen Vorteilen des Linux-Kernels einen höheren Determinismus und eine höhere Zuverlässigkeit bietet. Das Echtzeitbetriebssystem (RTOS) kann mit dem LabVIEW Real-Time Module über LabVIEW programmiert werden und unterstützt auch die C/C++-Entwicklung mit Ihrer bevorzugten integrierten Entwicklungsumgebung (IDE). Bei der Programmierung und Erstellung von Anwendungen mit LabVIEW haben Entwickler Zugriff auf vorgefertigte Bibliotheken für Netzwerkkommunikation und File I/O, was die Entwicklung erheblich vereinfacht.

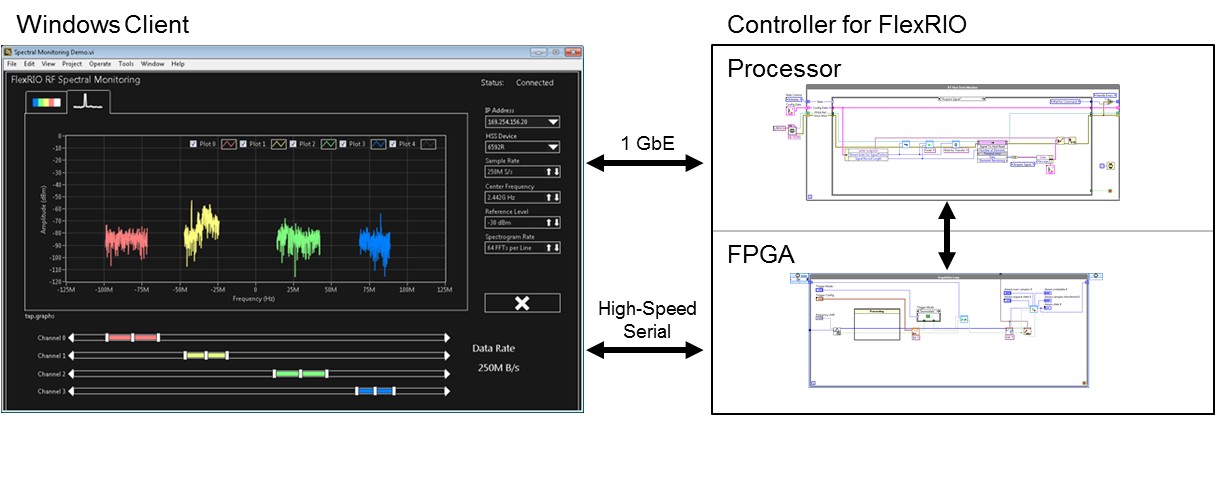

Für Benutzer, die mit FlexRIO vertraut sind, besteht der Hauptunterschied beim Wechsel von FlexRIO auf PXI zum Controller für FlexRIO darin, dass zwischen dem FPGA und einem herkömmlichen Windows-Client eine Anwendungsschicht für die Netzwerkkommunikation hinzugefügt wird. Anstatt den FPGA direkt von Windows aus anzusteuern, wird der Programmcode, der für NI Linux Real-Time entwickelt wurde, auf den FPGA ausgerichtet, und der Benutzer ist für die Programmierung jeglicher Netzwerkkommunikation zur Überwachung oder Konfiguration des Systems verantwortlich. Bei NI 7932R und NI 7935R können Benutzer die zwei seriellen Ports mit hohen Geschwindigkeiten für das Streamen von Daten direkt vom FPGA über 10-Gigabit-Ethernet-UDP oder Xilinx Aurora nutzen.

Abbildung 8: Ein implementiertes System verfügt häufig über drei Anwendungsschichten: die auf dem FPGA ausgeführte Firmware, den auf dem Linux-Real-Time-Host ausgeführten LabVIEW- oder C/C++-Programmcode und eine Client-Anwendung zur Fernkonfiguration, Überwachung oder Datenaufzeichung.

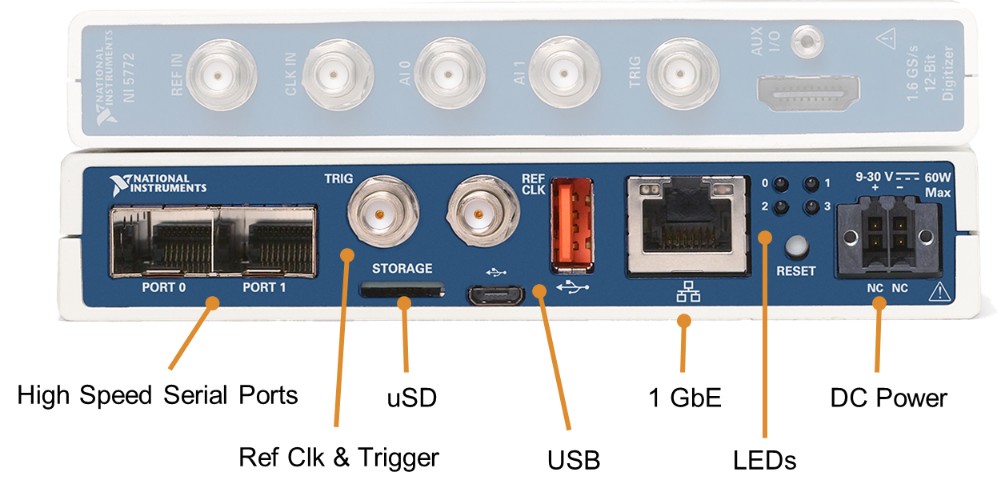

Der Prozessor hat darüber hinaus Zugriff auf einen eigenen Flashspeicher mit 512 MB und einen Arbeitsspeicher mit 512 MB sowie auf eine 1-Gigabit-Ethernet-Schnittstelle, USB-2.0-Geräte- und Host-Schnittstellen und einen µSD-Kartensteckplatz. Die primäre Schnittstelle für Anwendungen in der Praxis sollte das 1-Gigabit-Ethernet sein, da es wesentlich höhere Bandbreiten unterstützt. Der USB-Port kann jedoch für die Einrichtung, Konfiguration und Diagnose verwendet werden.

Konnektivität

Alle Anschlüsse befinden sich auf einer einzigen Hardware-Oberfläche, so dass das Gerät leichter in größere Systeme integriert werden kann. Obwohl die I/O modular aufgebaut ist, liefern analoge Adaptermodule dem FPGA auch digitale I/O über einen zusätzlichen I/O-Anschluss. Der Controller kann mit einer Gleichspannung zwischen 9 und 30 Volt betrieben werden, was bedeutet, dass er in tragbaren Systemen auch batteriebetrieben sein kann.

Abbildung 9: Abgesehen von den Anschlussmöglichkeiten, welche die FlexRIO-Adaptermodule bieten, verfügt der Controller für FlexRIO über Branchenstandard-Schnittstellen für das Streamen von Daten, SMA-Anschlüsse für die Taktung und Synchronisierung, USB-Ports für die Kommunikation mit Peripheriegeräten und LEDs für die visuelle Statusanzeige.

Mit Ausnahme der beiden USB Ports verfügen alle Anschlüsse über Maßnahmen zur Kabelbefestigung. Der USB-Host Port (in der Farbe Orange) ist speziell für eine hohe Speicherkapazität ausgelegt, während der USB-Device-Port in erster Linie für Diagnosezwecke vorgesehen ist.

Physikalische Verpackung

Das Aluminiumgehäuse des Geräts macht die Entwicklung benutzerdefinierter mechanischer Komponenten überflüssig und sorgt für eine einfache Integration, indem es eine konsistente analoge und thermische Leistung in einer Vielzahl von Anwendungsfällen bietet. Mit dem Montagesatz kann das Gerät auch sicher auf der Montageplatte befestigt werden.

Abbildung 10: Der Controller für FlexRIO ist für Embedded-Anwendungen konzipiert, in denen Größe, Gewicht und Leistung begrenzt sind.

Außerdem bietet das Gesamtpaket mehrere Merkmale, die eine langfristige Zuverlässigkeit und Wartungsfreundlichkeit gewährleisten. Zum einen haben die Entwickler Zugang zu Software-Hooks zur Überwachung der FPGA- und Prozessortemperaturen. Sollte die Temperatur des FPGA oder des Prozessors die Sicherheitsgrenzen überschreiten, schaltet sich das Gerät automatisch ab, um Schäden an den internen Komponenten zu vermeiden. Die aktive Kühlung erfolgt durch einen Lüfter, der vom Benutzer gewartet werden kann. Dieser kann in der Software überwacht und automatisch an die Gerätetemperatur angepasst werden. Bei 40 °C liegt die mittlere Betriebsdauer zwischen Ausfällen des Lüfters bei über sieben Jahren.

In Umgebungen, in denen Erschütterungen, Vibrationen, Temperatur oder Luftfeuchtigkeit eine Rolle spielen, ist der Controller für FlexRIO analog zu PXI ausgelegt. Er hält Stößen von 30 g in der Spitze bei halber Sinusfrequenz, Schwingungen von 0,3 geff zwischen 5 Hz und 500 Hz, Umgebungstemperaturen von 0 °C bis 55 °C und einer Luftfeuchtigkeit von 5 % bis 95 % (ohne Kondensation) stand.

Zusammenfassung

Die Möglichkeit der schnellen Prototypenerstellung von Algorithmen, die in Echtzeit ausgeführt werden, stellt einen Vorteil dar, den NI seit über einem Jahrzehnt mit der LabVIEW rekonfigurierbaren I/O-(RIO)-Architektur und LabVIEW FPGA zur Verfügung stellt. Ingenieuren und Wissenschaftlern, die an der Prototypenerstellung neuer Technologien in Bereichen wie Radar, Spektrumüberwachung, Kommunikation, Industriemaschinen, Ultraschall und medizinische Bildgebung arbeiten, bietet diese Plattform die Möglichkeit einer schnelleren Prototypenerstellung bei maximaler Wiederverwendung des Programmcodes während der Produktentwicklung oder der Bereitstellung.

Nächste Schritte

- Weitere Informationen zu FlexRIO

- NI-FlexRIO-Adaptermodule kaufen

- Controller für FlexRIO-Varianten anschauen

Die eingetragene Handelsmarke Linux® wird gemäß einer Unterlizenz von LMI verwendet. LMI ist der exklusive Lizenznehmer von Linus Torvalds, dem weltweiten Eigentümer der Marke.