Einführung in PXI-Module für High-Speed Serial

Überblick

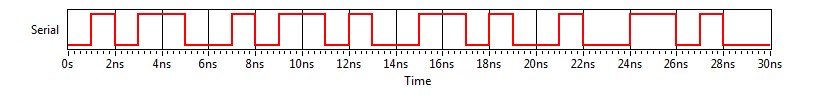

PXI-Module für High-Speed Serial unterstützen Ingenieure bei der Validierung, Anbindung und beim Testen serieller Hochgeschwindigkeitsprotokolle. Ausgewählte Hochgeschwindigkeitsmessgeräte für serielle Protokolle, wie beispielsweise das PXIe-7903 und PXIe-7902, wurden für Ingenieure entwickelt, die leistungsstarke FPGA-Coprocessing-Funktionen benötigen, um großvolumige Datenbewegungen und eine Inline-Echtzeit-Signalverarbeitung zu erzielen. Diese Hardware ist mit einem Xilinx Kintex™ UltraScale+™-FPGA oder einem FPGA der Serie 7 ausgestattet, die Sie mit dem LabVIEW FPGA Module programmieren können, um eine maximale anwendungsspezifische Anpassung und Wiederverwendung zu ermöglichen. Diese Geräte nutzen FPGA-Multi-Gigabit-Transceiver (MGTs) zur Unterstützung von Leitungsraten von bis zu 28,2 Gbit/s und bis zu 48 TX- und RX-Lanes. Als Teil der PXI-Plattform profitieren die Module von PXI-Takt- und Triggerfunktionen sowie von Funktionen zur Hochgeschwindigkeitsdatenübertragung, darunter Streaming zum und vom Datenträger sowie Peer-to-Peer-Streaming (P2P) mit Raten von bis zu 7 GB/s.

Inhalt

- Entwicklung serieller Hochgeschwindigkeitsschnittstellen

- Serielle Module mit hoher Geschwindigkeit

- Beispielanwendungen

- Erforderliche Fähigkeiten

- Nächste Schritte

Entwicklung serieller Hochgeschwindigkeitsschnittstellen

Mit der ständig steigenden Nachfrage nach höheren Datenbandbreiten müssen kabelgebundene Schnittstellen ihre Taktraten und ihre Parallelität erhöhen, um mit der Entwicklung Schritt halten zu können. Bei herkömmlichen parallelen Datenbussen können jedoch bereits geringste Laufzeitunterschiede zwischen den Takt- und Datenleitungen die Bitfehlerrate der Schnittstelle gefährden. Serielle Datenverbindungen bieten eine Lösung für dieses Problem, indem sie den Takt in den Datenstrom eines gegebenen Paars differentieller Leiterbahnen einbetten, wodurch die Möglichkeit von Laufzeitunterschieden zwischen Takt und Daten ausgeschlossen wird. Diese Funktion erfordert zusätzliche Elektronik am Empfangsende der Schnittstelle sowie eine zusätzliche Kodierung für die Taktwiederherstellung. Doch es sind erheblich höhere Datenraten möglich, was dem Bandbreitenbedarf entspricht.

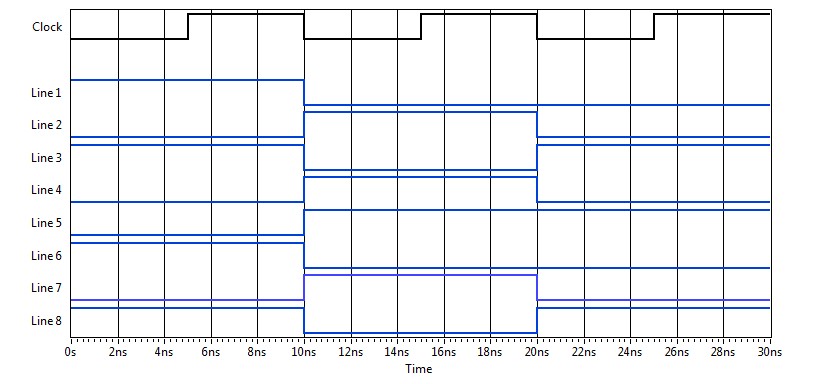

Abbildung 1. Paralleler Takt (schwarz) und Daten (blau) im Vergleich zu eingebettetem Takt in Daten (rot) bei äquivalenter Datenbandbreite.

Moderne Datenaustauschprotokolle sind von diesen parallelen Schnittstellen zu seriellen Hochgeschwindigkeitsschnittstellen übergegangen, wie z. B. PCI Express, HDMI- und DisplayPort-Videostandards, IEEE 1394b, USB 3.0 usw. Für Entwurfs- und Testingenieure stellt die Validierung dieser Schnittstellen neue Herausforderungen dar, die neue Testhardware erfordern. In der Vergangenheit verwendeten Ingenieure teure Oszilloskope oder Bitfehlerratentester (Bit Error Rate Testers, BERTs) zur Charakterisierung der physischen Schnittstellen sowie protokollspezifische Analyseprogramme und Generatoren, um zu überprüfen, ob der Protokollstack korrekt implementiert ist und Datenübertragung und -empfang effizient ablaufen. Für automatisierte V&V- und Fertigungstests gibt es jedoch keine optimierte Hardware, um diese seriellen Schnittstellen zu testen. Oszilloskope und Bitfehlerratentester sind oft zu teuer und zu langsam, um die von ihnen angebotene Abdeckung zu rechtfertigen, während protokollspezifische Hardware meist nicht flexibel genug ist, um sie in automatisierte Testsysteme zu integrieren. Protokollspezifische Hardware kann dagegen nicht für andere Tests wiederverwendet oder für andere Prüflinge (DUTs) umfunktioniert werden.

FPGAs bieten eine Lösung für diese Herausforderungen. Moderne Hochleistungs-FPGAs enthalten in der Regel mehrere MGTs, die mit einer Vielzahl serieller Hochgeschwindigkeitsschnittstellen arbeiten. In Kombination mit dem entsprechenden protokollspezifischen IP, der grafischen Programmierung durch das LabVIEW FPGA Module und den Vorteilen des PXI-Ökosystems entsteht ein neues Hochgeschwindigkeitssoftwaremessgerät für serielle Protokolle.

Serielle Module mit hoher Geschwindigkeit

Tabelle 1. PXI-Module für High-Speed Serial.

¹Lücke bei den erreichbaren Leitungsraten zwischen 8 Gbit/s und 9,8 Gbit/s.

²Das PXIe-7903 ist ein Modul mit zwei Slots.

Konnektivität und Verkabelung sind bei Anwendungen mit hohen Datenraten und analogen Bandbreiten von über 20 GHz von entscheidender Bedeutung. Die Module PXIe-7903, PXIe-7902, PXIe-6594, PXIe-6593, PXIe-6592 und PXIe-6591 bieten jeweils unterschiedliche Optionen, um die Konnektivität für bestimmte Anwendungsfälle zu vereinfachen. Alle drei Module umfassen einen benutzerprogrammierbaren Xilinx-FPGA.

Die Xilinx-Transceiver der Serie 7 (GTX) stellen die Schlüsseltechnologie hinter diesen Messgeräten dar. Sie verwenden „Current Mode Logic“ (CML), eine differentielle Schnittstelle mit einem kleinen Signalhub von 800 mVpp (nominal 1.000 mVpp Maximum) für reduzierten Stromverbrauch und abgestrahlte Emissionen, sowie eine differentielle Impedanz von 100 Ohm (50 Ohm pro Signalzweig), um Reflexionen und die daraus resultierenden Signalfehler bei hohen Datenraten zu minimieren. Für eine optimale Signaltreue verfügen diese Transceiver darüber hinaus über eine programmierbare Sendeamplitude zur Kompensierung langer Kabel sowie über eine Sende-Pre- und -Postemphasis und eine autoadaptive Empfängerentzerrung, um begrenzte Analogkanal-/Kabelbandbreite zu überwinden.

Alle seriellen Hochgeschwindigkeitsschnittstellen erfordern einen Bezugstakt, der mit einem ganzzahligen Teiler der Leitungsrate arbeitet. Für maximale Flexibilität enthalten die GTX-Transceiver eine Phasenregelschleife (Phase-Locked Loop, PLL), die den Bezugstakt bis zu 100-fach multiplizieren kann, um die serielle Datenrate zu erzeugen. Sie umfassen außerdem Seriell-Parallel- und Parallel-Seriell-Wandler mit bis zu 80-fachen Wandlerverhältnissen, die die FPGA-Taktfrequenzen begrenzen, aber gleichzeitig hohe serielle Datenraten ermöglichen. Darüber hinaus verfügen die Transceiver über integrierte 8b/10b-, 64b/66b- und 64b/67b-Kodier- und Dekodierstrukturen, um eine ausreichende Anzahl von Signalübergängen für die Taktwiederherstellung zu gewährleisten und den Verbrauch allgemeiner FPGA-Ressourcen zu vermeiden. Im Benutzerhandbuch zu Xilinx-GTX/GTH-Transceivern für FPGAs der Serie 7 finden Sie weitere Informationen zu Xilinx-GTX-Transceivern.

Neben der Bereitstellung serieller Hochgeschwindigkeits-Transceiver übernehmen die FPGAs von Xilinx auf den Geräten noch eine Reihe weiterer wichtiger Funktionen. Sie implementieren die Logik für das verwendete Protokoll sowie anwendungsspezifische Benutzerlogik für die Hardwarekonfiguration und Datenerzeugung, -empfang und -bewegung im gesamten System.

Abbildung 2: PXIe-7903-Hardwarearchitektur mit wichtigen Schnittstellen und Datenraten.

Tabelle 2. PXI-Module für High-Speed Serial und ihre jeweiligen FPGA-Spezifikationen.

Direkt mit den FPGAs verbunden ist ein bis zu 20 GB großer DDR3-DRAM-Speicher, der mit Raten von bis zu 25 GB/s (theoretisches Maximum) in benutzerdefinierten Zugriffsmustern gelesen oder geschrieben werden kann. Der FPGA verfügt außerdem über eine PCI-Express-x8-Schnittstelle der dritten Generation zur PXI-Express-Backplane für das Streaming von Daten zum und vom Host bzw. Datenträger oder für P2P zu anderen FPGA-fähigen Geräten im System mit unidirektionalen Raten von bis zu 7 GB/s und bidirektionalen Raten von bis zu 2,4 GB/s in jede Richtung (insgesamt 4,8 GB/s).

Ein Bezugstakt mit geringem Jitter und hoher Genauigkeit ist eine wichtige Komponente jedes seriellen Hochgeschwindigkeitsübertragungssystems. Alle Module verfügen über einen geräteeigenen Synthesizer mit beliebiger Rate für den MGT-Betrieb über den gesamten Bereich der Xilinx-GTX-Transceiver, wobei die Module PXIe-6591, PXIe-6592 und PXIe-7902 mit Geschwindigkeiten von 500 Mbit/s bis 8 Gbit/s und von 9,8 Gbit/s bis zu den jeweils maximalen Geräteraten arbeiten, während PXIe-6593, PXIe-6594 und PXIe-7903 keine solche Lücke zwischen ihren minimalen und maximalen Leitungsraten aufweisen. Die Module PXIe-6591, PXIe-6592, PXIe-6593 und PXIe-6594 verfügen am Frontpanel über Koaxialanschlüsse für den Export des integrierten Bezugstakts. Alle vier Module bieten Konnektivität für den Import eines externen Bezugstakts. Außerdem können die Geräte den PXI-Express-Takt von 100 MHz oder die DStarA-Backplane-Takte als Referenz für die MGTs weiterleiten.

Software

Ein Softwaremessgerät bietet den gleichen Funktionsumfang wie ein Messgerät mit fester Funktion, aber der Benutzer kann die Messgerätehardware über einen offenen, benutzerprogrammierbaren FPGA anpassen. Ein solches Maß an Anpassung ist bei einem PXI-Hochgeschwindigkeitsmessgerät für serielle Protokolle erforderlich, um eine Vielzahl von Protokollen und Anwendungen zu unterstützen. Daher gibt es keine einheitliche High-Level-API für die Programmierung dieser Geräte. Stattdessen werden sie direkt in der LabVIEW-Software für den Host- (CPU) und den FPGA-Code programmiert und bilden eine Schnittstelle zwischen beiden mit der untergeordneten NI-RIO-API. Um Benutzern den Einstieg zu erleichtern, veranschaulichen zahlreiche Beispiele die Verwendung verschiedener Protokolle sowie verschiedene Nutzungsmodelle für diese Geräte.

Der offene FPGA bietet ein hohes Maß an Anpassungsfähigkeit, das bei anderen Geräten nicht zu finden ist. In erster Linie wird damit das serielle Protokoll implementiert, für das das Messgerät konfiguriert ist. Allein dadurch können die Modelle PXIe-7903, PXIe-7902, PXIe-6594, PXIe-6593, PXIe-6592 und PXIe-6591 eine Vielzahl von Standard- und sogar benutzerdefinierten seriellen Protokollen unterstützen. Über das Protokoll hinaus ermöglichen benutzerdefinierte Hardwarefunktionen Testverfahren, die bisher nicht möglich waren. So werden beispielsweise durch die algorithmische Datenerzeugung im FPGA der erforderliche Signalverlaufsspeicher und die Systembandbreite für das Herunterladen dieser Signalverläufe reduziert, wodurch sich der Testdurchsatz beschleunigt. Algorithmische Datenanalysen wie Antwortvergleich, intelligente Triggerung und Datenreduktion und -komprimierung verringern die Datenmenge, die von der Host-CPU verarbeitet werden muss, erheblich, wodurch sich auch die Testzeit verkürzt.

Der benutzerdefinierte DRAM-Zugriff ermöglicht Flexibilität bei der Partitionierung des DRAMs in Stimulus- und Antwortbereiche. Darüber hinaus ermöglicht die Plattform benutzerdefinierte Komprimierungs- und Dekomprimierungsalgorithmen, wodurch die DRAM-Größe und -Bandbreite optimal genutzt werden kann. Die Erfassung und Wiedergabe von Standardsignalverläufen ist sicherlich möglich, aber je nach Protokoll, Leitungsrate und Anzahl der Lanes kann die I/O-Bandbreite die DRAM-Bandbreite überschreiten. Schließlich bietet die benutzerdefinierte Datenbewegung zu und von einem Hochgeschwindigkeitsmessgerät für serielle Protokolle und dem Host oder anderen Geräten eine erhebliche Flexibilität bei der Integration auf Systemebene. Beispielsweise ist es möglich, analoge Daten mit einem Hochgeschwindigkeitsdigitalisierer in digitale Samples umzuwandeln, diese Daten dann mithilfe von NI-P2P-Streaming mit bis zu 7 GB/s an ein Hochgeschwindigkeitsmessgerät für serielle Protokolle zu übertragen und diese digitalen Samples anschließend über ein serielles Protokoll an ein externes Gerät zu senden. Alternativ kann ein Hochgeschwindigkeitsmessgerät für serielle Protokolle einen seriellen Datenstrom erfassen und an die Host-CPU und schließlich ein RAID-Array mit hoher Bandbreite für die stunden- oder sogar tagelange kontinuierliche Speicherung übertragen, wiederum mit Raten von bis zu 7 GB/s.

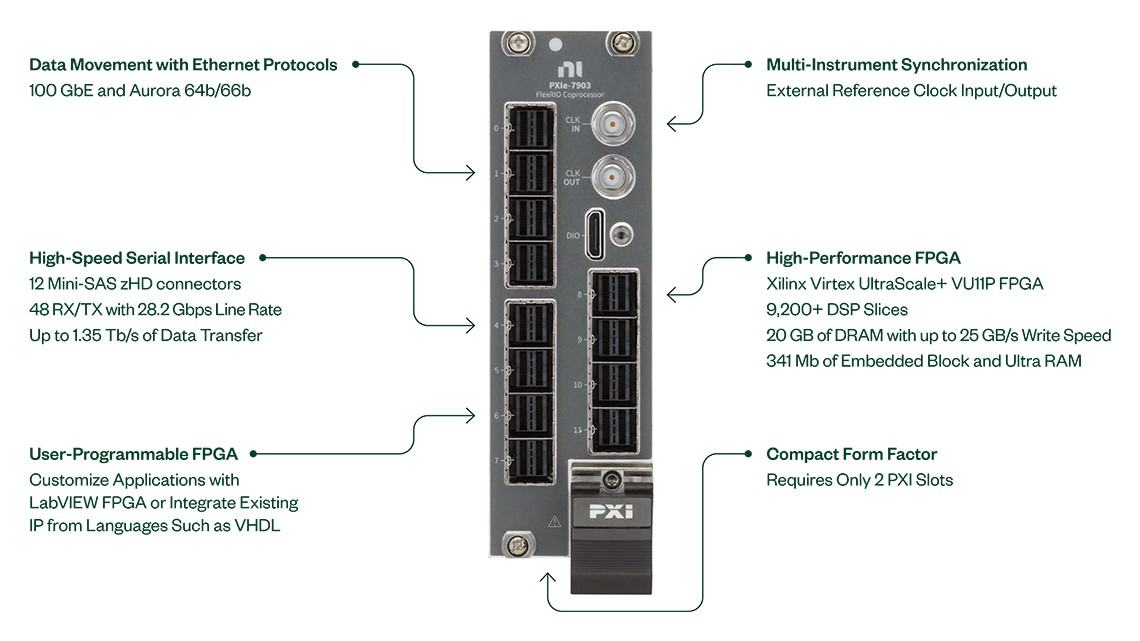

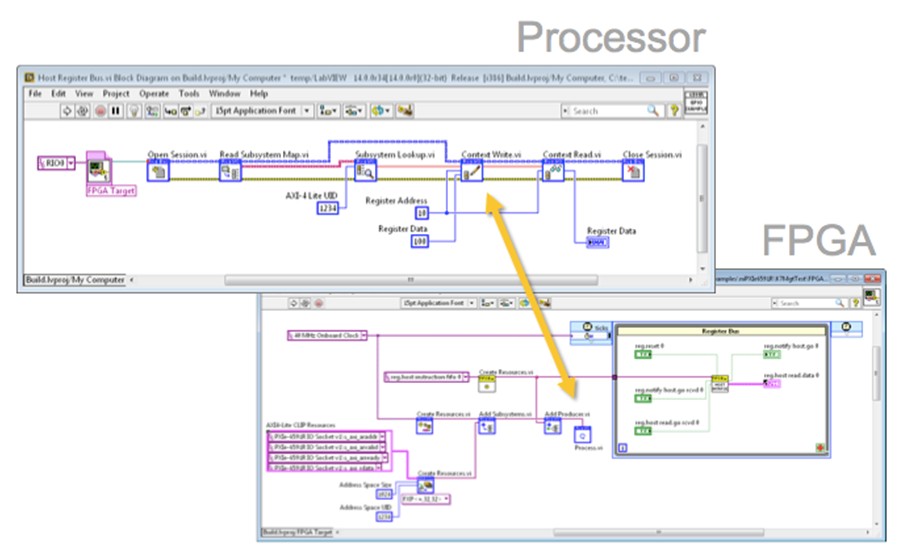

LabVIEW FPGA macht es einfach, diese Hochgeschwindigkeitsmessgeräte für serielle Protokolle zu konfigurieren und zu programmieren. In Abbildung 3 sind neben typischem Programmcode die wichtigsten Schnittstellen dargestellt, auf die über LabVIEW zugegriffen werden kann. LabVIEW FPGA und die NI-RIO-API bieten effiziente Mechanismen für den PCI-Express-basierten Datenaustausch zwischen der Host-CPU und dem FPGA, darunter Register-Lese- und -Schreibvorgänge sowie bidirektionale DMA-Übertragungen. Der DRAM-Zugriff – normalerweise eine schwierig zu verwaltende Schnittstelle in untergeordneten Hardwarebeschreibungssprachen (HDLs) – wird durch abstrahierte Anforderungs-, Lese- und Schreibschnittstellen vereinfacht, während gleichzeitig ein hoher Durchsatz aufrechterhalten und eine grundlegende Lese-/Schreib-Arbitrierung bereitgestellt wird. Die Konfiguration von GTX-Transceivern ist in der Regel protokollspezifisch, und für viele serielle Hochgeschwindigkeitsschnittstellen (HDL oder Netzliste) mit integrierter Transceiver-Konfiguration ist bereits IP vorhanden. Diese serielle Protokollschnittstelle wird in LabVIEW FPGA über eine Socketed Component-Level IP-(CLIP-)Schnittstelle bereitgestellt. CLIP-Knoten ermöglichen die asynchrone Ausführung von Programmcode, der nicht in LabVIEW implementiert wurde, verfügen jedoch über eine klar definierte Schnittstelle zum LabVIEW-FPGA-Diagramm. Ein gängiges Szenario verwendet protokollspezifisches IP von Xilinx (einschließlich Transceiver-Konfiguration) aus dem Xilinx-Vivado-IP-Katalog und eine dünne Schicht VHDL, um die Schnittstelle zu LabVIEW FPGA zu definieren. Nachdem das Protokoll implementiert wurde, bietet LabVIEW FPGA eine komplexe Programmiersprache für die Implementierung beliebiger Benutzerlogik wie Entscheidungsfindung, Zustandsautomatenimplementierung, Prüflingssteuerung, Signalverarbeitung und Datenbewegung.

Abbildung 3: LabVIEW FPGA bietet grafischen Zugriff auf Schlüsselaspekte des benutzerprogrammierbaren FPGA von PXI-Modulen für High-Speed Serial.

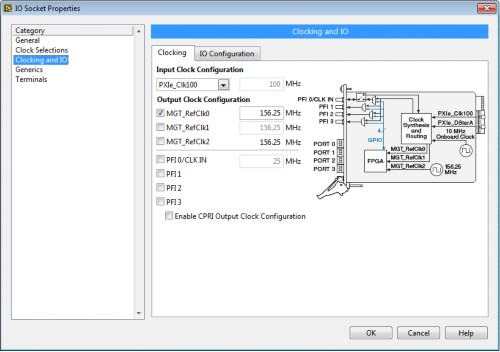

Neben der Definition der Logik, die auf dem benutzerprogrammierbaren FPGA implementiert werden soll, vereinfacht LabVIEW die Hardwarekonfiguration durch seine Projekthierarchie und die zugehörigen Konfigurationsseiten. So erfordert beispielsweise die Konfiguration des Bezugstakts bei diesen Hochgeschwindigkeitsmessgeräten für serielle Protokolle einen komplexen Algorithmus zur Bestimmung hunderter Registereinstellungen, die auf bis zu vier separate integrierte Schaltungen angewendet werden können, zusätzlich zur Logik, die zur Anwendung dieser Register beim Einschalten des FPGA erforderlich ist. LabVIEW FPGA zeigt dies als Dialogfeld mit einer grafischen Darstellung der Optionen sowie Entwurfsregeln und Anleitungen zur Durchsetzung gültiger Konfigurationen an. Dieser Ansatz vereinfacht die Konfiguration des Taktsynthesizers für alle Taktraten und der Routing-Schaltung, sodass für eine Aufgabe, die bisher Stunden oder Tage in Anspruch nahm, nur noch Minuten erforderlich sind.

Abbildung 4. LabVIEW FPGA bietet eine intuitive, grafische Oberfläche für die Taktkonfiguration, die einen komplexen Prozess vereinfacht.

Um die Wiederverwendung von Programmcode zu ermöglichen und allgemeine Aufgaben zu vereinfachen, unterstützen PXI-Module für High-Speed Serial bestimmte Geräteentwurfsbibliotheken. Dabei handelt es sich um Host- und FPGA-Codebibliotheken mit LabVIEW-Schnittstellen, die aufeinander abgestimmt sind und allgemeine Funktionen bieten. Das Anweisungs-Framework ist eine Geräteentwurfsbibliothek für die dynamische Hardwarekonfiguration während der Laufzeit. Obwohl sich die meisten Hardwarefunktionen dieser seriellen Geräte (z. B. die Taktkonfiguration) im LabVIEW-Projekt statisch konfigurieren lassen, können Benutzer das Anweisungs-Framework nutzen, um anwendungsspezifische Firmware-Parameter zu steuern. Beispielsweise vereinfacht das Anweisungs-Framework die Host-Konfiguration von Registereinstellungen, die über AXI-4-Lite--Schnittstellen auf dem FPGA verfügbar gemacht werden, die üblicherweise im IP zu seriellen Protokollen von Xilinx zu finden sind.

Abbildung 5. Prozessor- und FPGA-Code zum Schreiben und Lesen von Registern über eine AXl-4-Lite-Schnittstelle.

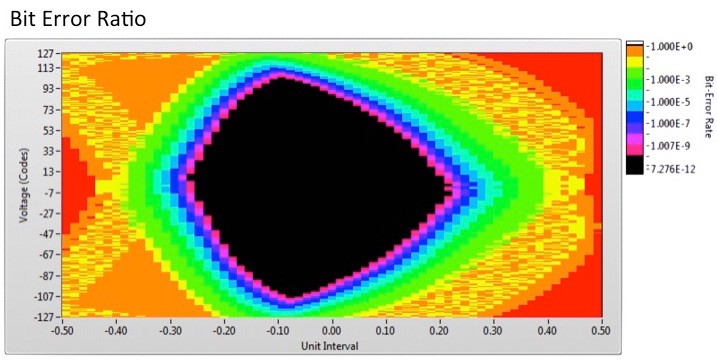

Die Eye-Scan-Geräteentwurfsbibliothek baut auf dem Anweisungs-Framework auf und bietet Debugging-Funktionen für die seriellen Hochgeschwindigkeitsempfangskanäle. Die Xilinx-GTX-Transceiver verfügen über zwei Empfänger-Komparatoren pro Kanal. Während ein Komparator auf der Grundlage der wiederhergestellten Taktfrequenz und -phase automatisch die Mitte des seriellen Auges verfolgt, können Amplitude und Phase des anderen Komparators unabhängig voneinander verschoben werden. Durch Variieren der Parameter des letztgenannten Komparators und Vergleichen der Ergebnisse mit denen des ersteren kann die Eye-Scan-Geräteentwurfsbibliothek ein statistisches Augendiagramm erstellen, das zur Bestimmung des Verbindungsspielraums der Schnittstelle nützlich ist, und zwar mit der Genauigkeit der Bitfehlerratenuntergrenze der GTX-Transceiver von Xilinx. Da die Eye-Scan-Geräteentwurfsbibliothek einen unabhängigen Satz von Hardwareressourcen verwendet, kann sie mit anderem Protokoll-IP koexistieren und gleichzeitig mit anderen anwendungsspezifischen Funktionen ausgeführt werden.

Abbildung 6. Die LabVIEW Instrument Design Libraries for PXI High-Speed Serial Instruments enthalten einen Referenzentwurf für die Durchführung eines statistischen Augenscans mithilfe einer Loopback-Konfiguration.

Abgesehen von diesen Geräteentwurfsbibliotheken bieten andere Softwaremessgeräte von National Instruments Bibliotheken für eine Vielzahl nützlicher Funktionen wie Multi-Recording oder DRAM-basierte Erfassung und Erzeugung. Obwohl sie auf den Modulen PXIe-7903, PXIe-7902, PXIe-6594, PXIe-6593, PXIe-6592 und PXIe-6591 nicht offiziell unterstützt oder getestet werden, können sie je nach Hardware-Agnostik der Geräteentwurfsbibliothek auch mit PXI-Modulen für High-Speed Serial verwendet werden.

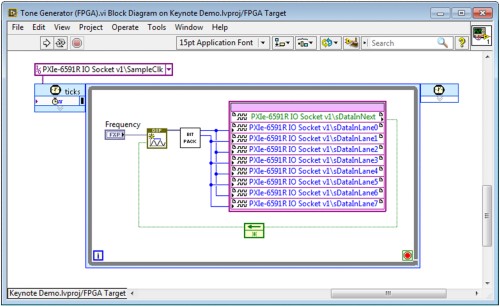

Abbildung 7. Ingenieure können die DSP-Geräteentwurfsbibliothek verwenden, um eine Sinuskurve für die Übertragung an einen D/A-Wandler über das serielle JESD204B-Protokoll zu synthetisieren.

Protokolle

Die Xilinx-GTX-Transceiver der PXI-Module für High-Speed Serial unterstützen eine Vielzahl von Protokollen. NI stellt neben einer Reihe von Softwarebeispielen zur Veranschaulichung der Integration gängiger Protokolle auch LabVIEW-Architekturen für verschiedene Anwendungsmuster bereit. Jedes Beispiel enthält eine vorkompilierte FPGA-Bitdatei für das unterstützte Gerät sowie den zugehörigen Quellcode und das entsprechende Protokoll-IP. Falls dieser Programmcode für die Endanwendung modifiziert werden muss, erfordern bestimmte Protokolle eine IP-Lizenz von Xilinx, um den FPGA neu zu kompilieren. Dieses Protokoll-IP ist entweder über Xilinx oder über Händler wie Avnet oder DigiKey erhältlich.

Xilinx Aurora

Das Aurora-Protokoll von Xilinx bietet ein einfaches Protokoll mit kurzer Wartezeit und kleinem Footprint, das für serielle Punkt-zu-Punkt-Schnittstellen entwickelt wurde. Es unterstützt die volle Rate der seriellen Xilinx-GTX-Transceiver sowie Lane-Bonding für eine noch größere Bandbreite. Aurora wurde in erster Linie für Datenbewegungen mit hoher Bandbreite entwickelt und bietet Ablaufsteuerung, flexible Gestaltung und Optionen für Simplex- oder Vollduplex-Kanäle. Weitere Informationen zu Xilinx Aurora finden Sie unter den folgenden Links:

http://www.xilinx.com/products/design_resources/conn_central/grouping/aurora.htm

Der Treiber „Instrument Design Libraries for High Speed Serial Instruments“ installiert einen Beispielprojekt-Referenzentwurf für Aurora 64b66b, und NI bietet ein Webbeispiel für Aurora 8b10b.

JESD204B und JESD204C

Da die Abtastraten und Auflösungen von Analog-Digital-Wandlern und Digital-Analog-Wandlern steigen, um den Anforderungen von drahtlosen breitbandmodulierten Digitalübertragungen gerecht zu werden, haben sich die Datenraten zu und von diesen Wandlern erhöht. Bei herkömmlichen parallelen Takt- und Datenschnittstellen erfordert dies eine größere Anzahl integrierter Schaltungspins mit engeren Toleranzen. Die Protokolle JESD204B und JESD204C begegnen dieser Herausforderung, indem sie diese Schnittstellen auf serielle Hochgeschwindigkeitsübertragung umstellen, was für eine hohe Datenbandbreite mit kurzer Wartezeit sorgt und die Synchronisierung mehrerer Wandler vereinfacht. Das Protokoll JESD204B unterstützt bis zu 12,5 Gbit/s und 32 Lanes für die neuesten A/D- und D/A-Wandler mit hoher Bandbreite, hohen Geschwindigkeiten und hoher Kanalanzahl. JESD204C dagegen unterstützt Raten von bis zu 32 Gbit/s. Das Protokoll JESD204B verwendet 8B/10B-Kodierung, während JESD204C 8B/10B, 64B/66B und 64B/80B unterstützt.

10-Gigabit-Ethernet

Mit einer Leitungsrate von 10,3125 Gbit/s bietet 10-Gigabit-Ethernet (10 GbE) eine praktische Bandbreite von ca. 1 GB/s. Die meisten 10-Gigabit-Ethernet-Schnittstellen sind entweder optische oder SFP+-Direktanschlüsse (Kupfer) mit 8P8C/RJ45-basierten Schnittstellen. Das 10-Gigabit-Ethernet-Beispiel für das PXIe-6592 unterstützt optische 10GBASE-SR-, -LR- und -ER-Schnittstellen sowie SFP+-Direktanschlüsse unter Verwendung des 10-Gigabit-Ethernet-PCS/PMA-IP-Cores von Xilinx und des 10-Gigabit-Ethernet-Datenträgerzugriffs-Controllers von OpenCores.org. Ein leichter UDP-Stack, der in LabVIEW FPGA implementiert ist, setzt auf dieser MAC/PHY-Lösung auf. Weitere Informationen zu 10-Gigabit-Ethernet-IP-Cores finden Sie unter den folgenden Links:

https://www.xilinx.com/products/intellectual-property/10gbase-r.html

Der Treiber „Instrument Design Libraries for PXI High-Speed Serial Instruments“ installiert ein Beispielprojekt-Referenzdesign für 1 GbE und 10 GbE.

100-Gigabit-Ethernet

100-Gigabit-Ethernet (100GbE) kann Ethernet-Frames mit einer Rate von 100 Gigabit pro Sekunde (Gbit/s) übertragen – einer deutlich höheren Geschwindigkeit als 10-Gigabit-Ethernet. 100 GbE bietet verschiedene optische und elektrische Schnittstellen sowie unterschiedliche Anzahlen von Glasfasersträngen. Zu den wichtigsten Schnittstellen gehören 100GBASE-KR2, 100GBASE-CR2 und QSFP28.

Im Lieferumfang von LabVIEW FPGA ist ein Beispiel für 100 GbE enthalten.

CPRI

CPRI definiert die optische Schnittstelle zwischen der Funkanlagensteuerung und den Funkanlagen, allgemein bekannt als Remote Radio Heads (RRHs). Der Standard erleichtert die Konfiguration und Synchronisierung von Funkköpfen und ermöglicht das Streaming von digitalen I/Q-Daten (Basisband). Weitere Informationen zum CPRI-IP-Core von Xilinx finden Sie unter folgendem Link:

https://www.xilinx.com/products/intellectual-property/do-di-cpri.html

Serielle RapidIO

Serial RapidIO ist ein leistungsstarkes serielles Verbindungsprotokoll, das für energieeffiziente Embedded-Systeme optimiert ist, darunter Telekommunikationsinfrastruktur, Embedded Computing in Luft- und Raumfahrt, Life-Sciences-Geräte mit hoher Bandbreite und industrielle Steuer- und Regelanwendungen. Es bietet Raten von bis zu 6,25 Gbit/s, Four-Lane-Bonding, kurze Wartezeit, Ablaufsteuerung, Paketlieferung in der richtigen Reihenfolge und einen relativ kleinen Footprint. Weitere Informationen zum Serial-RapidIO-IP-Core von Xilinx finden Sie unter folgendem Link:

http://www.xilinx.com/products/intellectual-property/ef-di-srio.html

Ein Referenzdesign für Serial RapidIO für das PXIe-6592 ist in der NI Community verfügbar. Für SRIO-Schnittstellen größer als x2 empfiehlt NI das PXIe-6591.

Zusätzliche Protokolle

Die vorhergehenden Beispiele stellen keine vollständige Liste aller Protokolle dar, die mit PXI-Modulen für High-Speed Serial kompatibel sind. Fragen zu bestimmten Protokollen, zur Anpassung der Beispiele oder zur Integration benutzerdefinierter oder proprietärer Protokolle können von den NI-Vertriebsingenieuren vor Ort beantwortet werden.

Beispielanwendungen

Durch die flexible Architektur der PXI-Module für High-Speed Serial können eine Vielzahl von Anwendungsfällen mit unterschiedlichen Datenbewegungsmustern, seriellen Protokollen und Softwarefunktionen unterstützt werden.

Funktionstest für Protokolle

Ein häufiger Anwendungsfall für PXI-Module für High-Speed Serial ist die Durchführung protokollspezifischer Funktionstests an einem bestimmten Prüfling. Diese Tests sollen bestätigen, dass der Prüfling über ein serielles Protokoll zuverlässig mit der „Außenwelt“ kommunizieren kann. Solche Tests können Register auf dem Prüfling schreiben und auslesen, Datendurchsatz und Wartezeit-Benchmarks durchführen oder andere protokollspezifische Attribute bzw. integrierte Testmodi ausführen. Sie können auch testen, wie der Prüfling auf Fehlerszenarien wie Antwort-Timeouts, injizierte Fehler oder ignorierte Ablaufsteuerungsbefehle reagiert. Damit verbundene Aufgaben umfassen Messungen der Link-Bitfehlerrate, Belastungstests für die Bitübertragungsschicht, wie etwa maximale und minimale Leitungsraten, Burn-In-Tests und sogar Bus-Snooping, bei denen das Gerät Analysen, benutzerdefinierte Trigger und Datenerfassung auf dem FPGA durchführt.

Steuerung, Stimulus und Antwort des Prüflings

Ein weiterer häufiger Anwendungsfall für PXI-Module für High-Speed Serial ist die Erfassung von Steuerung, Stimulus und Antwort des Prüflings. In diesem Szenario testet das Gerät das serielle Hochgeschwindigkeitsprotokoll nicht unbedingt direkt, sondern sendet oder empfängt Daten vom Prüfling mithilfe eines seriellen Hochgeschwindigkeitsprotokolls, sodass andere Aspekte des Geräts getestet werden können. Darüber hinaus können zusätzliche Digital-I/O-Geräte zur Steuerung des Prüflings über parallele oder serielle Protokolle mit niedriger Geschwindigkeit, wie SPI, verwendet werden.

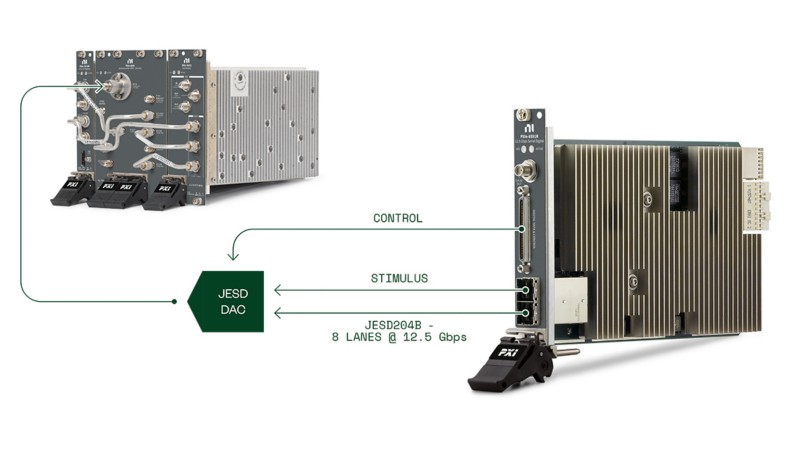

Im folgenden Beispiel stimuliert ein PXIe-6591 einen D/A-Wandler mithilfe des Protokolls JESD204B, um die Analogausgangseigenschaften des D/A-Wandlers zu testen.

Abbildung 8. Viele moderne leistungsstarke D/A-Wandler und A/D-Wandler ermöglichen die Kommunikation über das serielle Hochgeschwindigkeitsprotokoll JESD204B.

Verschieben von Daten mit hoher Bandbreite

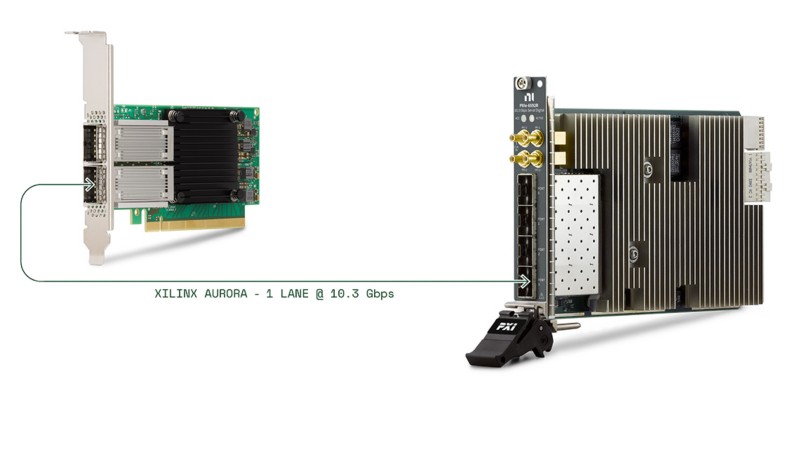

Viele leistungsstarke Embedded-Anwendungen können von der PXI-Plattform profitieren und erfordern eine Datenübertragung mit hoher Bandbreite und kurzer Wartezeit zwischen Hardware von Drittanbietern und NI-PXI-Geräten. Für diese Anwendungen bieten PXI-Module für High-Speed Serial Vorteile wie LabVIEW-FPGA-Hardwareverarbeitung, P2P-Daten-Streaming an PXI-Express-Geräte und Streaming mit hoher Bandbreite zum und vom Datenträger, während Verbindungen mit hoher Bandbreite zu externen Geräten über ein serielles Standardprotokoll mit hohen Geschwindigkeiten bereitgestellt wird.

Im folgenden Beispiel tastet ein Oszilloskop von NI ein analoges Signal ab und sendet die digitalisierten Rohdaten mittels P2P-Daten-Streaming an ein Hochgeschwindigkeitsmessgerät des Typs PXIe-6592 für serielle Protokolle. Das Gerät verarbeitet die Daten dann in Echtzeit mithilfe eines in LabVIEW FPGA implementierten Algorithmus. Abschließend werden die verarbeiteten Daten mithilfe des einfachen Aurora-Protokolls von Xilinx, das für die serielle Kommunikation von FPGA zu FPGA ausgelegt ist, an das Gerät eines Drittanbieters übertragen.

Abbildung 9. PXI-Module für High-Speed Serial sind eine hervorragende Lösung für Datenbewegungen mit hoher Bandbreite und kurzer Wartezeit mit einem Gerät von Drittanbietern.

Fehlersuche und Parametertests für Verbindungen

Da serielle Hochgeschwindigkeitsschnittstellen sehr hochfrequente Signale verwenden, kann eine schlechte Signalintegrität die Kommunikation stören. Wenn solche Probleme auftreten, können Fehlersuchwerkzeuge wertvolle Erkenntnisse über den Zustand der Verbindung liefern. Mit der zuvor beschriebenen Eye-Scan-Geräteentwurfsbibliothek können Entwickler den Verbindungsspielraum der empfangenen Signale bestimmen und feststellen, ob Kommunikationsprobleme auf eine geringe Signalintegrität zurückzuführen sind. Obwohl diese Funktion in erster Linie für die Fehlersuche während der Anwendungsentwicklung konzipiert ist, kann sie auch bei der Gerätevalidierung oder bei Fertigungstests eingesetzt werden, um Einblicke in gerätespezifische Leistungsparameter zu erhalten. Die PXI-Module für High-Speed Serial weisen jedoch Nennwerte für Amplitude und Timing-Genauigkeit auf, für die NI keine Garantie hinsichtlich der Leistung oder Rückverfolgbarkeit dieser Parameter übernimmt. Für bestimmte Anwendungen kann eine Kalibrierung oder Justierung vor Ort eine Option sein.

Andere parametrische Tests umfassen die Bitfehlerrate für eine bekannte pseudozufällige Bitfolge (PRBS) unter Verwendung von Industriestandardmustern (PRBS-7, PRBS-15, PRBS-23 und PRBS-31) anstelle eines spezifischen Protokolls. Die Leitungsraten von Sender und Empfänger können variiert werden, um den Bereich der unterstützten Bitraten für einen bestimmten Prüfling zu bestimmen. Schließlich können Senderamplitude sowie Pre- und Postemphasis variiert werden, um die Empfängerempfindlichkeit zu testen, einschließlich automatischer Verstärkungsregelung und dynamischer Entzerrung.

Zum PXIe-6591 und PXIe-6592 finden Sie in der NI Community unter dem folgenden Link zusätzliche Ressourcen: Artikel zum NI MGT Debug-Tool in der NI Community. Dieser enthält Informationen zu weiteren Tools für die Analyse der Bitübertragungsschicht zur Verwendung mit PXI-Modulen für High-Speed Serial. Informationen zum PXIe-6593 und PXIe-6594 finden Sie im Abschnitt Using Eye Scan with PXIe-6593 and PXIe-6594 High-Speed Serial Devices.

Erforderliche Fähigkeiten

Obwohl LabVIEW und LabVIEW FPGA die Implementierung von Hochgeschwindigkeitstechnologie für serielle Protokolle erheblich vereinfachen, ist doch ein gewisses Fachwissen unerlässlich, um den Erfolg der Programmierung von PXI-Modulen für High-Speed Serial sicherzustellen. Da sie in LabVIEW entworfen werden, ist es wichtig, mit der grafischen Programmierung von LabVIEW vertraut zu sein. Auf der Seite zu den Schulungskursen für die Anwendungsentwicklung mit NI LabVIEW unter ni.com finden Sie entsprechende Hilfe. Darüber hinaus ist für die Anpassung der Nicht-Protokoll-FPGA-Logik in LabVIEW FPGA ein umfassendes Verständnis der Programmierung in LabVIEW FPGA mit hohem Durchsatz erforderlich. Der NI LabVIEW High-Performance FPGA Developer's Guide ist eine gute Ressource für weitere Informationen. Für Protokolle mit vorhandenem IP oder Beispielen sind VHDL-Kenntnisse und -Erfahrung erforderlich, um die Schnittstelle zwischen dem Protokoll-IP und dem LabVIEW-FPGA-Diagramm zu definieren. Abschließend wird für die Implementierung neuer oder benutzerdefinierter Protokolle fortgeschrittenes Know-how im Digitaldesign empfohlen. Bestimmte NI-Partner bieten diese Fähigkeiten für diejenigen an, die unternehmensintern nicht über solche Fähigkeiten verfügen. NI-Vertriebsmitarbeiter vor Ort können bei der Suche nach einem geeigneten Partner behilflich sein.

Tabelle 4. Die Programmierung von Hochgeschwindigkeitsmessgeräten für serielle Protokolle erfordert unterschiedliche Kenntnisse und Tools, je nachdem, wie viele Änderungen an der Schnittstelle vorgenommen werden müssen.

Nächste Schritte

- Erfahren Sie mehr über die Maximierung der Datenbewegung und Signalverarbeitung mit dem PXI-Modul für High-Speed Serial von NI.

- Erfahren Sie mehr zu den grundlegenden Prinzipien serieller Kommunikationsverbindungen mit hohen Geschwindigkeiten.

- Sehen Sie sich ein Beispiel für einen Referenzentwurf für die Implementierung serieller Hochgeschwindigkeitsprotokolle in Funktionstestsystemen für Funk-Transceiver an.

- Zusätzliche Protokollreferenzdesigns, die nicht im Hardwaretreiber enthalten sind, finden Sie in der NI Community unter Examples and IP for Software-Designed Instruments and NI FlexRIO.

- Bestellen Sie PXI-Module für High-Speed Serial.

- Erstellen Sie Ihr PXI-System

|  |  |  |  |  | |

| Spez. | PXIe-6591 | PXIe-6592 | PXIe-6593 | PXIe-6594 | PXIe-7902 | PXIe-79032 |

| Leitungsrate | 500 Mbit/s–12,5 Gbit/s¹ | 500 Mbit/s–10,3125 Gbit/s¹ | 500 Mbit/s–16,3 Gbit/s | 500 Mbit/s–28,2 Gbit/s | 500 Mbit/s–12,5 Gbit/s | 500 Mbit/s–28,2 Gbit/s |

| Kanalanzahl | 8 TX/RX | 4 TX/RX | 8 TX/RX | 8 TX/RX | 24 TX/RX | 48 TX/RX |

| FPGA | Kintex 7 K410T | Kintex 7 K410T | Kintex UltraScale KU040, KU060 | Kintex UltraScale+ KU15P | Virtex™ 7 485T | Virtex UltraScale+ XCVU11P |

| DRAM | 2 GB | 2 GB | 4 GB | 8 GB | 2 GB | 20 GB |

| Host-Streaming-Bandbreite | 3,2 GB/s | 3,2 GB/s | 7 GB/s | 7 GB/s | 3,2 GB/s | 7 GB/s |

| Anschluss | Mini-SAS-Festplatte | SFP+ | QSFP28 | QSFP28 | Mini-SAS-Festplatte | Mini-SAS-Festplatte |

| Verkabelungsoptionen | Kupfer oder optisch | Kupfer oder optisch | Kupfer oder optisch | Kupfer oder optisch | Kupfer oder optisch | Kupfer oder optisch |

| Aux-DIO | 20 SE | 4 SE | 8 GPIO | 8 GPIO | k. A. | 8 GPIO |

| Spez. | FPGA | LUTs | DSP-Sektoren | Eingebetteter Block-RAM |

| PXIe-6591 | Kintex-7 K410T | 254.200 | 1540 | 28 Mb |

| PXIe-6592 | Kintex-7 K410T | 254.200 | 1540 | 28 Mb |

| PXIe-6593 | Kintex UltraScale KU040 | 242.400 | 1.920 | 21,1 Mb |

| Kintex UltraScale KU060 | 331.680 | 2.760 | 38 Mb | |

| PXIe-6594 | Kintex UltraScale+ KU15P | 523.000 | 1.968 | 34,6 Mb |

| PXIe-7902 | Virtex-7 485T | 303.600 | 2.800 | 37 Mb |

| PXIe-7903 | Virtex UltraScale+ XCVU11P | 2.835.000 | 9.216 | 341 Mb |

| Verwendungsmodell | LabVIEW | LabVIEW FPGA mit hohem Durchsatz | VHDL | Umfassende Erfahrung im Digitaldesign |

| Verwendung des vorhandenen Systems | — | — | — | |

| Anpassen des FPGA-Codes, nicht aber des Protokolls | — | — | ||

| Integrieren des vorhandenen Protokolls | — | |||

| Implementieren eines neuen oder benutzerdefinierten Protokolls |