Serielle Highspeed-Kommunikation erklärt

Überblick

Die serielle Highspeed-Kommunikation ist eine immer beliebter werdende Technologie, die den Platzbedarf von Geräten verringert und die Datenkommunikationsraten erhöht. In diesem Whitepaper werden die grundlegenden Prinzipien serieller Highspeed-Kommunikationsverbindungen untersucht.

Inhalt

- Die Notwendigkeit für serielle Highspeed-Kommunikation

- Schichten von seriellen Hochgeschwindigkeitsverbindungen

- Schlussfolgerungen

- Verwandte Inhalte

Die Notwendigkeit für serielle Highspeed-Kommunikation

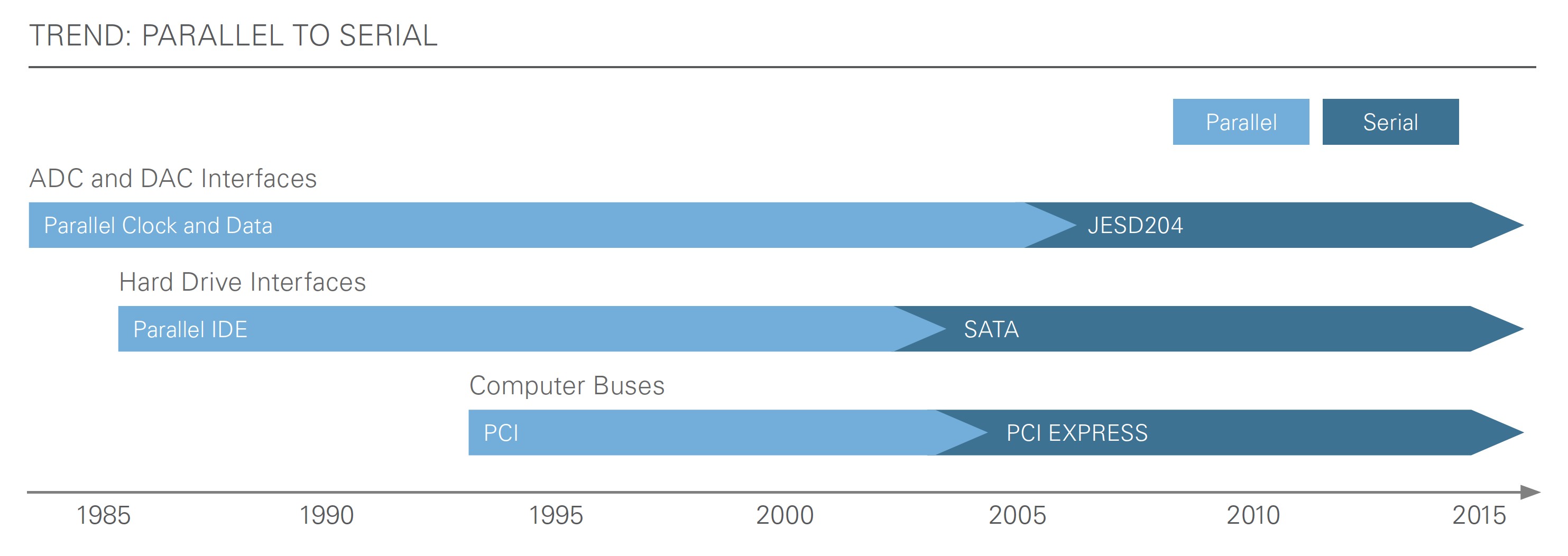

Die Verbraucher verlangen ständig nach besserer Leistung in einem kleineren Formfaktor bei geringerem Strombedarf. Anfang der 2000er-Jahre führten diese Anforderungen in einer Welt von Big Data zu einer drastischen Verschiebung von parallelen zu seriellen Kommunikationsbussen mit hohen Geschwindigkeiten. Dies wiederum hat zu Geräten mit viel geringerem Platzbedarf, einem viel höheren Datendurchsatz und einem geringeren Strombedarf geführt. Diese Funktionen ermöglichen viele der Technologien, die Verbraucher heute nutzen, wie SATA, USB und PCI Express.

Abbildung 1: Anfang der 2000er-Jahre begann der Markt mit der Umstellung von gängigen parallelen Kommunikationsstandards auf serielle Standards.

Vorteile

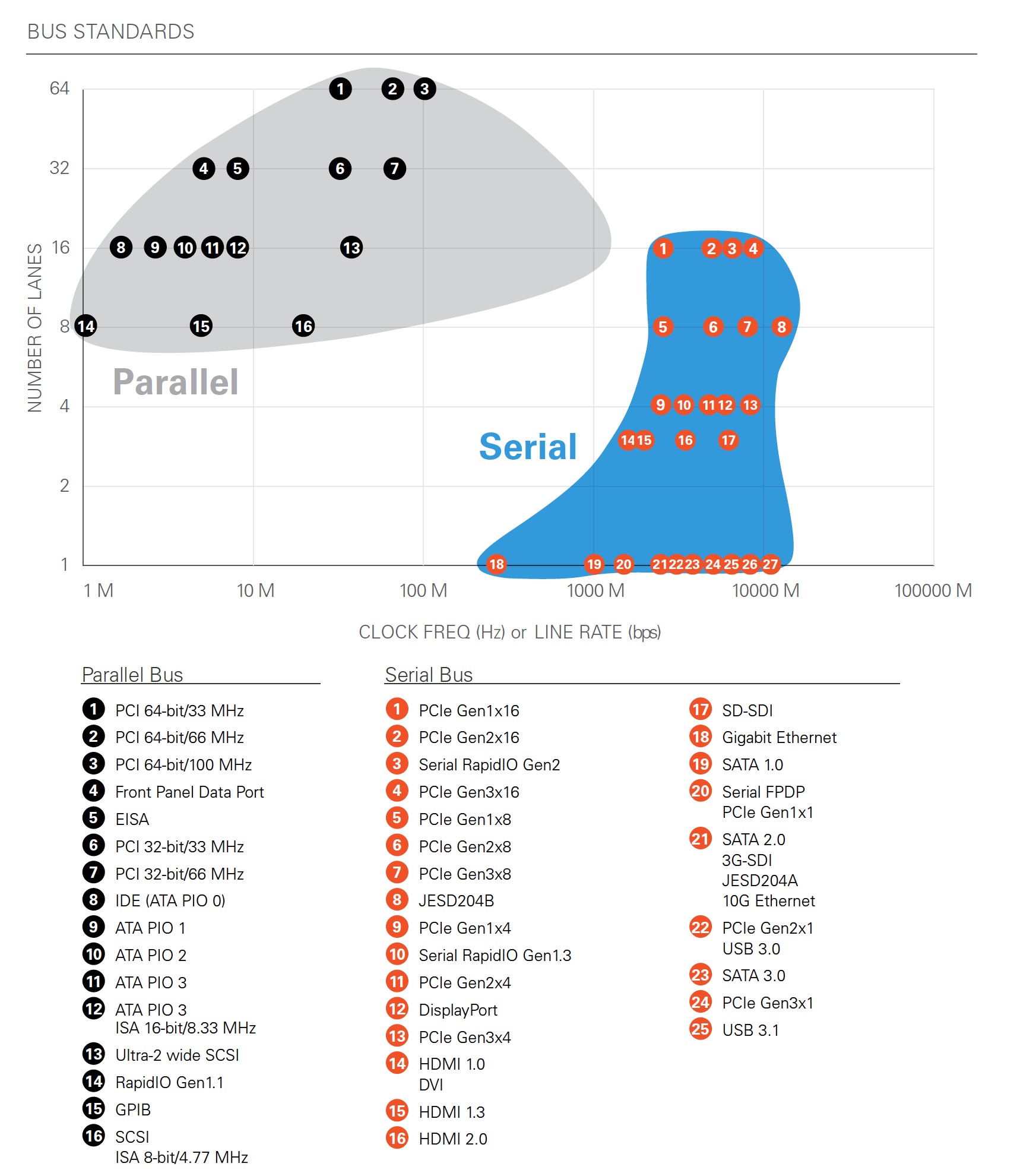

Die physikalische Begrenzung der Taktraten von parallelen Bussen liegt bei etwa 1 GHz bis 2 GHz, da die einzelnen Takt- und Datenleitungen einen Bitversatz verursachen, der bei höheren Raten zu Bitfehlern führt. Serielle Hochgeschwindigkeitsbusse senden kodierte Daten, die sowohl Daten- als auch Taktinformationen in einem einzigen differenziellen Signal enthalten, sodass Ingenieurinnen und Ingenieure die Geschwindigkeitsbegrenzungen paralleler Busse umgehen können. Heutzutage sind serielle Hochgeschwindigkeitsverbindungen mit Datenlanes von 10 Gbit/s üblich. Darüber hinaus können mehrere Lanes serieller Verbindungen kohärent miteinander gebündelt werden, um Kommunikationsverbindungen mit höheren Datendurchsätzen zu bilden.

Indem die Daten serialisiert und schneller gesendet werden, kann die Anzahl der Pins in integrierten Schaltungen (ICs) reduziert werden, was zu einer Verringerung der Gerätegröße beiträgt. Da die seriellen Lanes zudem mit einer viel höheren Taktrate arbeiten können, lässt sich ein besserer Datendurchsatz erzielen als mit parallelen Bussen.

Abbildung 2: Dieses Diagramm zeigt bekannte Busstandards und ihre jeweilige Anzahl von Lanes im Vergleich zu den Leitungsraten. Die seriellen Standards sind in der Lage, viel höhere Leitungsraten als die parallelen Standards zu erreichen, was zu einem höheren Durchsatz führt.

Nachteile

Obwohl eine reduzierte Pinanzahl die Designkomplexitäten verringern kann, stellen die erforderlichen höheren Geschwindigkeiten zusätzliche Herausforderungen an das Design. Bei Designs, die HF-Frequenzen erreichen, müssen Sie ähnliche analoge Überlegungen anstellen wie bei HF-Anwendungen, um eine ordnungsgemäße Signalintegrität zu gewährleisten. Um diese Probleme mit der Signalintegrität zu beheben, können Sie serielle Hochgeschwindigkeitsverbindungen verwenden, um Verfahren wie Kodierung, Akzentuierung und Entzerrung zu implementieren.

Schichten von seriellen Hochgeschwindigkeitsverbindungen

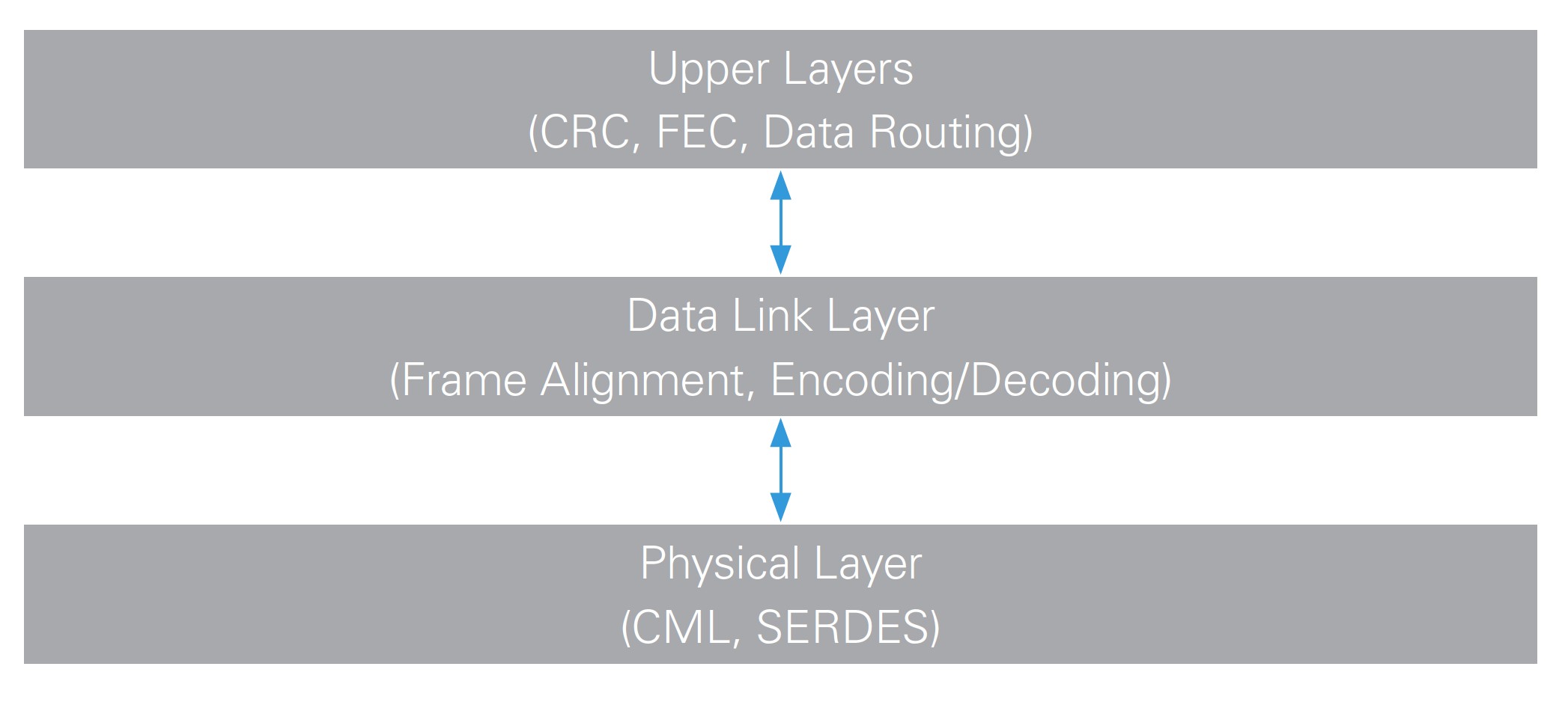

Damit eine serielle Verbindung funktioniert, muss jedes Ende zustimmen, innerhalb bestimmter Parameter zu arbeiten. Sie können diese Parameter auf mehrere Funktionsschichten abstrahieren.

Abbildung 3: Sie können Schichten oberhalb der Bitübertragungsschicht und der Sicherungsschicht hinzufügen. Diese Schichten variieren je nach Protokoll und Anwendung und sind normalerweise die am häufigsten anzupassenden Schichten.

Bitübertragungsschicht

Die Bitübertragungsschicht stellt die elektrische Kompatibilität zwischen den Geräten sicher und liefert synchron getaktete Bits an die Sicherungsschicht.

Elektrische Schnittstelle

Unterschiedliche serielle Protokolle für hohe Geschwindigkeiten definieren unterschiedliche Anforderungen an die elektrische Schnittstelle von Sender und Empfänger. Dadurch wird die elektrische Kompatibilität beim Verbinden des Sendegeräts mit dem Empfänger gewährleistet. Das elektrische Signal für serielle Hochgeschwindigkeitsverbindungen hat Schwierigkeiten, die extrem schnellen Anstiegs- und Abfallzeiten zu erreichen, die für die Kommunikation mit Geschwindigkeiten über 1 Gbit/s erforderlich sind, die elektromagnetischen Abstrahlungen zu minimieren und die Störfestigkeit durch Unterdrücken von Gleichtaktrauschen zu verbessern. Darüber hinaus steigen die Spitze-Spitze-Spannungen bei diesen Geschwindigkeiten selten über 1 V und elektrische Standards sind normalerweise die differenzielle Signalgebung bei niedrigen Spannungen (LVDS), emittergekoppelte Logik (ECL) oder die Stromschaltlogik (CML).

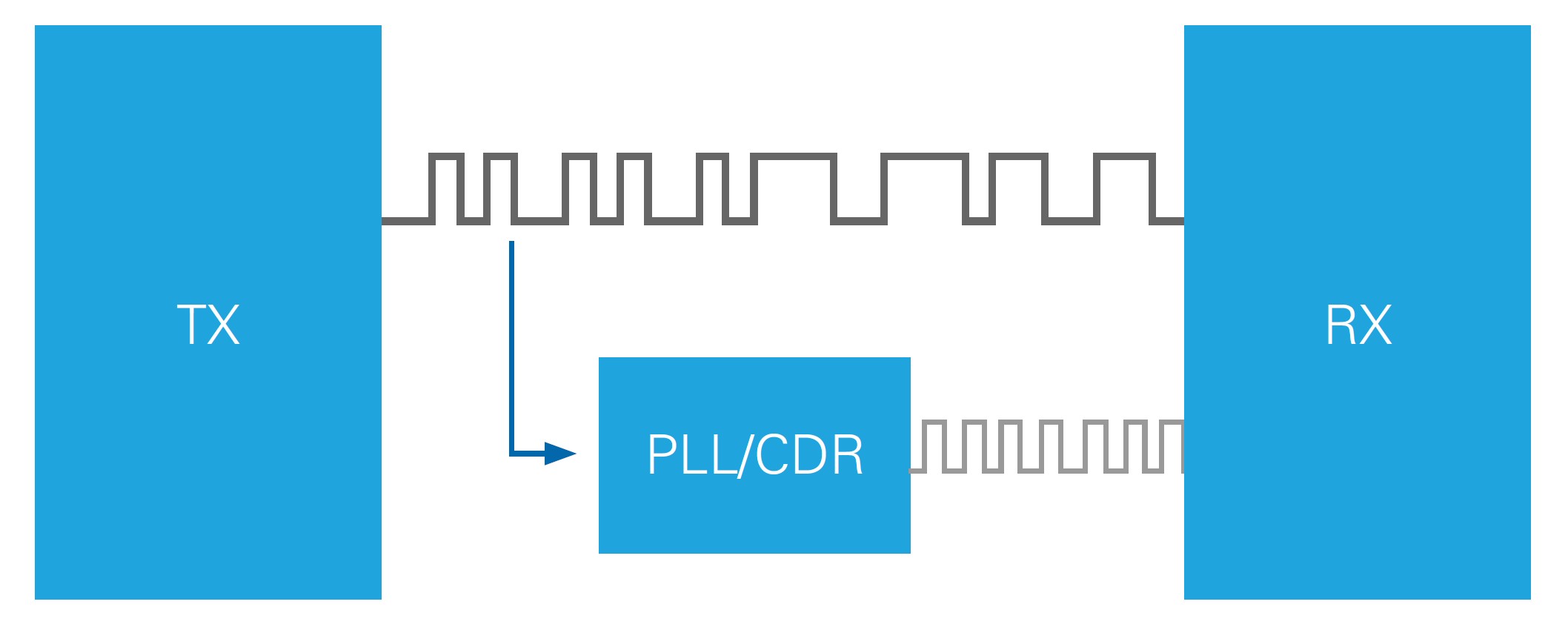

Takt- und Datenwiederherstellung

Eine weitere wichtige Funktion der Bitübertragungsschicht für serielle Hochgeschwindigkeitsverbindungen ist die Takt- und Datenwiederherstellung (CDR). CDR ist die Fähigkeit des Empfangsgeräts, den eingehenden Datenstrom zu takten, ohne dass ein tatsächliches Taktsignal erforderlich ist. Die Sicherungsschicht trägt dazu bei, indem sie durch Kodierung häufige Bitübergänge gewährleistet. Auf diese Weise können Phasenregelschleife(PLL)- und Phaseninterpolator(PI)-Schaltkreise den Sendetakt neu erzeugen und zur Erfassung des eingehenden Datenstroms mit minimalem Timing-Fehler verwenden.

Abbildung 4: Da die Kodierung auf der Sicherungsschicht häufige Übergänge zwischen 0 und 1 gewährleistet, kann der CDR-Schaltkreis den eingehenden Bitstrom per PLL verarbeiten und die kodierten Datenbits synchron abtasten.

Überlegungen zur Signalintegrität

Die Übertragung von Daten mit Bits, die mit Raten von 5 GHz oder mehr übergehen, stellt das Analogdesign vor Herausforderungen. Da die Übertragungsgeschwindigkeiten jetzt in den für HF-Designs typischen Frequenzbereichen liegen, ergeben sich Probleme mit der Signalintegrität. Sie müssen hochwertige Leiterplatten, Anschlüsse und Kabel verwenden, um bei diesen hohen Datenraten erfolgreich kommunizieren zu können. Leiterplattendesigner sollten außerdem mit der Theorie der Übertragungsleitungen vertraut sein, wenn sie für serielle Hochgeschwindigkeitsverbindungen entwerfen. Sie müssen in der Lage sein, Stichleitungen, Impedanzfehlanpassungen und Fehlanpassungen bei der Leiterbahnlänge zu vermeiden und geeignete Verfahren zur Minimierung von Signalverzerrungen anzuwenden.

Entzerrung

Bei der Entzerrung wird dem elektrischen Verhalten eines Kanals entgegengewirkt, um seinen Frequenzgang zu verbessern. Dies kann sowohl auf der Sender- als auch auf der Empfängerseite der Kommunikationsverbindung erfolgen, um die Verbindungsspanne zu verbessern. Der Begriff Entzerrung wird jedoch normalerweise in Bezug auf den Empfänger verwendet. Wenn das serielle Hochgeschwindigkeitssignal über die Leiterbahnen der Leiterplatte, durch Stecker und Kabel zum Empfänger geleitet wird, wirkt sich die Dämpfung nicht auf alle Frequenzkomponenten des Signals gleichermaßen aus und verursacht Signalverzerrungen. Mit den Entzerrungseinstellungen von Multi-Gigabit-Transceivern können verschiedene Frequenzen des Signals verstärkt oder gedämpft werden, bevor es abgetastet wird, um die Signal- und Verbindungsspanne zu verbessern. Viele Multi-Gigabit-Transceiver verfügen über eine automatische Entzerrung, um die idealen Einstellungen automatisch zu erkennen und die Entzerrer fortlaufend auf diese Einstellungen zu aktualisieren.

Akzentuierung

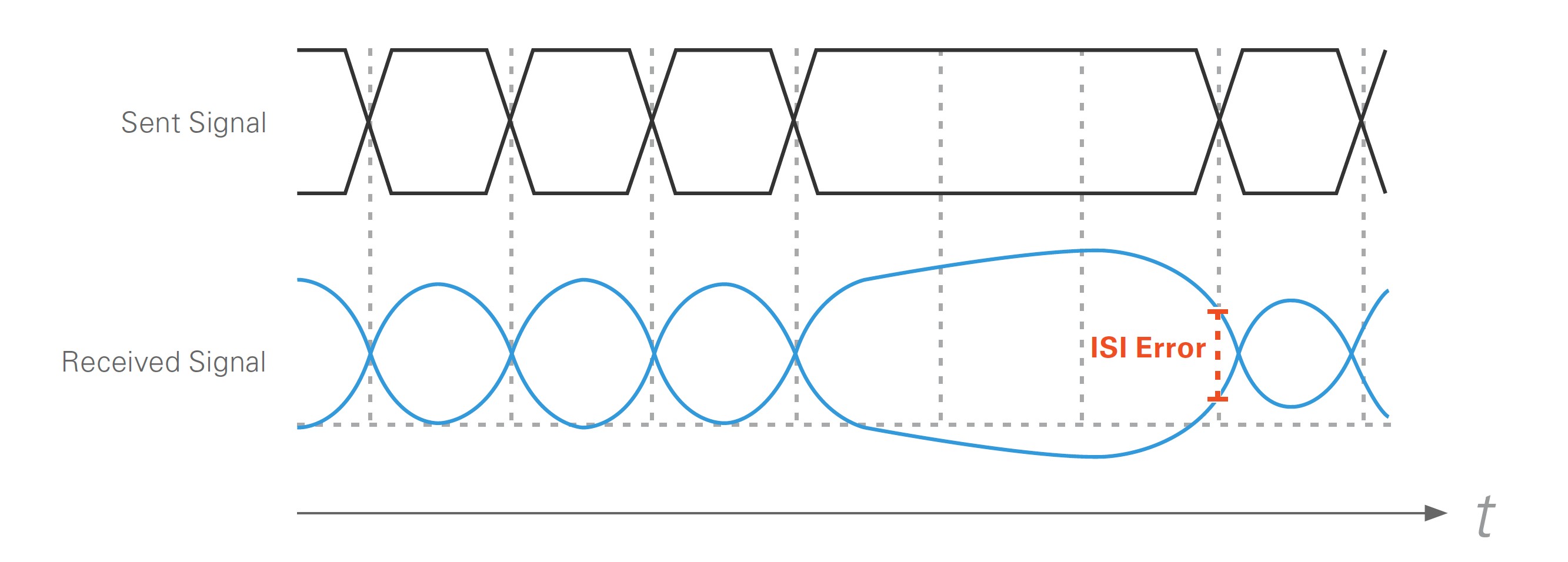

Akzentuierung bezieht sich normalerweise auf die Entzerrung auf der Senderseite einer seriellen Hochgeschwindigkeitsverbindung. Sie wird hauptsächlich verwendet, um analoge Herausforderungen zu überwinden, die durch Intersymbolinterferenz (ISI) entstehen. Bei hohen Leitungsraten beginnen sich die Datenbits bei der Übertragung gegenseitig zu beeinflussen. Wenn beispielsweise drei Einsen hintereinander übertragen werden, gefolgt von einer einzigen 0, hat die Datenleitung Schwierigkeiten, die 0 schnell auf Low zu setzen, da die Leitung eine positive Vorspannung aufgebaut hat.

Abbildung 5: Eine Signalverschlechterung aufgrund von ISI wird verursacht, wenn ein Mangel an Bitübergängen dazu führt, dass die Leitung eine Vorspannung aufbaut, wodurch es schwieriger wird, dass der erste Übergang zum entgegengesetzten Bit schnell erfolgt.

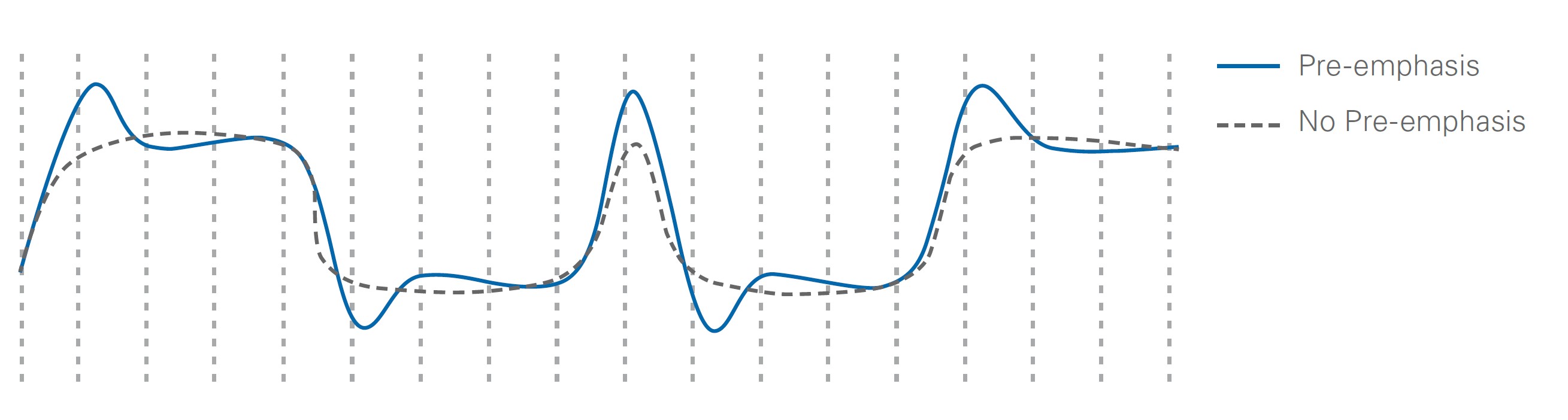

Es gibt zwei Möglichkeiten, eine Intersymbolinterferenz zu überwinden. Wenn Sie wissen, dass nur das erste Bit nach einem Übergang von Low zu High oder High zu Low Probleme aufweist, können Sie nur das erste Bit nach einem Übergang verstärken. Dies führt zu dem in Abbildung 6 gezeigten Signal.

Abbildung 6: Die Akzentuierung dient dazu, das erste Bit nach einem Signalübergang zu verstärken. Dies hilft, Probleme wie ISI zu beheben.

Ein gängigerer Ansatz zur Erzielung eines ähnlichen Signalverlaufs besteht darin, die Bits nach dem ersten Übergang zu dämpfen, anstatt das erste Bit zu verstärken. Dies wird durch die Hochpassfilterung erreicht, da die übergehenden Bits (höhere Frequenz) weniger gedämpft werden als die nicht übergehenden Bits.

Sicherungsschicht

Die Sicherungsschicht manipuliert Daten, um die Signalintegrität zu verbessern, eine erfolgreiche Kommunikation zu gewährleisten und physikalische Bits den Daten zuzuordnen. Funktionen, die dies ermöglichen, sind Kodierungsschemata und Steuerzeichen für die Ausrichtung, Taktkorrektur und Kanalbündelung.

Kodierungsschemata

Das Ziel der Kodierung besteht darin, häufige Bitübergänge für eine erfolgreiche Takt- und Datenwiederherstellung sowie einen DC-Abgleich für die Daten zu gewährleisten. Für eine erfolgreiche Takt- und Datenwiederherstellung muss das Kodierungsschema sicherstellen, dass das Datensignal genügend Übergänge hat, damit der CDR-Schaltkreis mit dem Datenstrom phasenstarr bleibt. Wenn die Phasenregelschleife im CDR-Schaltkreis aufgrund fehlender Übergänge nicht starr bleiben kann, kann der Empfänger die synchrone Taktung der Datenbits nicht garantieren, und es treten Bitfehler oder Verbindungsausfälle auf. Sie erreichen eine Takt- und Datenwiederherstellung, indem Sie sicherstellen, dass Symbole mit häufigen Bitübergängen übertragen werden, was dazu führt, dass den Daten Overhead-Bits hinzugefügt werden.

Der DC-Abgleich ist ebenfalls wichtig, um eine funktionierende serielle Verbindung aufrechtzuerhalten. Wenn Sie den DC-Abgleich nicht regulieren, können die Signale von ihren idealen logischen High- und Low-Pegeln abweichen und es können Bitfehler auftreten. Sie gewährleisten einen DC-Abgleich, indem Sie den statistischen Anteil von Einsen und Nullen in den übertragenen Symbolen abgleichen. Bei einem DC-abgeglichenen Signal ist die Anzahl der über die Zeit übertragenen Nullen und Einsen statistisch gesehen gleich.

8b/10b-Kodierung

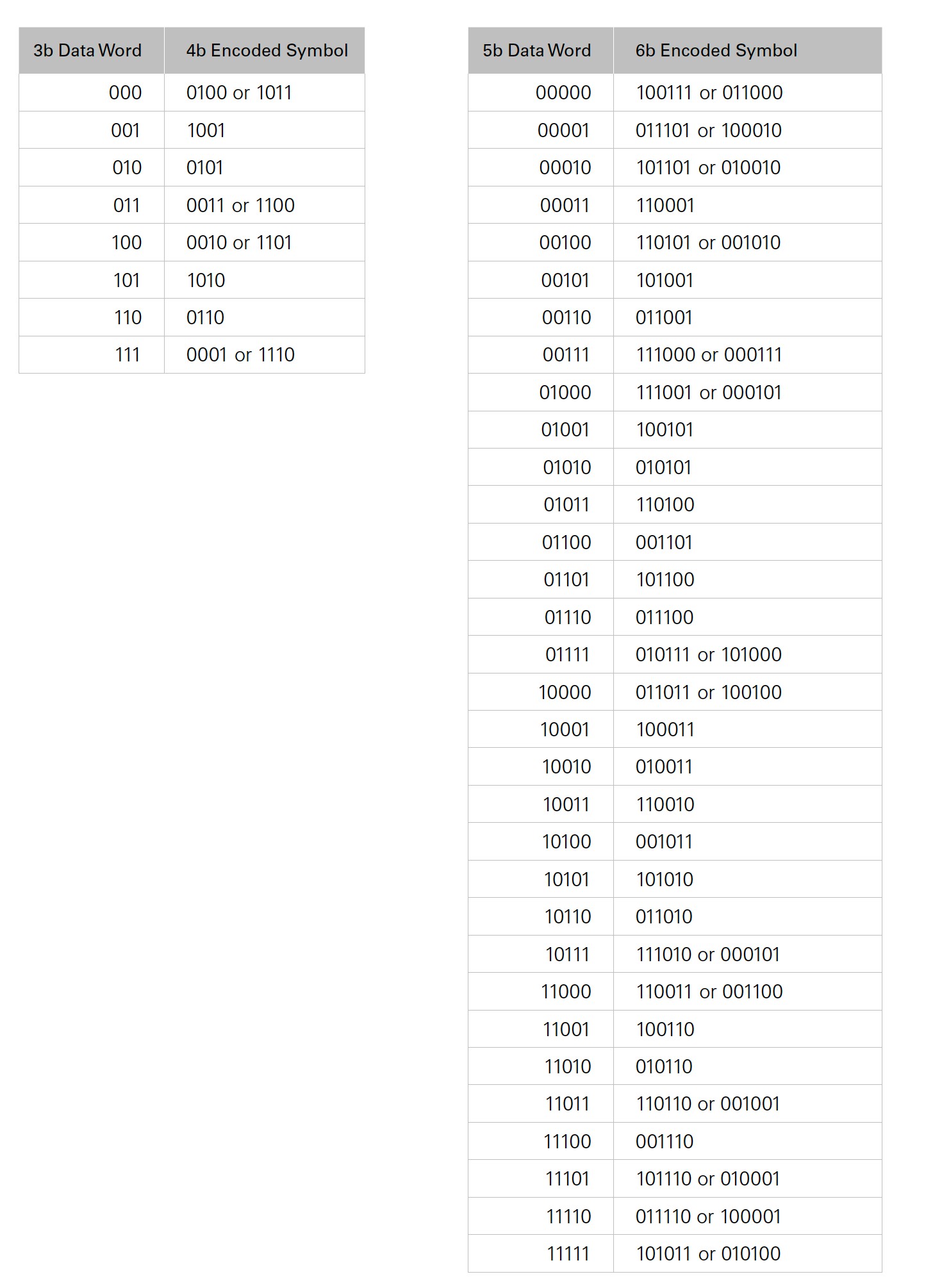

Ein übliches Kodierungsschema ist 8b/10b. Für jeweils acht Datenbits werden zwei zusätzliche Bits als Kodierungs-Overhead hinzugefügt. Diese beiden zusätzlichen Bits liefern viermal so viele Bitdarstellungen (Symbole) als acht Datenbits. Der 8b/10b-Encoder grenzt seine zahlreichen Symboloptionen ein, indem er die vordefinierten Symbole mit den meisten Übergängen und dem besten DC-Abgleich für die Zuordnung zu bestimmten Datenwörtern und Steuersymbolen auswählt. Er speichert diese Symbole in Zuordnungstabellen, die zum Kodieren und Dekodieren der Daten verwendet werden.

Wenn ein 8-Bit-Datenwort zur Kodierung bereit ist, teilt der Encoder das Datenwort in 5 Bits und 3 Bits auf und führt eine separate 5b/6b- und 3b/4b-Kodierung für das Datenwort durch. Er sendet die fünf niedrigstwertigen Bits an die 5b/6b-Tabelle und die drei höchstwertigen Bits an die 3b/4b-Tabelle.

Tabelle 1: Der Encoder kodiert 8b-Datenwörter, indem er die drei höchstwertigen Bits an eine 3b/4b-Tabelle und die fünf niedrigstwertigen Bits an eine 5b/6b-Tabelle sendet. Der Encoder kombiniert sie dann basierend auf der laufenden Disparität, um ein 10b-Symbol mit häufigen Übergängen für den CDR-Schaltkreis zu bilden.

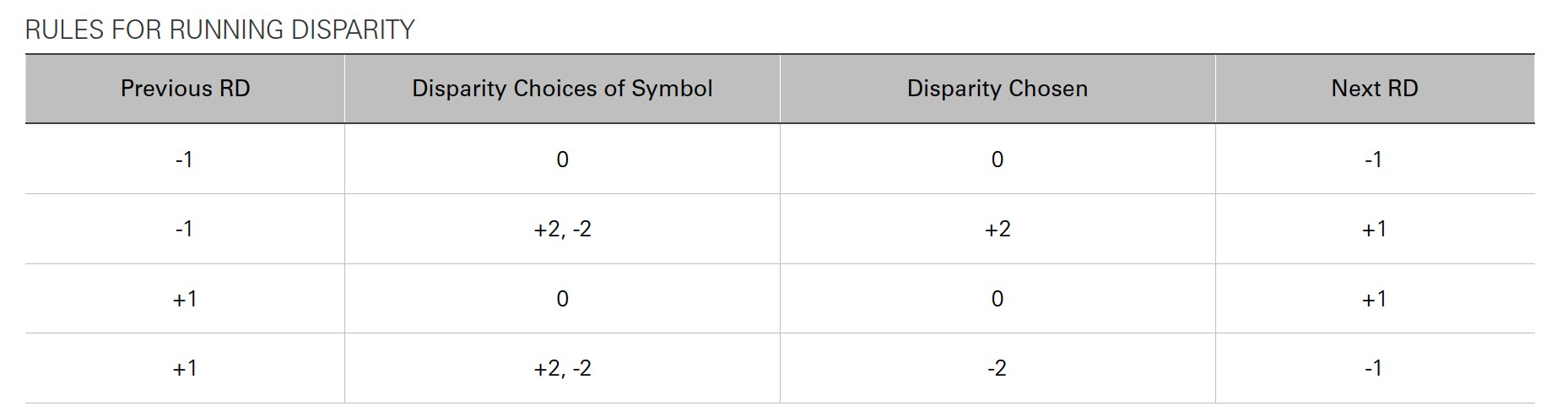

Im Idealfall haben alle Symbole die gleiche Anzahl von Nullen und Einsen, um den DC-Abgleich aufrechtzuerhalten. Dies gilt jedoch nicht für die Symbole in den 5b/6b- und 3b/4b-Tabellen. Daher wurden Regeln implementiert, um Entscheidungen auf der Grundlage eines Prinzips zu treffen, das als „laufende Disparität“ bekannt ist. Dies ist die kumulierte Differenz zwischen der Anzahl der übertragenen Einsen und Nullen. Es gibt nicht genügend Symbole mit der gleichen Anzahl von Einsen und Nullen, um acht Bits darzustellen. Daher werden einige Datenwörter mit zwei Symbolen dargestellt: einem Symbol mit mehr Nullen als Einsen und einem Symbol mit mehr Einsen als Nullen. Das 1101-Symbol aus der 3b/4b-Tabelle kann beispielsweise auch als 0010 dargestellt werden. Bei der Auswahl der zu verwendenden Symbolversion versucht der Encoder immer, die laufende Disparität abzugleichen. Die Disparität eines kompletten 8b/10b-Symbols beträgt immer 0, +2 oder -2. Tabelle 2 zeigt, wie der Encoder entscheidet, welches Symbol verwendet werden soll.

Tabelle 2: Die Regeln für die laufende Disparität bestimmen, welche Version des Codeworts verwendet wird, um einen DC-Abgleich sicherzustellen.

Ziehen Sie beispielsweise in Betracht, das Datenwort 10010001 zu kodieren. Die drei höchstwertigen Bits (100) werden an die 3b/4b-Tabelle und die fünf niedrigstwertigen Bits (10001) an die 5b/6b-Tabelle gesendet. Wenn dies das erste Wort ist, das über die Leitung gesendet wird, geht der Encoder von einer Disparität von -1 aus. Daher wird in diesem Beispiel angenommen, dass die laufende Disparität -1 ist. Der 5b/6b-Teil hat keine Wahl zu treffen, während der 3b/4b-Teil entscheidet, ob die Disparität +2 oder -2 beträgt. Da die laufende Disparität -1 ist, wird der 3b/4b-Code mit der Disparität +2 (1101) ausgewählt. Wenn die 3b/4b- und 5b/6b-Codes kombiniert werden, ergibt sich insgesamt das kodierte Symbol 1101100011. Nachdem dieses Symbol übertragen wurde, beträgt die laufende Disparität nun +1 = -1 + 2.

64b/66b-Kodierung

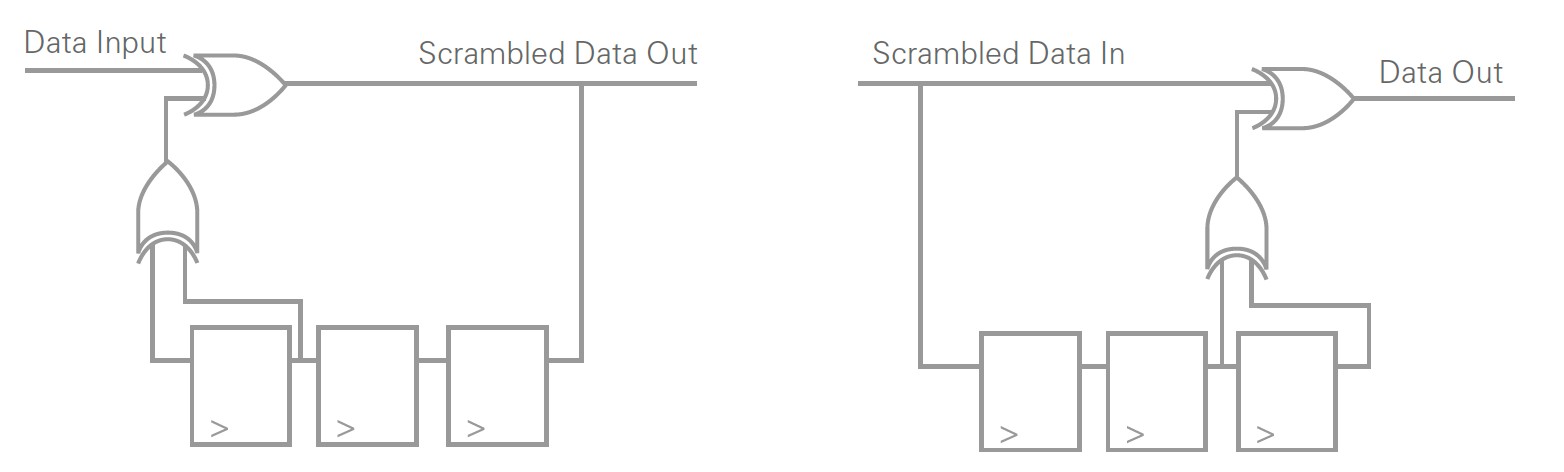

Mit einem anderen Ansatz als bei der 8b/10b-Kodierung können mit der 64b/66b-Kodierung ähnliche Aufgaben erfüllt werden. Anstelle von Codetabellen wird die Verwürfelung verwendet. Für die Verwürfelung ist eine Hardwareschaltung erforderlich, die eine hohe Wahrscheinlichkeit für mehrere, einigermaßen gleichmäßig verteilte Nullen und Einsen bietet. Durch die Verwürfelung können die kodierten Daten zufällig mit häufigen Übergängen erscheinen, können aber auf der Empfängerseite noch entwürfelt werden.

Abbildung 7: Eine Verwürfelungsschaltung lässt die Ausgabedaten zufällig und DC-abgeglichen erscheinen, aber die Daten können immer noch am Empfänger entwürfelt werden. Die Verwürfelung ist eine Alternative zur Kodierung von Daten mit einer Zuordnungstabelle.

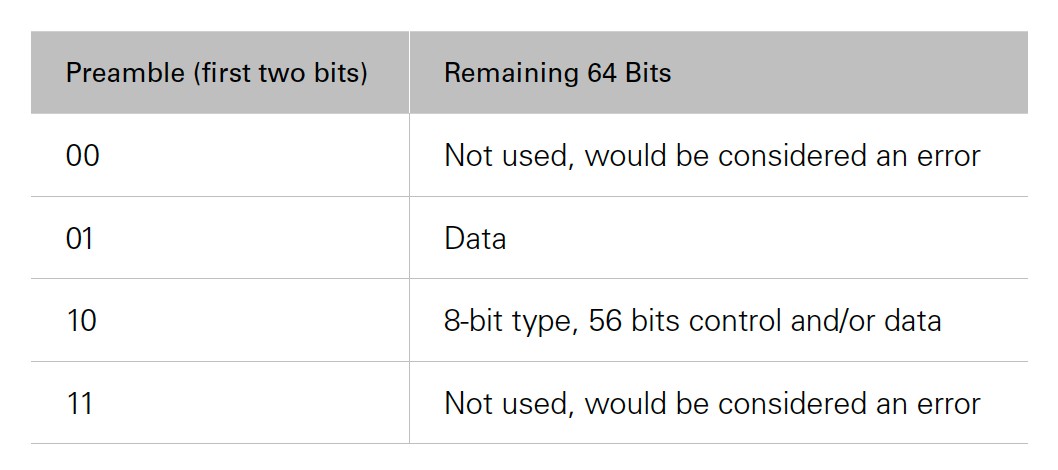

Die ersten beiden der 66 Bits gelten als Präambel und geben Informationen über die verbleibenden 64 Bit an. Der Hauptvorteil von 64b/66b im Vergleich zu 8b/10b ist der geringere Overhead. Die 64b/66b-Kodierung hat etwas mehr als 3 % Overhead, während die 8b/10b-Kodierung 20 % Overhead hat. Ein Nachteil der 64b/66b-Kodierung besteht darin, dass sie nicht wie die 8b/10b-Kodierung durch den DC-Abgleich beschränkt ist. Obwohl sich die Verwürfelungsschaltungen als sehr gut darin erwiesen haben, zufällig zu erscheinen und eine statistisch unbedeutende DC-Differenz zu haben, ist die 64b/66b-Kodierung nicht wie die 8b/10b-Kodierung beschränkt.

Tabelle 3: Die ersten beiden Bits eines 64b/66b-Symbols werden als Präambel betrachtet. Die Präambel stellt dem Decoder Informationen über die 64 Bits zur Verfügung, die auf die Präambel folgen. Die Bedeutung der Präambel in Tabelle 3 gilt für 10-Gigabit-Ethernet.

64b/67b

Bestimmte elektronische Geräte reagieren mit der Zeit zu empfindlich auf den DC-Offset. Dies kann beim 64b/66b-Kodierungsschema der Fall sein. Es könnte für Designer nicht attraktiv sein, da der DC-Offset nicht beschränkt ist. In diesen Situationen müssen die Ingenieurinnen und Ingenieure den höheren Overhead (20 %) des 8b/10b-Schemas in Kauf nehmen. Das 64b/67b-Schema fügt ein zusätzliches Overhead-Bit hinzu, wodurch die laufende Disparität auf ±96 begrenzt werden kann.

Der Sender überwacht die laufende Disparität und berechnet die neue Disparität der verwürfelten Codewörter. Wenn das neue Codewort die Disparitätszahl verringert, wird dieses Symbol übertragen. Wenn das neue Codewort die Disparitätszahl erhöht, dreht der Kodierer die 64 verwürfelten Bits um (bei einer Disparität von Null muss die Präambel nicht umgedreht werden). Das zusätzliche Bit wird als Invertierungsbit bezeichnet und teilt dem Decoder mit, ob der Decoder die Daten invertieren muss oder nicht. Auf diese Weise kann Chipelektronik, die empfindlich auf den DC-Offset reagiert, von einem Kodierungsschema mit geringem Overhead profitieren, das auch einen beschränkten DC-Offset aufweist.

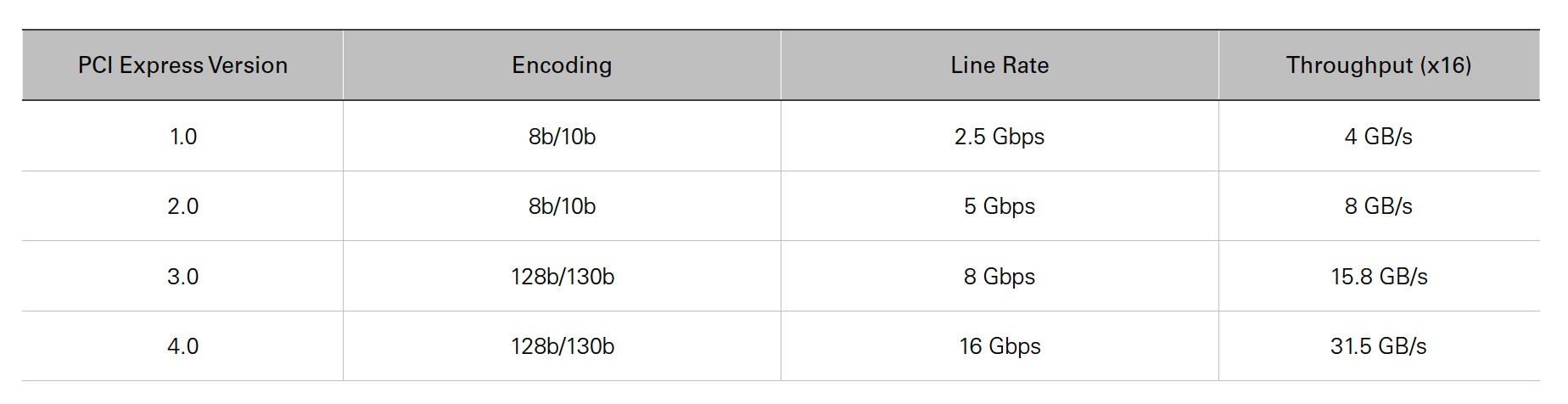

128b/130b

PCI Express 1.0 und 2.0 verwenden beide 8b/10b, während PCI Express 3.0 und 4.0 auf 128b/130b umgestiegen sind, um einen höheren Datendurchsatz mit einer erreichbaren Leitungsrate zu erzielen. Stellen Sie sich das 128b/130b-Schema als 64b/66b-Schema mit doppelt so vielen Nutzdaten und immer noch nur zwei Präambel-Bits vor. Tabelle 4 zeigt die Spezifikationen für PCI Express.

Tabelle 4: In dieser Tabelle sind die Spezifikationen für die vier PCI-Express-Generationen aufgeführt. PCI Express 3.0 und 4.0 wurden auf 128b/130b umgestellt, um den Datendurchsatz zu erhöhen und gleichzeitig die Leitungsraten auf einer besser kontrollierbaren Geschwindigkeit zu halten.

Steuersymbole (K-Zeichen)

Steuersymbole, im Zusammenhang mit der 8b/10b-Kodierung auch als K-Zeichen bezeichnet, sind eine wichtige Funktion von seriellen Hochgeschwindigkeitsverbindungen. Es handelt sich dabei um Symbole, die von Daten unterschieden werden können, sodass der Empfänger sie für verschiedene Steueraufgaben verwenden kann, z. B. für die Byte-Ausrichtung vor der Dekodierung, für Verfahren zur Taktkorrektur und für die Kanalbündelung für die Datenkohärenz über mehrere Lanes hinweg.

Ausrichtung und Kommaerkennung

Damit die Dekodierung korrekt funktioniert, muss der Empfänger die richtigen Wortgrenzen der kodierten Daten kennen. Der Empfänger durchsucht die eingehenden Daten nach dem Steuerzeichen, das auch als Komma bezeichnet wird, wenn es zur Ausrichtung im 8b/10b-Schema verwendet wird. Das Steuerzeichen definiert die Begrenzung der kodierten Daten. Sobald der Empfänger das Ausrichtungszeichen erkannt hat, verfügt er über ein Konzept der Wortgrenzen für die kodierten Daten, sodass die kodierten Daten an die Dekodierlogik gesendet werden können.

Taktkorrekturzeichen

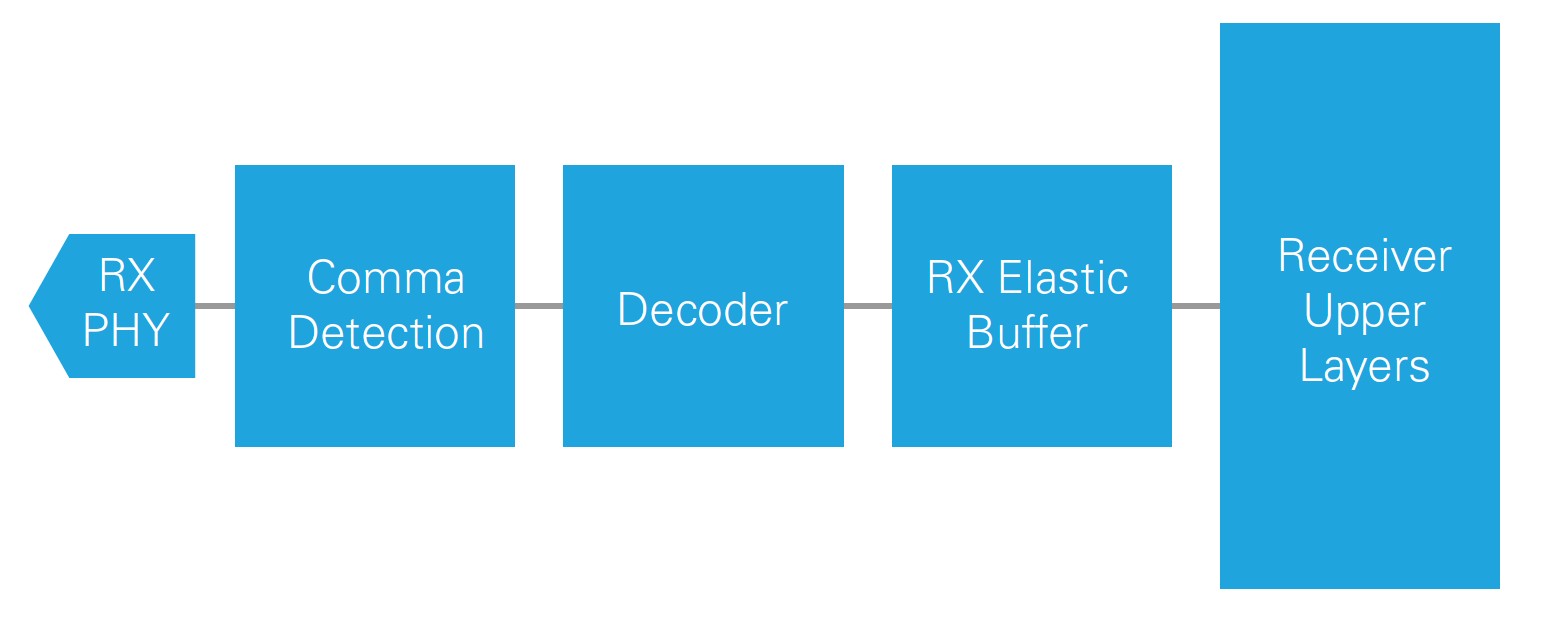

Eine Taktkorrektur ist immer dann erforderlich, wenn der Sendetakt nicht auf dieselbe Quelle wie der Empfangstakt eingestellt ist. Selbst wenn diese Takte die gleiche Nennfrequenz haben, driften sie aufgrund kleiner Ungenauigkeiten der Taktfrequenz langsam auseinander. Mit einem FIFO-Speicherpuffer, kurz auch elastischer Puffer, kann der Empfänger geringfügige Taktunterschiede zwischen Sender und Empfänger berücksichtigen und eine Taktkorrektur implementieren.

Abbildung 8: Der elastische RX-Puffer zwischen dem Decoder und den oberen Schichten des Empfängers ist für die Implementierung der Taktkorrektur erforderlich. Er puffert Daten, um Fehler durch auseinanderdriftende, nicht synchronisierte Takte zu vermeiden, und ermöglicht die Kommunikation zwischen zwei Geräten, ohne dass diese einen gemeinsamen Bezugstakt haben.

Die Logik der Taktkorrektur stellt sicher, dass bei dem elastischen Puffer niemals ein Unter- oder Überlauf entsteht. Wenn der Sendetakt etwas schneller läuft als der Empfangstakt aus dem elastischen Puffer liest, kann es zu einem Überlauf kommen, wenn Sie keine Verfahren zur Taktkorrektur einsetzen. Wenn der Sendetakt etwas langsamer läuft als die Leselogik des Empfängers, kann es zu einem Unterlauf kommen, wenn Sie keine Taktkorrektur haben.

Ein Steuerzeichen wird als Taktkorrekturzeichen gewählt. Der Sender sendet dieses Taktkorrekturzeichen periodisch mit echten Daten verschachtelt und die Frequenz dieses Taktkorrekturzeichens hängt von den Taktkorrekturanforderungen der Anwendung und dem Hardwaredesign ab. Wenn die Taktkorrekturlogik des Empfängers feststellt, dass bei dem elastischen Puffer des Empfängers Unterlauf entstehen wird, kann die Korrekturlogik des Empfängers zusätzliche Taktkorrekturzeichen einfügen, um sicherzustellen, dass kein Pufferunterlauf auftritt. Wenn die Taktkorrekturlogik feststellt, dass der elastische Puffer zu voll wird und kurz vor dem Überlaufen steht, kann sie die Taktkorrektursequenzen im Puffer verwerfen, um zusätzlichen Platz für Daten zu schaffen.

Kanalbündelung

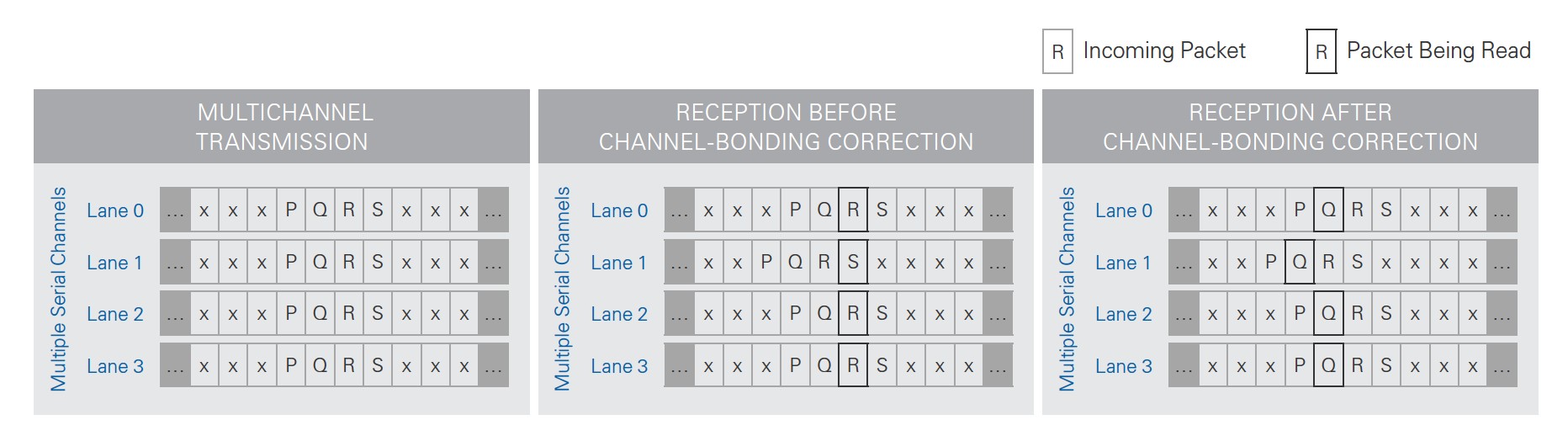

Wenn die Leitungsrate und das Kodierungsschema den von Ihnen auf einer einzigen seriellen Lane benötigten Datendurchsatz nicht erreichen, können Sie mehrere Lanes verwenden. HDMI-Standards verwenden beispielsweise drei serielle Datenlanes, um ihre Gesamtdatenbandbreite zu erreichen. Beim Senden von Daten über mehrere Lanes führen Ausbreitungsverzögerungen dazu, dass die Daten zu unterschiedlichen Zeiten an den einzelnen Empfangslanes beim Empfänger ankommen. Je nach Anwendung kann es erforderlich sein, die Daten über alle Lanes am Empfänger auszurichten. Dieser Prozess wird als Kanalbündelung bezeichnet. Der elastische Puffer in jeder empfangenden Lane des Empfängers, der für die Taktkorrektur verwendet wird, wird auch für die Kanalbündelung genutzt.

Um eine Kanalbündelung zu erreichen, müssen Sie ein spezielles Steuerzeichen wählen und es für Kanalbündelung reservieren. Die serielle Verbindung hat eine Master-Lane, die restlichen werden als Slaves betrachtet. Der Master und alle Slaves senden gleichzeitig das Kanalbündelungszeichen von den Sendern. Wenn der Master-Empfänger die Kanalbündelungssequenz an einer bestimmten Position des elastischen Puffers sieht, weist er alle Slaves an, ihre Bündelungssequenzen zu suchen. Anschließend passt der Master-Empfänger die Lesezeiger aller elastischen Puffer an den Offset der Position der Kanalbündelungssequenz an. Da jede Datenlane ihren eigenen Offset für ihren eigenen elastischen Puffer hat, kann der Empfänger von verschiedenen Positionen jedes elastischen Puffers lesen, was zum Lesen ausgerichteter Daten führt.

Abbildung 9: Die Kanalbündelung ändert die Lesezeiger des elastischen Puffers an jeder Empfangslane, damit der Empfänger synchrone Daten über mehrere Datenlanes hinweg lesen kann.

Idle-Steuerzeichen

Ein weiterer wichtiger Anwendungsfall für Steuerzeichen ist das Idle-Steuerzeichen. Damit die Takt- und Datenwiederherstellung phasenstarr bleibt, muss der Sender kontinuierlich Bits senden. Wenn der Sender keine Daten zu senden hat, muss ein Idle-Steuerzeichen gesendet werden. Dies ist ein weiteres vom Protokoll festgelegtes Steuerzeichen, und der Empfänger weiß, dass diese Zeichen keine echten Daten sind.

Zusätzliche obere Schichten

Zusätzliche obere Schichten befinden sich oberhalb der Sicherungsschicht, damit Sie die Kommunikation an Ihre spezifischen Anforderungen anpassen können. Einige Protokolle haben spezifische Standards für Funktionen der oberen Schicht, andere Protokolle überlassen dies Ihnen. Zu den üblichen Kommunikationsanpassungen gehören Fehlerprüfung/-korrektur, Header-Informationen für die paketbasierte Kommunikation oder sogar Verbindungsstatusangaben.

Die Schichten oberhalb der Sicherungsschicht und der Bitübertragungsschicht sind die Schichten, die am häufigsten an anwendungsspezifische Anforderungen angepasst werden. Einige Beispiele für gängige Anpassungen der oberen Schichten sind die Fehlererkennung und -korrektur durch eine zyklische Redundanzprüfung (CRC) und die Vorwärtsfehlerkorrektur (FEC). Als Kompromiss bei der Effizienz der Datenübertragung können Sie Schemata zur Erkennung oder Korrektur von Fehlern verwenden. CRC implementiert Regeln zur Erkennung von Bitfehlern bei der Übertragung, kann die Fehler jedoch nicht korrigieren. Sie können die Anwendung so anpassen, dass Daten erneut angefordert werden. Im Gegensatz dazu enthält FEC zusätzliche Fehlerkorrekturinformationen in den übertragenen Daten, die es dem Empfänger ermöglichen, sich von einer begrenzten Anzahl von Bitfehlern zu erholen. Dies ist nützlich bei verrauschten Kanälen oder bei so hohen Kommunikationsraten, dass Bitfehler aufgrund der Signalintegrität häufiger vorkommen. Die Einbeziehung von FEC ist eine Designentscheidung, bei der die Datenrateneffizienz den gelockerten Anforderungen an die Signalintegrität geopfert wird.

Schlussfolgerungen

Für eine erfolgreiche Kommunikation müssen Sie viele Herausforderungen auf mehreren Schichten der seriellen Hochgeschwindigkeitsverbindung meistern. Die Kenntnis der verschiedenen Prinzipien auf jeder Ebene hilft Ihnen bei der Implementierung und dem Testen der verschiedenen Schichten. Damit eine Schicht funktionieren kann, müssen die darunter liegenden Schichten richtig funktionieren. Wenn Sie eine der vielen definierten Spezifikationen für Bitübertragungs- und Sicherungsschichten verwenden, müssen Sie die Details für die unteren Schichten nicht selbst bestimmen. Ein weiterer Vorteil der Verwendung einer standardisierten Bitübertragungsschicht und einer Sicherungsschicht ist das Internetprotokoll (IP), das alle diese Details für Sie implementiert. Ein hervorragendes Beispiel hierfür ist das Xilinx-Aurora-Protokoll, ein kostenloses IP, das ein schlankes Sicherungsschicht-Protokoll für die serielle Punkt-zu-Punkt-Kommunikation implementiert. Es hilft Ihnen, die kleinen Details wie Taktkorrektur, Kanalbündelung, Idle-Steuerzeichen und Kodierung/Dekodierung zu abstrahieren und sich auf die oberen, anwendungsspezifischen Schichten zu konzentrieren.

Durch die Vorteile der geringeren Größe und des geringeren Stromverbrauchs, gepaart mit einer höheren Leistung, werden serielle Hochgeschwindigkeitsverbindungen immer beliebter. Die Kommunikationsindustrie verbessert kontinuierlich die seriellen Hochgeschwindigkeitstechnologien, um höhere Leitungsraten zu erreichen und die Welt der Big Data zu ermöglichen.