了解直接数字频率合成(DDS)

概览

了解直接数字频率合成的基本原理和理论,以及如何将其应用于函数发生器和任意函数发生器。

内容

简介

生成信号白皮书中探讨了信号发生器(如函数发生器和任意函数发生器(AFG))如何输出所需的模拟信号,以及一些信号发生器如何使用直接数字频率合成(DDS)技术以精确的频率输出信号。本文将介绍使信号源能够在信号生成中达到亚赫兹精度的组件和技术。

工作原理

不同于按照波形存储顺序逐一输出采样的传统方法,使用DDS技术的信号发生器通过独特的存储器访问和时钟机制以精确的频率生成信号。任意波形发生器(AWG)使用传统信号生成方法。AWG可生成复杂的用户定义波形,但生成波形的频率精确度受限。这是因为存在限制因素:波形必须从AWG的存储器中逐点生成,以及用于控制生成点间时间的采样时钟具有有限的频率。

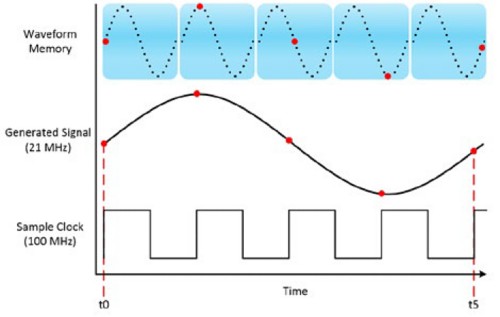

使用DDS的函数发生器和AFG会在存储器中存储周期波形单个周期的大量点。DDS技术使函数发生器或AFG能够选择从存储器输出的采样。由于函数发生器或AFG在波形中选择下一个采样时不受限,因此可以生成精确频率的信号。图1以图形方式显示了函数发生器或AFG生成21 MHz正弦波的方式,其中正弦波并非是100 MHz采样时钟的整数部分。100 MHz采样时钟仍可驱动数模转换器(DAC)输出的更新速率;因此,采样时钟越快,生成的信号波形就越准确。

图1:在支持DDS的硬件中,您无需按照存储器中的存储顺序选择采样。这使得100 MHz采样时钟能够准确地创建21 MHz正弦波

在上述特定情况下,AFG使用100 MHz采样时钟驱动DAC,但生成信号的频率取决于从波形存储器位置选择采样的方法。下文将介绍可实现采样选择的控制逻辑的组件。

功能概述

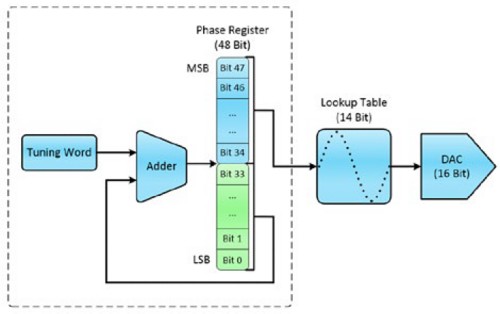

DDS实现需要3个主要的硬件构建模块:(a)采样时钟、(b)相位累加器和(c)查找表,后者是可编程只读存储器的实现。图2所示为从硬件模块之间的高级流程。

图2:DDS架构的硬件结构框图

a.采样时钟

采样(参考)时钟用于创建频率控制字、更新相位累加器值以及驱动数模转换。采样时钟决定DAC何时输出采样,但并不直接决定输出信号的频率。

b.相位累加器

相位累加器是支持函数发生器或AFG以精确频率输出的组件集合。为了以精确频率生成信号,相位累加器包括3个通用组件。首先,相位累加器使用频率控制字指定信号的频率。频率控制字是一个24至48位的数字字,用于指定要在波形存储器中跳转的采样数。第2个组件是加法器,用于获取频率控制字并将其与相位寄存器的余数相加。加法器将得到的新数值输出至相位寄存器。相位累加器的最后一个组件是相位寄存器,它获取新的数字字,并用其来指定查找表中要输出的下一个采样点的存储器地址。相位寄存器获取查找表存储器地址中未使用的剩余最高有效位,并将其重新提供给加法器,以确保频率精确度随时间变化。

c. 查找表

当寄存器地址随时间推移而增加时,相位寄存器的输出看起来像一个数字斜坡,并以频率控制字指定的速率变化。因此,相位寄存器的输出指向查找表中所需的波形采样地址,从而输出所需波形。然后,查找表在所提供的存储器地址处提供DAC要生成的正确振幅和相位的数字字。

频率捷变即快速改变波形频率和连续改变相位的能力,是DDS架构的主要优势之一。使用DDS的AFG可非常快速地改变波形频率,因为只需改变频率控制字即可改变波形频率。

常见应用

如上所述,DDS技术具有2个主要优势。DDS技术的首要优势是生成信号的频率精度。鉴于函数发生器或AFG生成的信号具有出色的频率精度,该功能为实现极其精确的组件测试提供了机会。

DDS技术的第2个主要优势是能够极快地改变生成信号的频率并连续更改相位。由于能够快速实现频率变化,还可以通过使用突破设备向待测设备提供信号的限制来对设备进行压力测试,您可以在特定范围内进行更有效的组件测试。

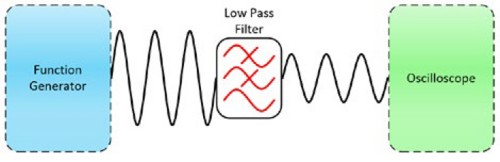

使用DDS技术的AFG极具价值的一个具体例子就是准确的滤波器特性分析。只有当提供给滤波器的信号由AFG准确生成并且滤波后的信号由示波器准确测量时,AFG才能准确地对滤波器进行特性分析。图3所示为滤波器特性分析的典型测试设置。

图3:具有DDS功能的函数发生器、低通滤波器和示波器的滤波器特性分析应用结构框图

总结

- 未采用DDS技术的信号发生器通过按照采样时钟的频率逐点输出存储的波形来生成波形。

- 采用DDS技术的信号发生器可生成频率精度极高的多频率周期性波形。这要得益于独特的存储器访问和时钟机制。

- 3个更高级别的硬件模块用于实现DDS技术:采样时钟、相位累加器和查找表。

- 采样时钟能够创建频率控制字、更新相位累加器值,并驱动DAC输出速率。

- 相位累加器以频率控制字为输入,并为查找表提供下一个输出采样的数字存储器地址。

- 查找表将周期波形存储为数字采样。查找表从相位累加器获取存储器地址,并将该地址的数字波形采样提供给DAC。

- 采用DDS技术的信号发生器可用于有精确频率生成或频率捷变需求的应用。

- 对于需要超大、复杂和用户定义波形的应用,应最好使用任意波形发生器,而不是采用DDS技术的任意函数发生器。