DDS (직접 디지털 파형합성) 이해하기

개요

직접 디지털 파형합성의 기본 원리와 이론, 그리고 이를 함수 생성기와 임의 함수 생성기에 적용하는 방법을 알아봅니다.

내용

개요

신호 생성 백서에서는 함수 생성기와 임의 함수 생성기 (AFG)와 같은 신호 생성기에서 필요로 하는 아날로그 신호를 출력하는 방법과 일부 신호 생성기에서 DDS (직접 디지털 파형합성) 기술을 사용하여 정확한 주파수에서 신호를 출력하는 방법의 기초를 살펴봅니다. 이 문서에서는 신호 소스가 신호를 생성할 때 서브 헤르츠를 정확히 구현하는 데 필요한 구성요소와 기술에 대해 살펴봅니다.

작동 원리

신호 생성기는 DDS를 사용하며 고유한 메모리 액세스와 클럭 메커니즘을 통해 정확한 주파수에서 신호를 생성합니다. 이는 웨이브폼이 저장된 순서대로 각 샘플을 출력하는 기존의 방법과는 다릅니다. AWG (임의 웨이브폼 생성기)는 기존의 신호 생성 방법을 활용합니다. AWG는 복잡한 사용자 정의 웨이브폼을 생성할 수 있지만 웨이브폼이 생성되는 정확한 주파수가 한정적입니다. 이는 웨이브폼이 AWG의 메모리에서 포인트 단위로 생성되어야 하고 생성된 각 포인트 간 시간을 제어하는 샘플 클럭이 한정된 수의 주파수를 갖는다는 제약 때문입니다.

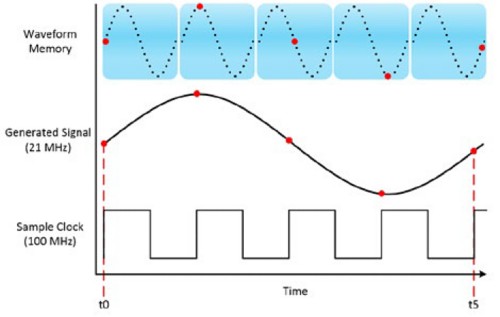

DDS를 사용하는 함수 생성기와 AFG는 주기적인 웨이브폼의 단일 사이클에 대해 많은 수의 포인트를 메모리에 저장합니다. DDS 기술을 사용하면 함수 생성기 또는 AFG가 메모리에서 출력할 샘플을 선택할 수 있습니다. 함수 생성기 또는 AFG는 웨이브폼에서 다음 샘플을 선택할 때 제한을 받지 않기 때문에 정확한 주파수에서 신호를 생성할 수 있습니다. 그림 1은 함수 생성기 또는 AFG에서 21MHz 사인파를 어떻게 생성하는지 그래픽으로 설명한 것입니다. 여기서 21MHz 사인파는 100MHz 샘플 클럭의 정수 나눗셈이 아닙니다. 100 MHz 샘플 클럭은 변함없이 DAC 출력의 업데이트 속도를 구동합니다. 따라서 샘플 클럭이 빠를수록 생성된 신호의 모양이 더 정확해집니다.

그림 1: DDS 지원 하드웨어에서 반드시 메모리에 저장된 순서대로 샘플이 선택되는 것은 아닙니다. 따라서 100 MHz 샘플 클럭은 21 MHz 사인파를 정확히 생성할 수 있습니다.

위와 같이 특정한 경우에 AFG는 100 MHz 샘플 클럭을 사용하여 DAC를 구동하지만 생성된 신호의 주파수는 웨이브폼 메모리 위치에서 샘플을 선택하는 방법을 통해 생성됩니다. 다음 섹션에서는 샘플 선택의 이면에 있는 컨트롤 로직을 구현하는 구성요소에 대해 설명합니다.

기능 개요

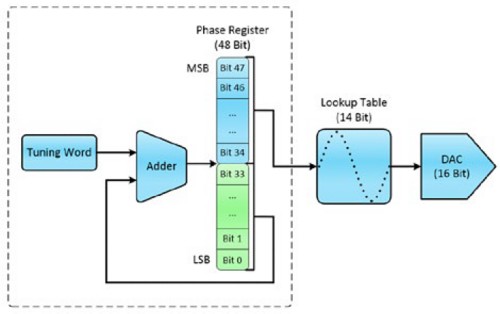

DDS를 구현하려면 (a) 샘플 클럭, (b) 위상 어큐뮬레이터, (c) 프로그램 가능한 읽기 전용 메모리의 구현인 룩업 테이블의 세 가지 주요 하드웨어 빌딩 블록이 필요합니다. 그림 2는 하드웨어 블록에서 하드웨어 블록으로의 상위 레벨 흐름을 보여줍니다.

그림 2: DDS 아키텍처의 하드웨어 블록다이어그램

a. 샘플 클럭

샘플 클럭 또는 참조 클럭은 주파수 튜닝 워드를 생성하고 위상 어큐뮬레이터 값을 업데이트하며 디지털-아날로그 간 변환을 구동하는 데 사용됩니다. 샘플 클럭은 DAC에서 샘플이 출력되는 시기를 결정하지만 출력 신호의 주파수는 직접적으로 결정하지 않습니다.

b. 위상 어큐뮬레이터

위상 어큐뮬레이터는 함수 생성기 또는 AFG가 정확한 주파수에서 출력할 수 있도록 하는 구성요소의 집합입니다. 정확한 주파수에서 신호를 생성하기 위해 위상 어큐뮬레이터는 세 가지 일반적인 구성요소를 사용합니다. 첫 번째 구성요소는 위상 어큐뮬레이터로, 튜닝 워드를 사용하여 신호의 주파수를 지정합니다. 튜닝 워드는 웨이브폼 메모리에 점프할 샘플 수를 지정하는 24~48비트의 디지털 워드입니다. 두 번째 구성요소는 가산기로, 튜닝 워드를 가져와 위상 레지스터의 나머지에 합산합니다. 이 새로운 디지털 값은 위상 레지스터로 출력됩니다. 위상 어큐뮬레이터의 마지막 구성요소는 위상 레지스터로, 새로운 디지털 워드를 가져와 이를 룩업 테이블에서 출력할 다음 샘플 포인트의 메모리 주소를 지정하는 데 사용합니다. 위상 레지스터는 룩업 테이블 메모리 주소에서 사용되지 않은 남아 있는 최상위 비트를 다시 가산기로 반환하여 시간이 지나서도 주파수를 정확하게 유지합니다.

c. 룩업 테이블

위상 레지스터의 출력은 시간이 지나면서 메모리 주소가 늘어나면 디지털 램프처럼 보이게 되는 데 이 때문에 튜닝 워드가 지정한 속도로 변합니다. 따라서 원하는 웨이브폼을 출력하기 위해 위상 레지스터의 출력은 룩업 테이블에서 필요한 웨이브폼 샘플 주소를 가리킵니다. 그러면 룩업 테이블은 받은 메모리 주소에 디지털 워드를 전달합니다. 이는 DAC가 생성할 수 있는 정확한 진폭과 위상을 나타내는 디지털 워드입니다.

주파수 민첩성 또는 웨이브폼의 주파수를 매우 빠르게 변경하고 위상을 연속적으로 변경하는 능력은 DDS 아키텍처의 주요 이점 중 하나입니다. DDS를 사용하는 AFG는 웨이브폼의 주파수를 매우 빠르게 변화시킬 수 있는데, 웨이브폼의 주파수를 변경하려면 튜닝 워드만 바꾸면 되기 때문입니다.

일반적인 어플리케이션

위에서 이야기한 바와 같이 DDS 기술의 주요 이점은 두 가지입니다. DDS 기술의 주요 이점 중 하나는 생성된 신호의 주파수가 정확하다는 점입니다. 이런 이점 덕분에 함수 생성기 또는 AFG에서 생성된 신호의 주파수 정확도를 믿을 수 있어 구성요소를 매우 정확하게 테스트할 수 있습니다.

DDS 기술의 두 번째 주요 이점은 생성된 신호의 주파수를 매우 빠르게 바꾸고 위상을 연속적으로 바꿀 수 있는 기능입니다. 이를 통해 주파수를 신속하게 변경할 수 있고 DUT(Device Under Test)에 전달되는 신호의 한계를 뛰어넘어 테스트 디바이스에 부담을 줄 수 있기 때문에 특정 범위에서 구성요소를 더 효율적으로 테스트할 수 있습니다.

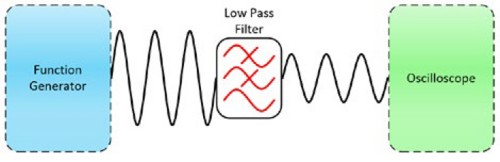

DDS 기술이 적용된 AFG가 매우 유용하다는 것을 확인할 수 있는 예는 정확한 필터 특성화입니다. 필터로 전달된 신호가 AFG에서 정확하게 생성되고 필터링된 신호가 오실로스코프에서 정확히 측정되는 경우에만 필터를 정확하게 특성화할 수 있습니다. 그림 3은 필터 특성화를 위한 일반적인 테스트 설정을 나타냅니다.

그림 3: DDS 지원 함수 생성기, 저역 통과 필터, 오실로스코프가 포함된 필터 특성화 어플리케이션 블록다이어그램

요약

- DDS 기술이 적용되지 않은 신호 생성기는 샘플 클럭의 주파수에서 저장된 웨이브폼을 포인트별로 출력하여 웨이브폼을 생성합니다.

- DDS 기술이 적용된 신호 생성기는 다양한 주파수에서 매우 정확한 주파수로 주기적인 웨이브폼을 생성할 수 있습니다. 이는 고유한 메모리 액세스와 클럭 메커니즘 때문입니다.

- DDS 기술은 3개의 상위 레벨 하드웨어 블록인 샘플 클럭, 위상 어큐뮬레이터, 룩업 테이블로 구현됩니다.

- 샘플 클럭은 주파수 튜닝 워드를 생성하고 위상 어큐뮬레이터 값을 업데이트하며 DAC 출력 속도를 구동합니다.

- 위상 어큐뮬레이터는 주파수 튜닝 워드를 입력으로 사용하고 룩업 테이블에서 출력될 다음 샘플의 디지털 메모리 주소를 전달합니다.

- 룩업 테이블은 주기적인 웨이브폼을 디지털 샘플로 저장합니다. 룩업 테이블은 위상 어큐뮬레이터의 메모리 주소를 가져와 그 메모리 주소의 디지털 웨이브폼 샘플을 DAC에 전달합니다.

- DDS 기술이 적용된 신호 생성기는 정확하게 주파수를 생성해야 하거나 주파수 민첩성이 필요한 응용 분야에 사용해야 합니다.

- 매우 크고 복잡한 사용자 정의 웨이브폼이 필요한 응용 분야에서는 DDS 기술이 적용된 임의 함수 생성기 대신 임의 웨이브폼 생성기를 사용하는 것이 가장 좋습니다.