LabVIEW FPGAコードをテストおよびデバッグする

概要

LabVIEW FPGAモジュールには、複数のシミュレーションオプションがあります。設計検証プロセスで各オプションをいつどのように使用するかを理解することは重要です。このドキュメントは、設計のテスト用に異なるLabVIEW FPGAシミュレーションオプションを使用する際の判断に役立ちます。

内容

- モジュール式テストレベル

- FPGAの実行モードを理解する

- FPGA実行モードの選択

- Windowsコンテキストでの実行

- FPGAシミュレーションモードでの実行

- サードパーティシミュレータでの実行

- FPGAターゲットでの実行

モジュール式テストレベル

コードをモジュール式のセクションに分割することで、大規模で複雑なアプリケーションの検証を簡素化できます。より小型でシンプルなモジュールを最初にテストすることで、システム全体のテストでは診断がより困難な機能上の問題を特定できます。テストは、ユニット、コンポーネント、システムの3つのレベルに分けられます。

ユニット

ユニットとは、特定の機能を提供し、それ以上分解してテストできない、IPの最も基本的なレベルです。通常、ユニットはさまざまな言語プリミティブで構成される特定のアルゴリズムまたは処理関数です。

コードのセクションは、以下の要件を満たす場合にユニットとみなされます。

- コードがサブVIとしてカプセル化でき、設計の他の部分で再利用できる場合がある。

- コードに、I/O、データ通信、またはターゲット固有のリソースは含まれていない。

- コードに、並列で実行されているか、異なるレートで実行されている複数のループが含まれていない。

- 予測される出力をテストするための既知の入力のセットを提供することで、コードの機能を検証できる。

- コードの状態が時間の明示的な経過または制御に依存していない。

コンポーネント

コンポーネントはもっと複雑な論理の集合体で、システム全体のタイミングや状態に影響を与える要素が含まれています。通常、FPGAアプリケーションは複数のコンポーネントに分割が可能で、大きなコンポーネントに統合する前に機能を個別に検証できます。

コードのセクションは、以下の要件を満たす場合にコンポーネントとみなされます。

- コードに、達成すべき明確なタスクまたは目標がある。

- コードが単一のプロセスで、スタンドアロンで実行されるか、相互に依存するプロセスの集合である。

システム

システムとは、トップレベルのFPGA VIとコンポーネントレベルIP (CLIP) を介して設計にインポートされた追加のIPによって表される最上位のコンポーネントです。トップレベルのFPGAシステムのインタフェースのみがホストアプリケーションに表示されます。そのため、検証テストには通常、ホストインタフェースAPIと実際のI/O信号が必要です。通常、システムには複数のコンポーネントが含まれており、それらを組み合わせてタスクを実行します。

FPGAの実行モードを理解する

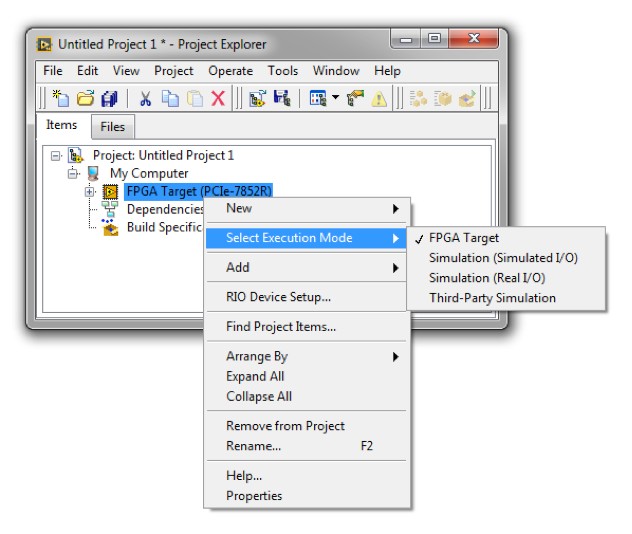

LabVIEW FPGAモジュールには、いくつかの実行モードがあります。各実行モードは、FPGA VIのテストおよびデバッグに対して異なる機能を提供します。LabVIEWプロジェクトでFPGAターゲットを右クリックし、ショートカットメニューから実行モードを選択を選択すると、実行モードを変更できます。

注記: FPGAデスクトップ実行ノードは、リアルタイム環境では使用できません。

図1. LabVIEW FPGAプロジェクトで実行モードを選択

FPGAターゲット

FPGAハードウェアでの実行は、通常LabVIEW FPGA設計をテストする最終段階に使用されます。この実行モードはデプロイメント時のシステム動作を最もよく表しますが、デバッグオプションは制限されています。

シミュレーション (シミュレーションI/O)

LabVIEW FPGAのユーザは、大半のテストをこのモードで実行します。シミュレーションモードでは高度なシミュレーションエンジンを利用してデスクトップでVIを実行しますが、そのタイミング特性はFPGAハードウェアと類似しています。シミュレーションI/Oを使用するシミュレーションモードでは、I/Oのシミュレート値を使用してコードを検証するためのいくつかの高度なメカニズムが提供されます。任意の値または定義された値をシミュレートできます。

シミュレーション (実際のI/O)

このモードでは、FPGAターゲットから収集した実データをホストコンピュータに渡し、シミュレーション環境で使用します。シミュレーションでFPGA出力値を変更すると、FPGAハードウェア出力に物理的変化が生じます。この実行モードはRシリーズターゲットのみに予約が可能です。

サードパーティシミュレーション

この実行モードでは、高度なサードパーティソフトウェアとVHDLテストベンチを使用して、FPGAコードのフルサイクルアキュレートシミュレーションを行います。サードパーティシミュレーションモードでは、CLIPまたはIP統合ノードを介して統合されたHDL IPの検証も可能です。

FPGA実行モードの選択

モジュール式のテストレベルとFPGA実行モードの基本を理解すると、LabVIEW FPGA設計の各部分のテストにどの実行モードが適切かを決定できます。以下の表は、各実行モードの理想的な使用方法をまとめたものです。

| 実行モード | Windows PC1 | FPGAシミュレーションモード | サードパーティシミュレーション | FPGAターゲット |

|---|---|---|---|---|

| 機能的パフォーマンスを検証する | ✓ | ✓ | ✓ | ✓ |

| タイミングを検証する | ✓2 | ✓ | ✓ | |

| サードパーティHDL IPを検証する | ✓3 | ✓ | ✓ | |

| ユニットテストに適している | ✓ | |||

| コンポーネントテストに適している | ✓ | ✓ | ✓ | |

| システムテストに適している | ✓ |

1実行モードを選択ショートカットメニューにWindows PCがありません。詳細については、Windowsコンテキストでの実行のセクションを参照してください。

2FPGAシミュレーションモードはシミュレーションFPGA時間の概念を使用します。詳細については、FPGAシミュレーションモードでの実行のセクションを参照してください。

3IP統合ノードを介して統合されたIPのシミュレーションのみが、FPGAシミュレーションモードでサポートされています。CLIPのシミュレーションには、サードパーティシミュレーションの使用をお勧めします。

Windowsコンテキストでの実行

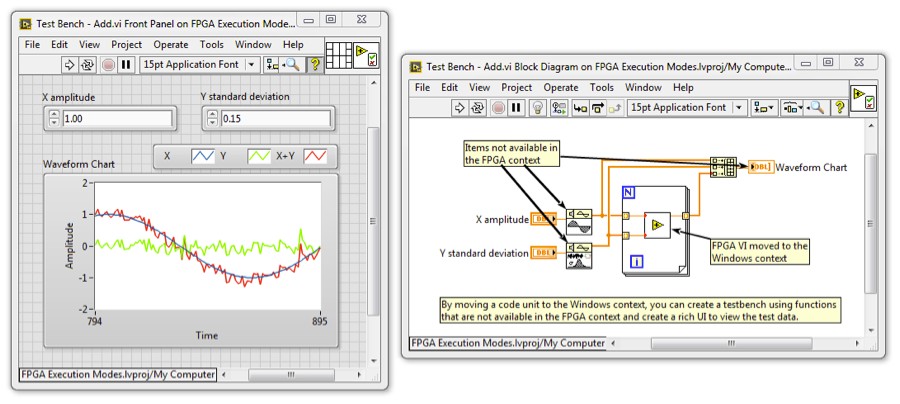

WindowsコンテキストでのVIの実行は、主にユニットテストとロジックの検証に使用されます。ユニットにはFPGA固有のI/Oやリソースが含まれないため、VIをWindowsコンテキストで実行できます。WindowsコンテキストでFPGA VIを実行するには、FPGAターゲットからVIをLabVIEWプロジェクトのマイコンピュータにドラッグします。

VIを移動したら、テストベンチVIを作成してユニットの機能を実行できます。WindowsコンテキストでVIを実行するため、テストベンチにはFPGAコンテキストに存在しない関数を含めることができ、テスト結果を視覚化するためのUIを作成できます。

図2. Windows環境でLabVIEWを使用したユニットテストの実行

WindowsコンテキストでFPGA VIを実行する場合、VIの機能を検証することのみが可能です。Windowsコンテキストでは、VIのFPGAタイミング特性は一切保持されません。タイミングを検証するには、ユニットをコンポーネントに統合し、他の実行モードの1つでそのユニットをテストする必要があります。

FPGAシミュレーションモードでの実行

FPGAシミュレーションモードでは、FPGAのI/Oとリソースをシミュレートでき、実行タイミングをより正しく理解できます。これらの要因により、FPGAシミュレーションモードはコードコンポーネントのテストに最適です。

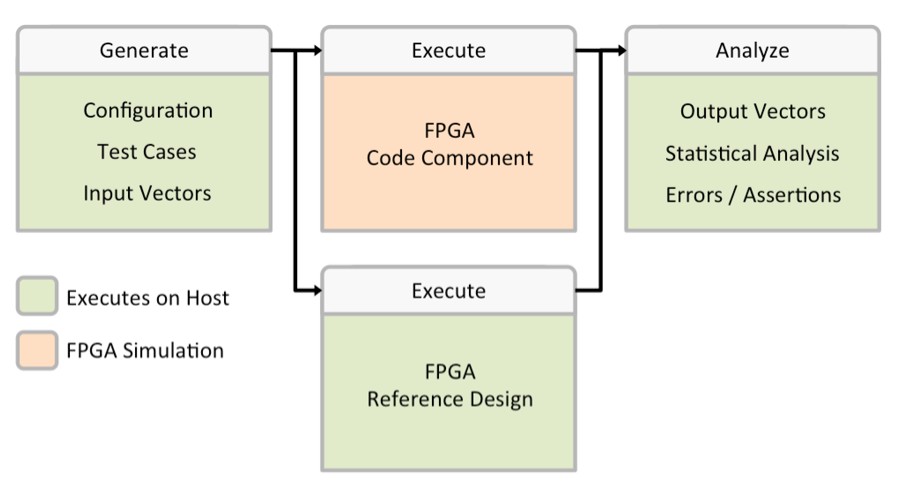

NIでは、シミュレーションモードで実行するFPGA VIと通信するホスト (マイコンピュータやRTターゲットなど) で実行するテストベンチVIを作成することを推奨します。ホスト上でテストベンチVIを実行すると、テスト入力を作成し、テスト結果を解析するための何百もの機能にアクセスできます。これらの関数を使用して、コンポーネントのリファレンス実装を作成またはインポートすることもできます。以下の図は、LabVIEWでグラフィカルに実装できるテストベンチのハイレベル図を示しています。

図3. テストベンチ環境を使用するLabVIEW FPGAシミュレーションモード

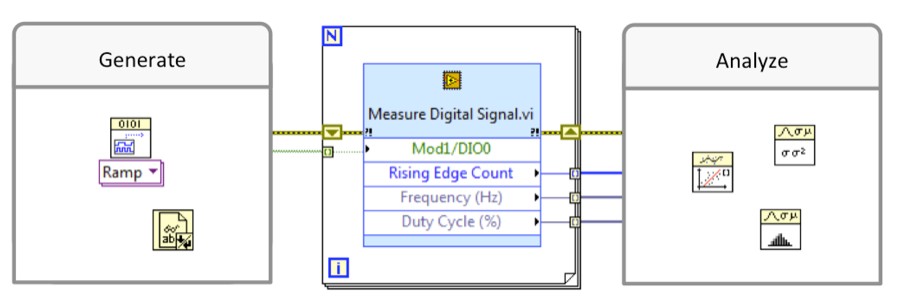

LabVIEW 2013では、ホストテストベンチの作成を簡素化し、FPGAコードのシミュレーションタイミングを改善するため、FPGAデスクトップ実行ノード (DEN) が導入されました。DENは、ハードウェアタイミングの反映にシミュレーション時間を使用します。DENを使用すると、カスタマイズされた刺激を制御器と入力に提供し、FPGAを強制的に指定数分進め、表示器と出力の値を読み取ることができます。さまざまなテストベクトルとケースを使用してこの手順を簡単に反復してコンポーネントを検証できます。

図4. デスクトップ実行ノードを使用して、改善されたタイミング機能などのテストベンチ環境を簡素化する

FPGAデスクトップ実行ノードの詳細については、LabVIEW FPGAデスクトップ実行ノードの使用チュートリアルを参照してください。

サードパーティシミュレータでの実行

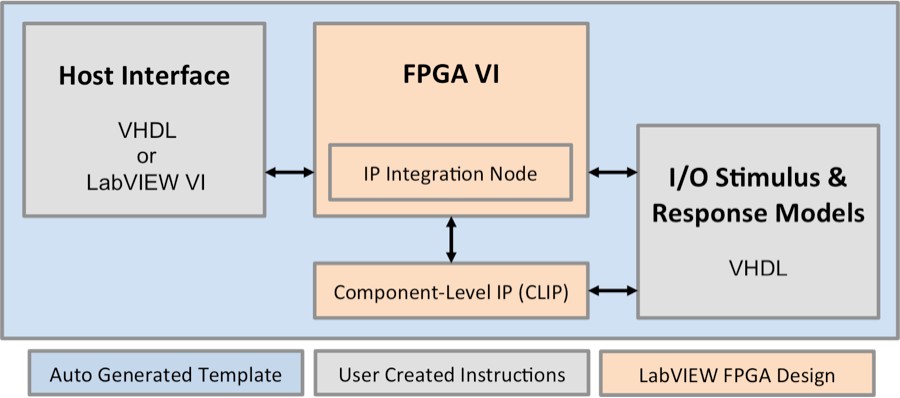

LabVIEW FPGAをサードパーティのシミュレーションソフトウェアとインタフェースして使用することで、高度なシミュレーション要件を満たすことができます。サードパーティシミュレーションにより、詳細なタイミング解析が可能なFPGA設計の真のサイクルアキュレートシミュレーションが可能です。サードパーティシミュレーションはまた、CLIPまたはIP統合ノードを介して統合されたIPを含む設計の非常に有益なシミュレーションを提供します。以下の図は、サードパーティFPGAシミュレーションのハイレベル図を示しています。

図5. CLIPまたはIP統合ノードを使用したサードパーティコードの統合

Xilinx ISim (ISE) およびXilinx XSim (Vivado) は、LabVIEW FPGA Compilation Toolに含まれています。Xilinx ISimおよびXilinx XSimで効果的なテストベンチを作成するには、VHDLの知識が必要です。Xilinx ISimの使用に関する詳細は、Xilinx ISimを使用したサイクルアキュレートシミュレーションドキュメントを参照してください。

LabVIEWを使用してサードパーティシミュレーション用のホストインタフェーステストベンチを作成することで、生産性が向上し、VHDLの専門知識が不要になります。ホストインタフェースを作成するには、Mentor Graphics Questaシミュレータをサードパーティのシミュレーションソフトウェアとして使用する必要があります。LabVIEW FPGAモジュールでサポートされているMentor Graphicsシミュレータのバージョンの情報については、ni.com/infoサイトでInfo Codeに「ex9b2p」と入力してください。Mentor Graphics Questaシミュレータの使用の詳細については、Mentor Graphics Questaシミュレータを使用したサイクルアキュレート協調シミュレーションドキュメントを参照してください。

注記: LabVIEW 2018 FPGAモジュールのリリースからMentor Graphics Questaシミュレータのサポートが削除されました。

FPGAターゲットでの実行

どのシステムでも、完全な検証を行うにはシミュレーション環境だけでなくハードウェアでもテストする必要があります。物理ハードウェアで実行すると、実際のI/O、ジッタなどがシステムの機能やタイミングに影響を与えるため、デプロイされた環境での設計の動作を最も正確に表現できます。

従来のLabVIEWデバッグツールは物理的なFPGAターゲット上で使用できないため、機能とタイミングの検証に役立つメカニズムを設計にコンパイルする必要があります。FPGAの物理的な実行を検証するには、以下の方法があります。

- 表示器とFIFOを使用して、主要領域からホストにデータを渡します。

- 制御器、ループ、シーケンスストラクチャを使用して、FPGAの実行を「一時停止」するトリガを作成します。

- シーケンスストラクチャとティックカウンタを使用して、コードのクリティカルセクションでタイミングをベンチマークします。

- Xilinx ChipScopeを使用して、内部のFPGA信号をプローブ、トリガ、表示します。