Introduction aux instruments série haute vitesse PXI

Aperçu

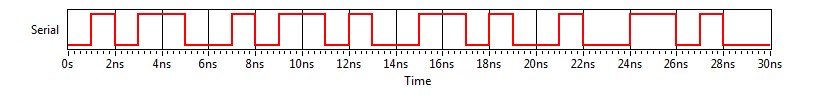

Instruments série haute vitesse PXI aident les ingénieurs à valider, interfacer et tester les protocoles série haute vitesse. Certains matériels série haute vitesse, tels que les PXIe-7903 et PXIe-7902, ont été conçus pour les ingénieurs qui ont besoin des capacités de co-traitement hautes performances du FPGA pour transférer des données en grand volume et intégrer le traitement du signal en temps réel. Ce matériel intègre un FPGA Xilinx Kintex™ UltraScale+™ ou un FPGA de la Série 7, que vous pouvez programmer avec le LabVIEW FPGA Module pour une personnalisation et une réutilisation maximales en fonction de chaque application spécifique. Ces instruments tirent parti des émetteurs-récepteurs multigigabits (MGT) FPGA pour prendre en charge des vitesses de ligne allant jusqu'à 28,2 Gbit/s et jusqu'à 48 lignes TX et RX. Faisant partie de la plate-forme PXI, ils bénéficient des capacités de cadencement, de déclenchement et de déplacement de données à haute vitesse PXI, notamment pour le transfert en continu vers et depuis le disque, ainsi que pour le transfert en continu pair-à-pair (P2P) à des vitesses pouvant atteindre 7 Go/s .

Contenu

- L’émergence des interfaces série haute vitesse

- Modules série haute vitesse

- Exemples d’applications

- Compétences requises

- Étapes suivantes

L’émergence des interfaces série haute vitesse

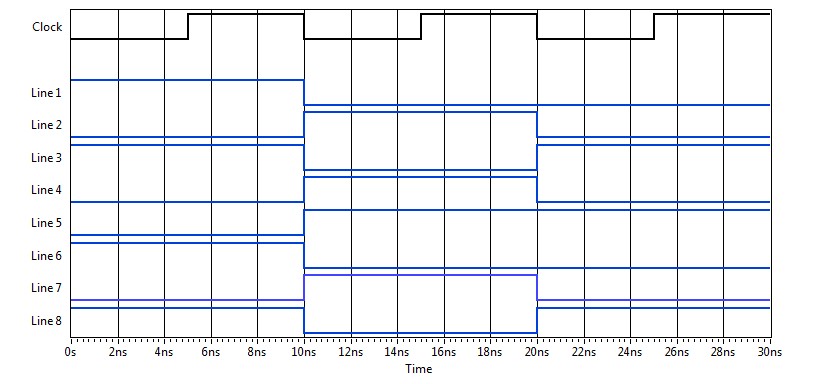

Face à la demande en bande passante de données toujours plus élevée, il a été nécessaire d’augmenter les fréquences d’horloge et le parallélisme des interfaces câblées. Cependant, avec les bus de données parallèles traditionnels, le moindre décalage entre l'horloge et les lignes de données peut avoir une incidence sur le taux d'erreur binaire de l'interface. Les liaisons de données série offrent une solution à ce problème en intégrant l'horloge dans le flux de données d'une paire donnée de traces différentielles, ce qui élimine la possibilité de décalage entre l'horloge et les données. Cette fonctionnalité nécessite du matériel électronique supplémentaire à l'extrémité réceptrice de l'interface ainsi qu'un encodage supplémentaire pour la récupération d'horloge ; cependant, il permet des débits de données considérablement plus élevés, ce qui répond à la demande de bande passante.

Figure 1. Horloge parallèle (noir) et données (bleu) comparées à une horloge embarquée dans les données (rouge), à bande passante de données équivalente.

Les protocoles de communication de données modernes sont passés de ces interfaces parallèles à des interfaces série haute vitesse, telles que les normes vidéo PCI Express, HDMI et DisplayPort, IEEE 1394b, USB 3.0, etc. Pour les ingénieurs de conception et de test, la validation de ces interfaces présente de nouveaux défis qui nécessitent un nouveau matériel de test. Traditionnellement, les ingénieurs utilisent des oscilloscopes coûteux ou des testeurs de taux d’erreur binaire (BERT) pour caractériser les interfaces physiques et utilisent des analyseurs et des générateurs spécifiques au protocole pour valider que la pile de protocoles est implémentée correctement, et que la transmission et la réception de données fonctionnent efficacement. Cependant, pour les tests V&V automatisés et en fabrication, il n’existe pas de matériel optimisé pour tester ces interfaces série. Les oscilloscopes et les testeurs de taux d'erreur sur les bits sont souvent trop coûteux et lents pour justifier la couverture qu'ils fournissent, tandis que le matériel spécifique à un protocole n'est souvent pas assez flexible pour s'intégrer dans les systèmes de test automatique. Le matériel à protocole spécifique, en revanche, ne peut pas être réutilisé pour d’autres tests ni pour d’autres appareils sous test (DUT).

Les FPGA fournissent une solution à ces défis. Les FPGA modernes et hautes performances comprennent généralement plusieurs MGT qui fonctionnent avec une variété d'interfaces série haute vitesse. Lorsqu'il est associé à l'IP spécifique au protocole approprié, à la programmation graphique via le LabVIEW FPGA Module et aux avantages de l'écosystème PXI, un nouvel instrument série haute vitesse est conçu par logiciel.

Modules série haute vitesse

|  |  |  |  |  | |

| Spécifications | PXIe-6591 | PXIe-6592 | PXIe-6593 | PXIe-6594 | PXIe-7902 | PXIe-79032 |

| Fréquence de ligne | 500 Mbit/s–12,5 Gbit/s¹ | 500 Mbit/s–10,3125 Gbit/s¹ | 500 Mbit/s–16,3 Gbit/s | 500 Mbit/s–28,2 Gbit/s | 500 Mbit/s–12,5 Gbit/s | 500 Mbit/s–28,2 Gbit/s |

| Voies | 8 TX/RX | 4 TX/RX | 8 TX/RX | 8 TX/RX | 24 TX/RX | 48 TX/RX |

| FPGA | Kintex 7 K410T | Kintex 7 K410T | Kintex UltraScale KU040, KU060 | Kintex UltraScale+ KU15P | Virtex™ 7 485T | Virtex UltraScale+ XCVU11P |

| DRAM | 2 Go | 2 Go | 4 Go | 8 Go | 2 Go | 20 Go |

| Hôte Transfert en continu BW | 3,2 Go/s | 3,2 Go/s | 7 Go/s | 7 Go/s | 3,2 Go/s | 7 Go/s |

| Connecteur | Mini-SAS HD | SFP+ | QSFP28 | QSFP28 | Mini-SAS HD | Mini-SAS HD |

| Options de câblage | Cuivre ou Optique | Cuivre ou Optique | Cuivre ou Optique | Cuivre ou Optique | Cuivre ou Optique | Cuivre ou Optique |

| DIO auxiliaire | 20 SE | 4 SE | 8 GPIO | 8 GPIO | N/A | 8 GPIO |

Tableau 1. Instruments série haute vitesse PXI.

¹Écart dans les débits de ligne réalisables entre 8 Gbit/s et 9,8 Gbit/s.

²Le PXIe-7903 est un module à 2 emplacements.

La connectivité et le câblage sont essentiels pour les applications qui présentent des débits de données élevés et des bandes passantes analogiques supérieures à 20 GHz. Les modules PXIe-7903, PXIe-7902, PXIe-6594, PXIe-6593, PXIe-6592 et PXIe-6591 proposent chacun des options distinctes pour simplifier la connectivité dans des cas d'utilisation spécifiques. Les trois modules intègrent un FPGA Xilinx programmable par l'utilisateur.

Les émetteurs-récepteurs GTX de la Série 7 de Xilinx représentent la technologie clé de ces instruments. Ils utilisent la logique en mode courant (CML), qui est une interface différentielle qui offre une petite oscillation de signal de 800 mVpp (nominalement, 1000 mVpp au maximum) pour une consommation électrique et des émissions rayonnées réduites, et un différentiel de 100 ohms (50 ohms par branche du signal ) pour minimiser les réflexions et les aberrations de signal qui en résultent aux fréquences de données élevées. De plus, pour une fidélité optimale du signal, ces émetteurs-récepteurs incluent une amplitude de transmission programmable pour compenser les longs câbles ainsi que la pré-emphase et la post-accentuation, ainsi qu'une égalisation auto-adaptative du récepteur pour surmonter la bande passante limitée des voies analogiques et des câbles.

Toutes les interfaces série haute vitesse requièrent une horloge de référence qui opère à un diviseur entier de la fréquence de ligne. Pour une flexibilité maximale, les émetteurs-récepteurs GTX incluent une boucle à verrouillage de phase (PLL) capable de multiplier l'horloge de référence jusqu'à 100 fois pour produire le débit de données série. Ils incluent également des convertisseurs série-parallèle et parallèle-série avec des rapports allant jusqu'à 80X, limitant les fréquences d'horloge FPGA tout en permettant des vitesses de données série élevées. De plus, les émetteurs-récepteurs intègrent des structures d'encodage et de décodage 8b-10b, 64b/66b et 64b/67b pour garantir un nombre suffisant de transitions du signal pour la récupération de l'horloge et pour éviter de consommer des ressources FPGA à usage général. LeGuide de l'utilisateur des émetteurs-récepteurs FPGA de la Série 7 Xilinx GTX/GTH fournit plus de détails sur les émetteurs-récepteurs Xilinx GTX.

En plus de fournir des émetteurs-récepteurs série haute vitesse, les FPGA Xilinx sur les instruments remplissent d'autres fonctions essentielles. Ils implémentent la logique du protocole utilisé, ainsi que toute logique utilisateur spécifique à l’application pour la configuration du matériel et la génération, la réception et le déplacement des données dans l’ensemble du système.

Figure 2. Architecture matérielle PXIe-7903 avec interfaces clés et débit de données.

| Spécifications | FPGA | LUT | Tranches DSP | Bloc RAM embarqué |

| PXIe-6591 | Kintex-7 K410T | 254 200 | 1 540 | 28 Mo |

| PXIe-6592 | Kintex-7 K410T | 254 200 | 1 540 | 28 Mo |

| PXIe-6593 | Kintex UltraScale KU040 | 242,400 | 1 920 | 21,1 Mo |

| Kintex UltraScale KU060 | 331,680 | 2,760 | 38 Mo | |

| PXIe-6594 | Kintex UltraScale+ KU15P | 523,000 | 1,968 | 34,6 Mo |

| PXIe-7902 | Virtex-7 485T | 303,600 | 2,800 | 37 Mo |

| PXIe-7903 | Virtex UltraScale+ XCVU11P | 2,835,000 | 9,216 | 341 Mo |

Tableau 2. Instruments série haute vitesse PXI et leurs spécifications FPGA respectives.

Directement aux circuits FPGA, on trouve une mémoire DRAM DDR3 embarquée pouvant atteindre 20 Go, qui permet de lire ou d'écrire des données à des vitesses allant jusqu'à 25 Go/s (maximum théorique) avec des modèles d'accès définis par l'utilisateur. Le FPGA inclut aussi une interface PCI Express x8 Gen 3 dans le fond de panier PXI Express pour le transfert en continu de données depuis et vers l'hôte et le disque, ou le P2P vers d'autres matériels FPGA du système à des vitesses unidirectionnelles allant jusqu'à 7 Go/s et bidirectionnelles à 2,4 Go/s dans chaque direction (4,8 Go/s au total).

Une horloge de référence haute fidélité à faible fluctuation est un composant essentiel de tout système de communication série haute vitesse. Tous les modules intègrent un synthétiseur toutes vitesses pour les opérations MGT sur toute la gamme des émetteurs-récepteurs Xilinx GTX, avec les PXIe-6591, PXIe-6592 et PXIe-7902 fonctionnant de 500 Mbit/s à 8 Gbit/s et 9,8 Gbit/s à leur maximum. Il n’existe pas de fréquences de ligne minimale et maximale pour le PXIe-6593, le PXIe-6594 et le PXIe-7903. Les modèles PXIe-6591, PXIe-6592, PXIe-6593 et PXIe-6594 sont dotés d'une connectivité coaxiale en face avant pour exporter l'horloge de référence intégrée. La connectivité permet également d'importer une horloge de référence externe. Enfin, les périphériques peuvent acheminer les horloges de fond de panier PXI Express 100 MHz ou DStarA comme référence pour les MGT.

Logiciels

Un instrument conçu par logiciel fournit les mêmes fonctionnalités qu'un instrument à fonction fixe, mais les utilisateurs ont la possibilité de personnaliser le matériel d'instrumentation par le biais d'un FPGA ouvert et programmable par l'utilisateur. Ce niveau de personnalisation est nécessaire dans un instrument série haute vitesse PXI pour prendre en charge une grande variété de protocoles et d'applications. Par conséquent, il n'existe pas d'API de haut niveau pour programmer ces matériels. Au lieu de cela, elles sont programmées directement dans le logiciel LabVIEW pour le code hôte (processeur) et FPGA, s'interfaçant entre les deux avec l'API NI-RIO de bas niveau. Pour aider les utilisateurs à être rapidement opérationnels, une multitude d'exemples illustrent l'utilisation de différents protocoles, ainsi que différents modèles d'utilisation pour ces instruments.

Le FPGA ouvert fournit un degré de personnalisation que l'on ne trouve pas dans d'autres instruments. Il implémente avant tout le protocole série pour lequel l'instrument est configuré. À lui seul, cela permet aux PXIe-7903, PXIe-7902, PXIe-6594, PXIe-6593, PXIe-6592 et PXIe-6591 de prendre en charge une multitude de protocoles série standard et même personnalisés. Au-delà du protocole, les fonctionnalités matérielles définies par l'utilisateur permettent des types de tests qui n'étaient pas possibles auparavant. Par exemple, la génération de données algorithmique sur le FPGA réduit la mémoire de stockage de waveforms et la bande passante système nécessaires pour télécharger ces waveforms, ce qui accélère le débit des tests. Les analyses de données algorithmiques telles que la comparaison des réponses, le déclenchement intelligent et la réduction et compression des données réduisent considérablement la quantité de données à traiter par le processeur hôte, ce qui réduit également le temps de test.

L'accès à la DRAM défini par l'utilisateur permet une flexibilité dans la façon dont la DRAM est partitionnée en régions de stimulus et de réponse. Il active également des algorithmes de compression et de décompression personnalisés, ce qui permet une utilisation optimale de la taille et de la bande passante de la DRAM. La capture et la lecture de signaux standard sont certainement possibles, mais en fonction du protocole, de la fréquence de la ligne et du nombre de lignes, la bande passante des E/S peut dépasser la bande passante de la DRAM. Enfin, le mouvement des données défini par l'utilisateur vers et depuis un instrument série haute vitesse et l'hôte ou d'autres instruments offre une flexibilité importante pour l'intégration au niveau du système. Par exemple, il est possible de convertir des données analogiques en échantillons numériques avec un numériseur haute vitesse, d'utiliser le transfert en continu en P2P de NI pour transférer ces données vers un instrument série haute vitesse à des vitesses allant jusqu'à 7 Go/s, puis de transmettre ces échantillons numériques à un périphérique externe via un protocole série. Un instrument série haute vitesse peut également capturer un flux de données série et le transférer vers le processeur hôte et, en fin de compte, une matrice RAID à large bande passante pour des heures, voire des jours, de stockage continu, toujours à des vitesses pouvant atteindre 7 Go/s.

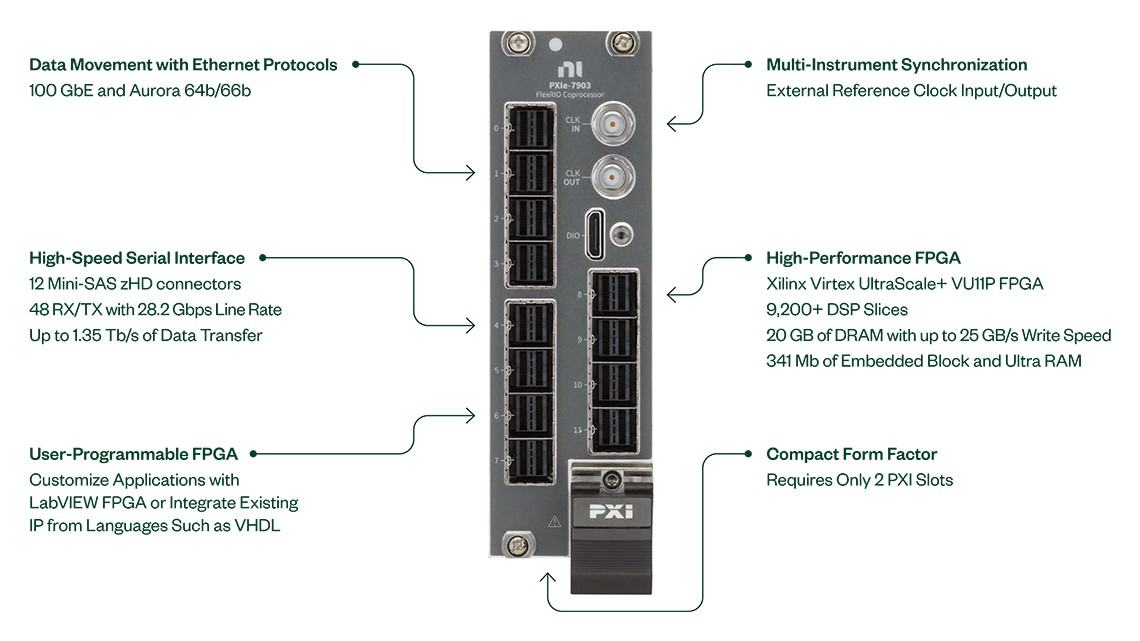

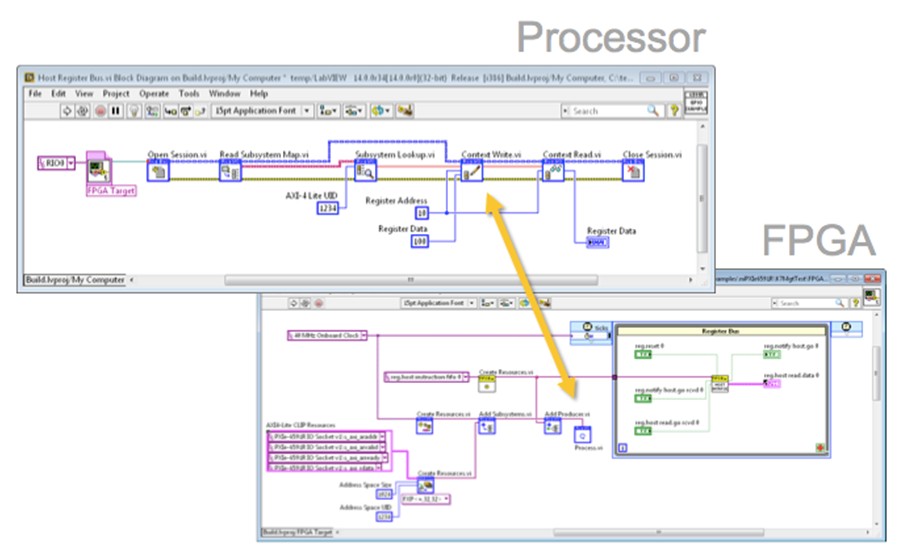

LabVIEW FPGA simplifie la configuration et la programmation de ces instruments série haute vitesse. La Figure 3 présente les principales interfaces accessibles via LabVIEW, ainsi qu'un code représentatif. Le LabVIEW FPGA et l'API NI-RIO fournissent des mécanismes efficaces pour le transfert de données basé PCI Express entre le processeur hôte et le FPGA, y compris la lecture et l'écriture de registres ainsi que les transferts DMA bidirectionnels. L'accès à la DRAM, généralement une interface difficile à gérer dans les langages de description du matériel (HDL) de bas niveau, est simplifié par des interfaces de requête, de lecture et d'écriture abstraites, tout en maintenant un débit élevé et en fournissant un arbitrage de lecture et d'écriture élémentaire. La configuration de l'émetteur-récepteur GTX est généralement spécifique au protocole, et l'IP existe déjà pour de nombreuses interfaces série haute vitesse (HDL ou netlist) dotées d'une configuration de l'émetteur-récepteur intégrée. Cette interface de protocole série est exposée dans LabVIEW FPGA via une interface CLIP (component-level IP) à socket. Les nœuds CLIP permettent l'opération asynchrone de code non implémenté dans LabVIEW, mais ont une interface bien définie avec le diagramme LabVIEW FPGA. Un scénario courant utilise une IP spécifique au protocole Xilinx (y compris la configuration d’émetteur-récepteur) du catalogue d’IP Xilinx Vivado et une fine couche de VHDL pour définir l’interface avec LabVIEW FPGA. Une fois le protocole implémenté, LabVIEW FPGA offre un langage riche pour implémenter la logique utilisateur arbitraire comme la prise de décision, l'implémentation de machine à états, le contrôle de DUT, le traitement de signaux et le transfert de données.

Figure 3. LabVIEW FPGA fournit un accès graphique aux aspects clés du FPGA programmable par l'utilisateur sur des instruments série haute vitesse PXI.

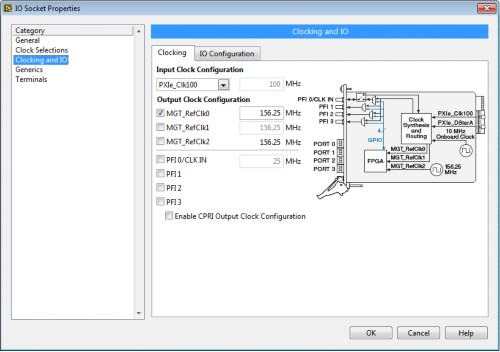

Au-delà de la définition de la logique à implémenter sur le FPGA programmable par l'utilisateur, LabVIEW simplifie la configuration du matériel via sa hiérarchie de projet et les pages de configuration associées. Par exemple, la configuration de l'horloge de référence sur ces instruments série haute vitesse nécessite un algorithme complexe pour déterminer des centaines de paramètres de registres à appliquer à au moins quatre circuits intégrés séparés, en plus de la logique requise pour appliquer ces registres quand le FPGA s’allume. LabVIEW FPGA affiche ceci comme une boîte de dialogue avec une représentation graphique des options, ainsi que des règles de conception et des conseils pour appliquer les configurations valides. Cette approche simplifie la configuration du synthétiseur d'horloge à n'importe quelle fréquence et le circuit de routage vers une tâche qui prend quelques minutes plutôt que plusieurs heures voire jours.

Figure 4. LabVIEW FPGA offre une interface graphique intuitive pour la configuration d'horloge qui simplifie un processus complexe.

Pour permettre la réutilisation du code et simplifier les tâches courantes, les instruments série haute vitesse PXI prennent en charge certaines bibliothèques de conception d'instruments, qui sont des bibliothèques de code hôte et FPGA avec des interfaces LabVIEW conçues pour fonctionner ensemble et fournir des capacités génériques. Le framework d'instructions est une bibliothèque de conception d'instruments pour la configuration dynamique du matériel pendant l'exécution. Bien que la plupart des fonctionnalités matérielles de ces instruments série (par exemple, la configuration de l'horloge) puissent être configurées de manière statique dans le projet LabVIEW , les utilisateurs peuvent tirer parti du framework d'instruction pour contrôler les paramètres du firmware spécifiques à l'application. Par exemple, le framework d’instructions simplifie la configuration de l’hôte des paramètres de registre exposés via les interfaces AXI-4 Lite sur le FPGA, couramment trouvés dans le protocole IP série Xilinx.

Figure 5. Processeur et code FPGA pour l'écriture et la lecture de registres via une interface AXI-4 Lite.

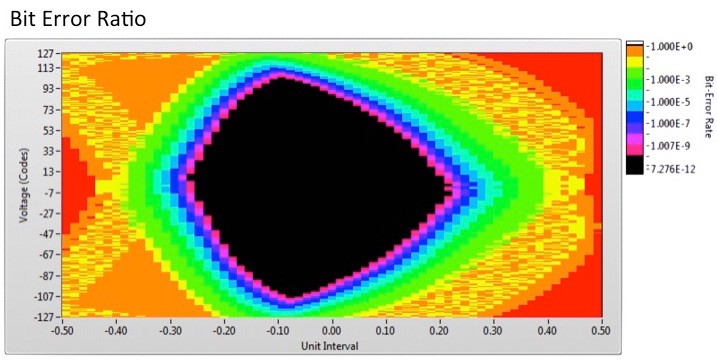

Construite à un niveau supérieur au framework d’instructions, la bibliothèque de conception d’instruments Eye Scan fournit des capacités de mise au point pour les voies de réception série haute vitesse. Les émetteurs-récepteurs Xilinx GTX disposent de deux comparateurs récepteurs par voie. Alors qu'un comparateur suit automatiquement le centre de l'œil série en fonction de la fréquence d'horloge et de la phase récupérées, l'autre comparateur peut effectuer indépendamment un décalage en amplitude et en phase. En faisant varier les paramètres de ce dernier comparateur et en comparant les résultats avec le premier, la bibliothèque de conception d'instruments Eye Scan peut créer un diagramme de l'œil statistique utile pour déterminer la marge de liaison de l'interface, avec une précision égale au plancher du taux d'erreur binaire des émetteurs-récepteurs GTX Xilinx. De plus, comme la bibliothèque de conception d'instruments Eye Scan utilise un ensemble indépendant de ressources matérielles, elle peut coexister avec d'autres IP de protocole et s'exécuter simultanément avec d'autres fonctionnalités spécifiques à l'application.

Figure 6. Les bibliothèques de conception d'instruments LabVIEW pour les instruments série haute vitesse PXI incluent une conception de référence pour effectuer un balayage de l'œil statistique en utilisant une configuration de rebouclage.

Au-delà de ces bibliothèques de conception d'instruments, d'autres instruments conçus par logiciel fournis par NI incluent des bibliothèques pour une grande variété de fonctions utiles comme le multi-enregistrement, ainsi que l'acquisition et la génération basées sur la DRAM. Bien qu'ils ne soient pas officiellement pris en charge ou testés sur les PXIe-7903, PXIe-7902, PXIe-6594, PXIe-6593, PXIe-6592 et PXIe-6591, en fonction de la compatibilité matérielle de la bibliothèque de conception d’instruments, il est parfois possible de les utiliser avec les instruments série haute vitesse PXI.

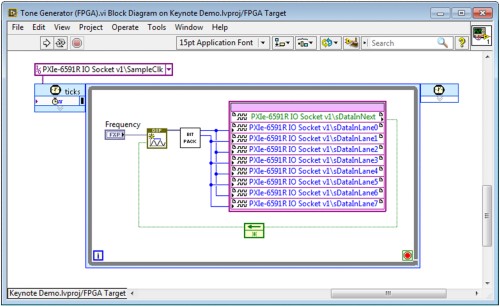

Figure 7. Les ingénieurs peuvent utiliser la bibliothèque de conception d'instruments DSP pour synthétiser une sinusoïde pour une transmission vers un convertisseur numérique-analogique via le protocole série JESD204B.

Protocoles

Les émetteurs-récepteurs GTX Xilinx intégrés aux instruments série haute vitesse PXI prennent en charge une grande variété de protocoles. NI fournit un certain nombre d'exemples logiciels pour démontrer comment intégrer des protocoles communs, ainsi que des architectures LabVIEW pour plusieurs modèles d'application. Chaque exemple est livré avec un fichier bitfile FPGA précompilé pour l'instrument pris en charge, ainsi que le code source et l'IP de protocole associés. Si ce code nécessite une modification pour l'application finale, certains protocoles nécessitent une licence IP de Xilinx pour recompiler le FPGA. Cette IP de protocole est disponible à l'achat auprès de Xilinx ou de revendeurs tels que Avnet ou DigiKey.

Xilinx Aurora

Xilinx Aurora fournit un protocole léger, à faible latence et à faible encombrement conçu pour les interfaces série point à point. Il prend en charge le plein débit des émetteurs-récepteurs série GTX Xilinx, ainsi que le lane bonding pour une bande passante encore plus grande. Principalement conçu pour le transfert de données à large bande passante, Aurora offre un contrôle de flux, un cadrage flexible et des options pour les voies simplex ou full-duplex. Pour en savoir plus sur Xilinx Aurora, cliquez sur les liens suivants :

http://www.xilinx.com/products/design_resources/conn_central/grouping/aurora.htm

Le driver Bibliothèques de conception d’instruments pour instruments série haute vitesse installe un exemple de conception de référence de projet pour Aurora 64b66b, et NI propose un exemple web pour Aurora 8b10b.

JESD204B et JESD204C

À mesure que les fréquences d'échantillonnage et les résolutions des convertisseurs analogique-numérique (C A/N) et numérique-analogique (C N/A) augmentent pour répondre aux exigences des transmissions numériques modulées à large bande sans fil, les débits de données vers et depuis ces convertisseurs ont augmenté. Avec les interfaces de données et d'horloge parallèle traditionnelles, ceci nécessite davantage de broches de circuit intégré avec des tolérances réduites. Les JESD204B et JESD204C relèvent ce défi en faisant passer ces interfaces vers des interfaces série haute vitesse, conçues pour fournir une bande passante de données élevée avec une faible latence et pour faciliter la synchronisation de plusieurs convertisseurs. JESD204B prend en charge jusqu'à 12,5 Gbit/s et 32 lignes pour les derniers C A/N et C N/A à large bande passante, haute vitesse et grand nombre de voies. Alors que JESD204C prend en charge des débits allant jusqu’à 32 Gbit/s. JESD204B utilise le codage 8B-10B, tandis que JESD204C prend en charge 8B-10B, 64B/66B et 64B/80B.

10 Gigabit Ethernet

Avec un débit de ligne de 10,3125 Gbit/s, le 10 Gigabit Ethernet (10 GbE) fournit une bande passante pratique d'environ 1 Go/s. La majorité des interfaces 10 Gigabit Ethernet sont soit optiques, soit SFP+ à attache directe (cuivre), avec des interfaces 8P8C/RJ45. L'exemple 10 Gigabit Ethernet pour le PXIe-6592 prend en charge les interfaces optiques 10GBASE-SR, 10GBASE-LR et 10GBASE-ER ainsi que SFP+ à attache directe, à l'aide du cœur IP PCS/PMA 10 Gigabit Ethernet de Xilinx et du contrôleur d'accès multimédia 10 Gigabit Ethernet OpenCores.org. Une pile UDP légère implémentée dans LabVIEW FPGA vient s'ajouter à cette solution MAC/PHY. De plus amples informations sur les cœurs IP 10 Gigabit Ethernet sont disponibles aux adresses suivantes :

https://www.xilinx.com/products/intellectual-property/10gbase-r.html

Le driver des bibliothèques de conception d'instruments pour les instruments série haute vitesse PXI installe un exemple de conception de référence de projet pour 1 GbE et 10 GbE.

100 Gigabit Ethernet

Le protocole 100 Gigabit Ethernet (100GbE) permet de transmettre des trames Ethernet à une vitesse de 100 gigabits par seconde (Gbit/s), ce qui est nettement supérieur au protocole 10 Gigabit Ethernet. Le protocole 100 GbE offre différentes interfaces optiques et électriques et différents nombres de fibres optiques. Parmi les interfaces clés, citons 100GBASE-KR2, 100GBASE-CR2 et QSFP28.

LabVIEW FPGA est livré avec un exemple pour 100 GbE.

CPRI

CPRI définit l’interface optique entre le contrôle des équipements radio (REC) et les équipements radio (RE) communément appelés têtes radio distantes (RRH). Elle facilite la configuration et la synchronisation de la tête radio, ainsi que le transfert en continu des données I/Q numérique (bande de base). Pour en savoir plus sur le cœur IP CPRI de Xilinx, cliquez sur le lien suivant :

https://www.xilinx.com/products/intellectual-property/do-di-cpri.html

Serial RapidIO

Serial RapidIO est un protocole d'interconnexion série hautes performances, optimisé pour les systèmes embarqués à faible consommation d'énergie tels que les infrastructures de télécommunications, l'informatique embarquée dans le domaine militaire et aérospatial, les matériels à large bande passante pour les sciences de la vie et le contrôle industriel. Il offre des vitesses allant jusqu'à 6,25 Gbit/s, quatre voies, une faible latence, un contrôle de flux, une distribution de paquets dans l'ordre et un encombrement relativement faible. Pour en savoir plus sur le cœur IP Serial RapidIO de Xilinx, cliquez sur le lien suivant :

http://www.xilinx.com/products/intellectual-property/ef-di-srio.html

Une conception de référence de Serial RapidIO pour le module PXIe-6592 est disponible sur NI Community. Pour des interfaces SRIO supérieures à x2, NI recommande le PXIe-6591.

Protocoles supplémentaires

Les exemples précédents ne représentent pas une liste exhaustive de tous les protocoles compatibles avec les instruments série haute vitesse PXI. Les ingénieurs commerciaux NI locaux peuvent répondre aux questions sur des protocoles spécifiques, la personnalisation des exemples ci-dessus, ou l'intégration de protocoles propriétaires ou personnalisés.

Exemples d’applications

L’architecture flexible des instruments série haute vitesse PXI leur donne la capacité de prendre en charge une grande variété de cas d’utilisation, chacun avec des modèles de transfert de données, des protocoles série et des capacités logicielles différents.

Test fonctionnel du protocole

Les instruments série haute vitesse PXI sont souvent utilisés pour effectuer des tests fonctionnels spécifiques à un protocole sur un DUT donné. Ces tests sont conçus pour confirmer que le DUT peut communiquer de manière fiable avec le « monde extérieur » via un protocole série. De tels tests peuvent écrire et relire des registres sur le DUT, effectuer des tests de débit et de latence des données, ou exercer d’autres attributs spécifiques au protocole ou modes de test intégrés. Ils peuvent également tester la façon dont l'unité sous test répond aux scénarios d'erreur tels que les expirations de délai de réponse, les erreurs injectées ou les commandes de contrôle de flux ignorées. Les tâches associées incluent les mesures du taux d'erreur sur les bits de liaison, les tests de contrainte de la couche physique tels que les fréquences de ligne maximales et minimales, les tests de déverminage et même la surveillance de bus, pour laquelle l'instrument effectue une analyse, un déclenchement personnalisé et une capture de données sur le FPGA.

Contrôle, stimulus et réponse du DUT

Un autre cas d'utilisation courant des instruments série haute vitesse PXI est le contrôle, les stimulus et la capture de la réponse du DUT. Dans ce scénario, l’instrument ne teste pas nécessairement le protocole série haute vitesse directement, mais plutôt envoie ou reçoit des données du DUT à l’aide d’un protocole série haute vitesse, de sorte que d’autres aspects du périphérique peuvent être testés. De plus, les E/S numériques auxiliaires peuvent être utilisées pour contrôler le matériel sous test à l'aide de protocoles parallèles ou série basse vitesse, tels que SPI.

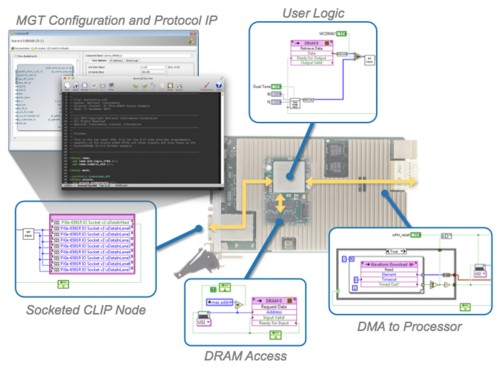

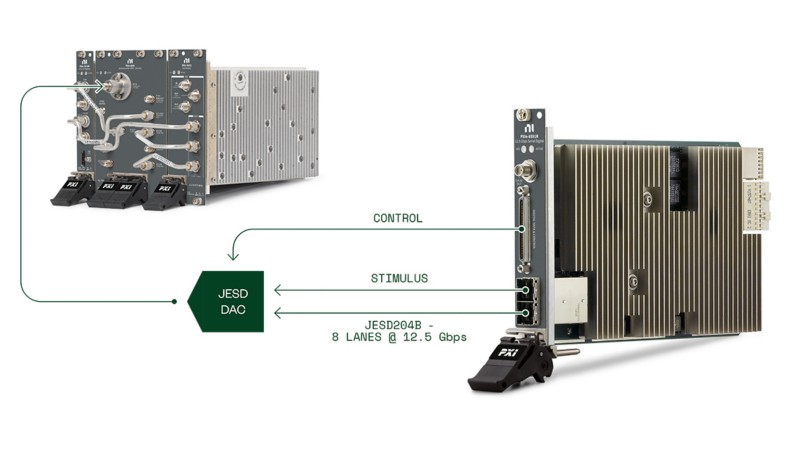

Dans l'exemple suivant, un PXIe-6591 stimule un C N/A à l'aide du protocole JESD204B afin de tester les caractéristiques de sortie analogique du C N/A.

Figure 8. De nombreux C N/A et C A/N hautes performances modernes incluent la communication à l’aide du protocole série haute vitesse JESD204B.

Transfert de données à large bande passante

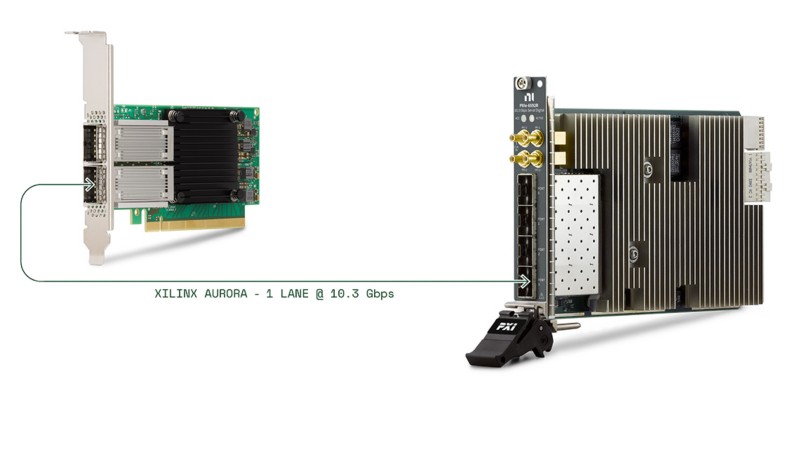

De nombreuses applications embarquées hautes performances peuvent tirer parti de la plate-forme PXI et nécessitent un transfert de données à large bande passante et à faible latence vers et depuis du matériel tiers et du matériel PXI de NI. Pour ces applications, les instruments série haute vitesse PXI offrent des avantages tels que le traitement matériel LabVIEW FPGA, le transfert en continu de données en P2P vers les instruments PXI Express et le transfert en continu à large bande passante vers et à partir du disque, tout en offrant une connectivité à large bande aux périphériques externes via un protocole série haute-vitesse.

Dans l'exemple suivant, un oscilloscope NI échantillonne un signal analogique puis envoie les données brutes numérisées à un instrument série haute vitesse PXIe-6592 en utilisant le transfert continu de données en P2P. L'instrument traite ensuite les données en temps réel à l'aide d'un algorithme implémenté dans LabVIEW FPGA. Il transmet enfin les données traitées à un appareil tiers à l’aide du protocole Xilinx Aurora léger, conçu pour la communication série FPGA vers FPGA.

Figure 9. Les instruments série haute vitesse PXI constituent une excellente solution pour le transfert de données à large bande passante et à faible latence avec un appareil tiers.

Mise au point des liens et test paramétrique

Étant donné que les interfaces série haute vitesse utilisent des signaux à très haute fréquence, une mauvaise intégrité du signal peut perturber la communication. Lorsque de tels problèmes surviennent, les outils de mise au point peuvent fournir des informations précieuses sur l’état de la liaison. La bibliothèque de conception d'instruments Eye Scan décrite précédemment permet aux concepteurs de déterminer la marge de liaison sur les signaux reçus et d'identifier si les problèmes de communication sont dus à une faible intégrité du signal. Bien que principalement conçue pour la mise au point pendant le développement de l’application, cette fonctionnalité peut également être utilisée dans la validation ou le test de fabrication d’un appareil pour avoir une idée des paramètres de performance spécifiques au périphérique. Cependant, les instruments série haute vitesse PXI présentent des valeurs nominales d’amplitude et de précision de cadencement, et NI ne garantit pas les performances ou la traçabilité de ces paramètres. L'étalonnage ou l'ajustement sur site peut être une option pour certaines applications.

D'autres tests paramétriques incluent le taux d'erreur sur les bits pour une séquence de bits pseudo-aléatoire (PRBS) connue utilisant des modèles standard de l'industrie (PRBS-7, PRBS-15, PRBS-23 et PRBS-31) au lieu d'un protocole spécifique. Les fréquences de ligne de l'émetteur et du récepteur peuvent varier afin de déterminer la gamme de débits binaires supportée pour un DUT particulier. Enfin, l'amplitude de l'émetteur ainsi que la pré-accentuation et la post-accentuation peuvent être modifiées pour tester la sensibilité du récepteur, y compris le contrôle automatique de gain et l'égalisation dynamique.

Pour les PXIe-6591 et PXIe-6592, vous trouverez des ressources supplémentaires au sein de la NI Community à l'aide du lien suivant : NI MGT Debug Tool sur NI Community pour obtenir davantage d'outils d'analyse de couche physique à utiliser avec les instruments série haute vitesse PXI. Pour les PXIe-6593 et PXIe-6594, reportez-vous à la référence Using Eye Scan with PXIe-6593 and PXIe-6594 High-Speed Serial Devices (Utiliser Eye Scan avec les appareils série haute-vitesse PXIe-6593 et PXIe-6594).

Compétences requises

Bien que LabVIEW et LabVIEW FPGA simplifient considérablement la tâche d'implémentation de la technologie série haute vitesse, une certaine expertise est essentielle pour garantir le succès de la programmation d'instruments série haute vitesse PXI. Dans la mesure où ils sont conçus en LabVIEW, il est essentiel de se familiariser avec la programmation graphique LabVIEW. La page de cours de formation NI LabVIEW Application Development sur ni.com peut vous aider. De plus, pour personnaliser la logique FPGA sans protocole dans LabVIEW FPGA, une compréhension détaillée de la programmation LabVIEW FPGA à haut débit est nécessaire. Le Guide du développeur FPGA hautes performances LabVIEW de NI est une bonne ressource pour obtenir davantage d’informations. Pour les protocoles avec des IP existantes ou des exemples, des connaissances et de l’expérience en VHDL sont nécessaires pour définir l’interface entre l’IP de protocole et le diagramme LabVIEW FPGA. Enfin, pour implémenter des protocoles nouveaux ou personnalisés, une expertise avancée en conception numérique est suggérée. Certains partenaires NI proposent ces fonctionnalités à ceux qui ne les possèdent pas en interne. Les représentants commerciaux NI locaux peuvent vous aider à trouver un partenaire approprié.

| Modèle d’utilisation | LabVIEW | LabVIEW FPGA haut débit | VHDL | Une grande expertise en conception numérique |

| Utiliser une personnalité existante | — | — | — | |

| Personnaliser le code FPGA, mais pas le protocole | — | — | ||

| Intégrer le protocole existant | — | |||

| Implémenter un protocole nouveau ou personnalisé |

Tableau 4. La programmation d'instruments série haute vitesse nécessite différents niveaux de compétences et d'outils en fonction du niveau de modifications de l'interface.

Étapes suivantes

- En savoir plus sur l'optimisation des transferts de données et le traitement du signal avec le module série haute vitesse PXI.

- Apprenez-en davantage sur les concepts fondamentaux des liens de communication série haute vitesse.

- Consultez un exemple de conception de référence pour l'implémentation de protocoles série haute vitesse dans des systèmes de test fonctionnel pour émetteurs-récepteurs.

- Obtenez des conceptions de référence de protocole supplémentaires non incluses dans le driver matériel provenant des exemples et IP pour les instruments conçus par logiciel et de la communauté NI FlexRIO.

- Achetez des instruments série haute vitesse PXI.

- Construisez votre système PXI.