La série haut débit expliquée

Aperçu

La technologie série haut débit est une technologie de plus en plus populaire qui permet de réduire l’encombrement des périphériques et d’augmenter les taux de communication des données. Cet article explore les concepts fondamentaux des liaisons de communication série haut débit.

Contenu

- La nécessité d’une liaison série haut débit

- Couches de liaisons série haut débit

- Conclusions

- Contenu associé

La nécessité d’une liaison série haut débit

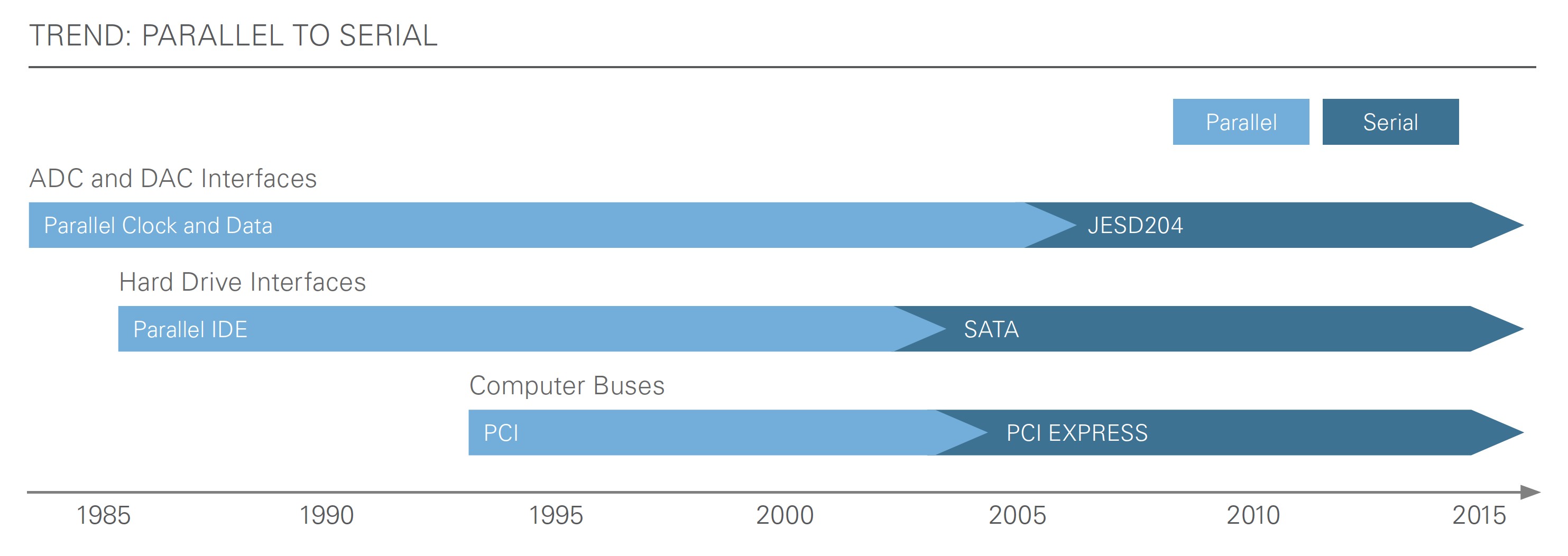

Les consommateurs exigent continuellement de meilleures performances dans un format plus petit avec une consommation d’énergie réduite. Au début des années 2000, ces exigences dans un monde de big data ont entraîné un changement radical des bus de communication numérique parallèles aux bus de transmission série haut débit numérique. Cela a permis de créer des périphériques dont l’empreinte est beaucoup plus petite, le débit de données beaucoup plus élevé et la consommation d’énergie plus faible. Ces fonctionnalités permettent l’utilisation de nombreuses technologies dont les consommateurs profitent aujourd’hui, telles que SATA, USB et PCI Express.

Figure 1 : Au début des années 2000, le marché a commencé à passer de normes de communication parallèle communes à des normes série.

Avantages

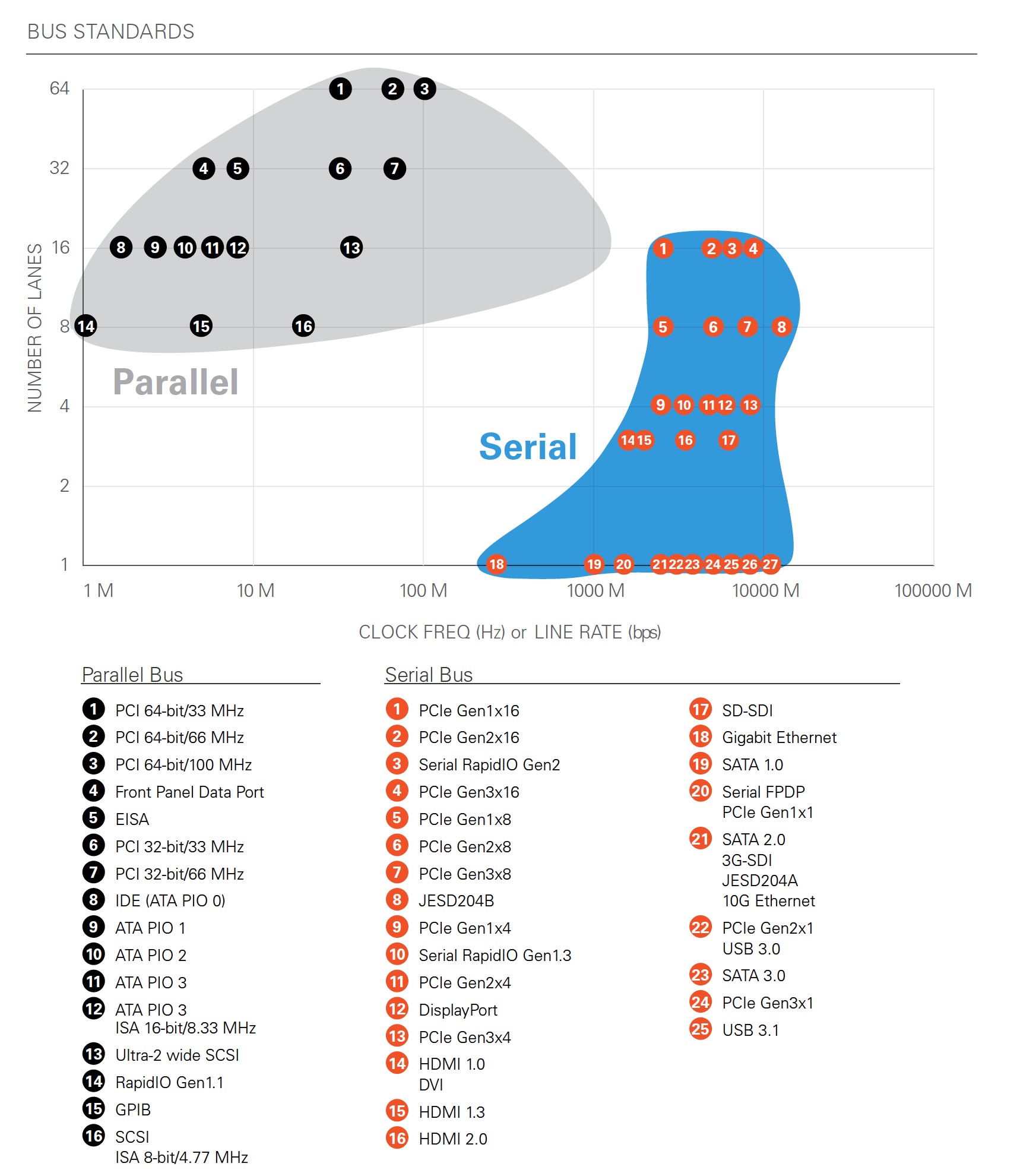

La limitation physique des fréquences d’horloge des bus parallèles est d’environ 1 à 2 GHz en raison du décalage introduit par les lignes d’horloge et de données individuelles, qui provoque des erreurs de bits à des fréquences plus élevées. Les bus série haut débit envoient des données codées qui contiennent à la fois des données et des informations d’horloge dans un seul signal différentiel, ce qui permet aux ingénieurs d’éviter les limitations de vitesse des bus parallèles. Aujourd’hui, les liaisons série haut débit avec des voies de données fonctionnant à 10 Gbps sont courantes. De plus, plusieurs voies de liaisons série peuvent être reliées de manière cohérente pour former des voies de communication avec des débits de données plus élevés.

En sérialisant les données et en les envoyant à des vitesses plus rapides, le nombre de broches dans les circuits intégrés (CI) peut être réduit, ce qui permet de réduire la taille du périphérique. De plus, comme les voies série peuvent fonctionner à une vitesse d’horloge beaucoup plus rapide, vous pouvez obtenir un meilleur débit de données qu’avec des bus parallèles.

Figure 2 : Ce graphique présente les normes de bus les plus connues et leur nombre respectif de voies par rapport aux fréquences de ligne. Les normes série permettent des fréquences de ligne beaucoup plus élevées que les normes parallèles, ce qui se traduit par un débit plus important.

Inconvénients

Bien que la réduction du nombre de broches puisse réduire la complexité de la conception ; les vitesses plus rapides requises posent des problèmes de conception supplémentaires. Lorsque les conceptions atteignent les radio-fréquences, vous devez prendre en compte les mêmes considérations analogiques que pour les applications RF afin de garantir l’intégrité du signal. Pour atténuer ces problèmes d’intégrité du signal, vous pouvez utiliser des liaisons série haut débit pour mettre en œuvre des techniques telles que le codage, la pré-accentuation et l’égalisation.

Couches de liaisons série haut débit

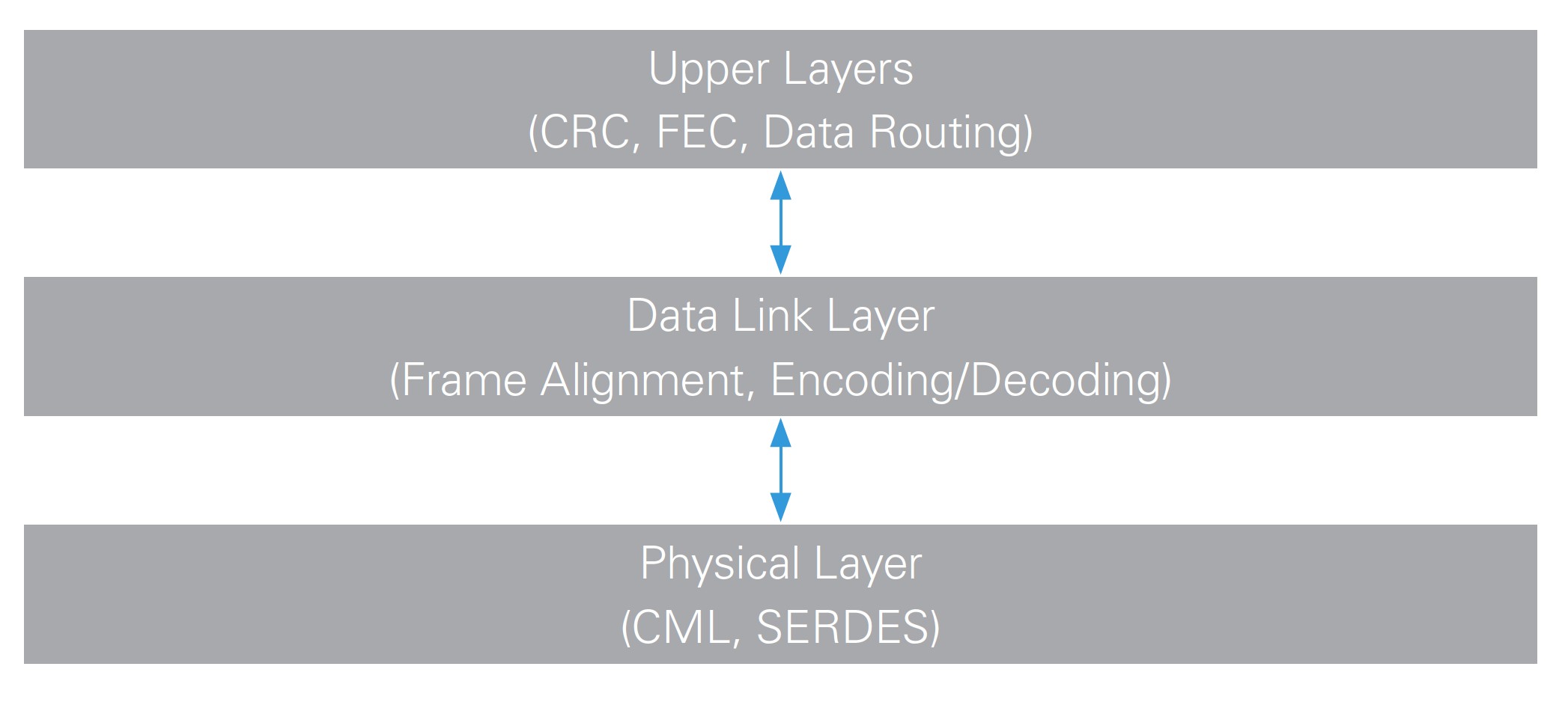

Pour qu’une connexion série fonctionne, chaque extrémité doit accepter de fonctionner selon des paramètres spécifiques. Vous pouvez abstraire ces paramètres pour les appliquer à plusieurs couches fonctionnelles.

Figure 3 : Vous pouvez ajouter des couches au-dessus de la couche physique et de la couche de liaison de données. Ces couches varient en fonction du protocole ainsi que de l’application et sont généralement les couches les plus courantes à personnaliser.

Couche physique

La couche physique assure la compatibilité électrique entre les périphériques et présente des bits synchronisés à la couche de liaison de données.

Interface électrique

Différents protocoles série haut débit définissent différentes exigences pour l’interface électrique de l’émetteur et du récepteur. Ceci garantit la compatibilité électrique lors de la connexion de l’émetteur au récepteur. Le signal électrique pour les liaisons série haut débit a du mal à atteindre les temps de montée et de descente extrêmement rapides nécessaires pour communiquer à des vitesses supérieures à 1 Gbps, à minimiser les émissions électromagnétiques et à améliorer l’immunité au bruit en rejetant les bruits en mode commun. De plus, les tensions de crête dépassent rarement 1 V à ces vitesses, et les normes électriques sont généralement la transmission différentielle basse-tension (LVDS), la logique à émetteurs couplés (ECL) ou logique par commutation de courant (LCC).

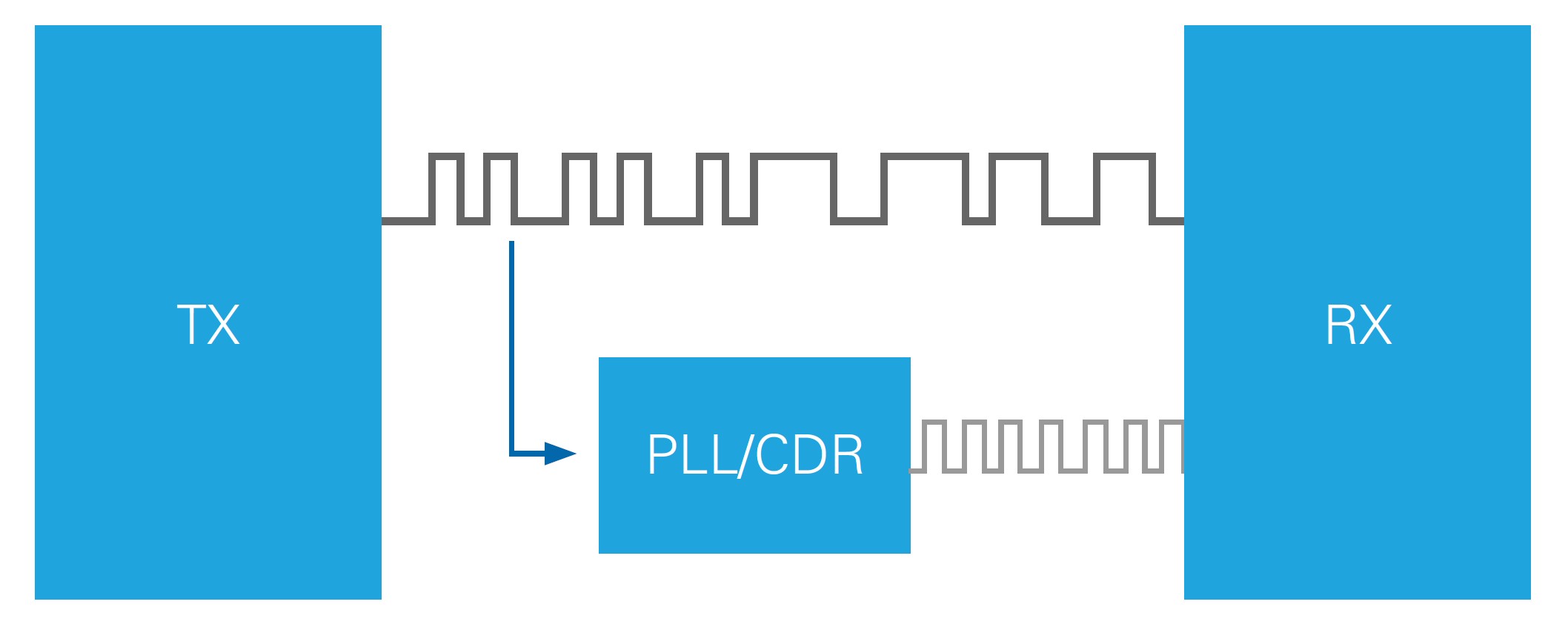

Récupération de données et d’horloges

Une autre caractéristique importante de la couche physique pour les liaisons série haut débit est la récupération de données et d’horloges (CDR). La CDR est la capacité du périphérique de réception à cadencer le flux de données entrant sans avoir besoin d’un signal d’horloge réel. Le calque de liaison de données y contribue en assurant des transitions bits fréquentes par le biais du codage. Cela permet aux circuits à boucle à phase asservie (PLL) et d’interpolateur de phase (PI) de recréer l’horloge émission et de l’utiliser pour capturer le flux de données entrant avec une erreur de synchronisation minimale.

Figure 4 : Comme le codage au niveau de la couche de liaison de données assure des transitions fréquentes entre 0 et 1, le circuit CDR peut effectuer une PLL sur le « bit stream » entrant et échantillonner de manière synchrone les bits de données codées.

Considérations relatives à l’intégrité du signal

La transmission de données avec des bits transitant à des fréquences de 5 GHz ou plus pose des problèmes de conception analogique. Comme les vitesses de transmission se situent désormais dans des gammes de fréquences typiques des conceptions RF, des problèmes d’intégrité du signal se posent. Vous devez utiliser des circuits imprimés, des connecteurs et des câbles de haute qualité pour communiquer avec succès à ces débits de données élevés. De plus, les concepteurs de circuits imprimés doivent comprendre la théorie des lignes de transmission lors de la conception de liaisons série haut débit. Ils doivent être en mesure d’éviter les stubs, les disparités d’impédance et la non-concordance de la longueur des lignes et d’utiliser des techniques appropriées pour minimiser les distorsions du signal.

Égalisation

L’égalisation est le processus qui consiste à contrecarrer le comportement électrique d’un canal pour augmenter sa réponse en fréquence. Ceci peut se produire du côté de l’émetteur ou du récepteur de la liaison de communication pour améliorer la marge de liaison, mais le terme « égalisation » est généralement utilisé dans le cadre du récepteur. Lorsque le signal série haut débit circule sur les lignes des circuits imprimés, à travers les connecteurs et les câbles, jusqu’au récepteur, l’atténuation n’affecte pas toutes les composantes fréquentielles du signal de la même manière et provoque une distorsion du signal. Les paramètres d’égalisation des émetteurs-récepteurs multi-gigabit (MGT) peuvent appliquer un gain ou une atténuation à différentes fréquences du signal avant qu’il soit échantillonné pour améliorer la marge du signal et de la liaison. De nombreux MGT sont dotés d’un système d’égalisation automatique qui détecte automatiquement les égaliseurs et les met continuellement à jour en fonction de leurs réglages idéaux.

Pré-accentuation

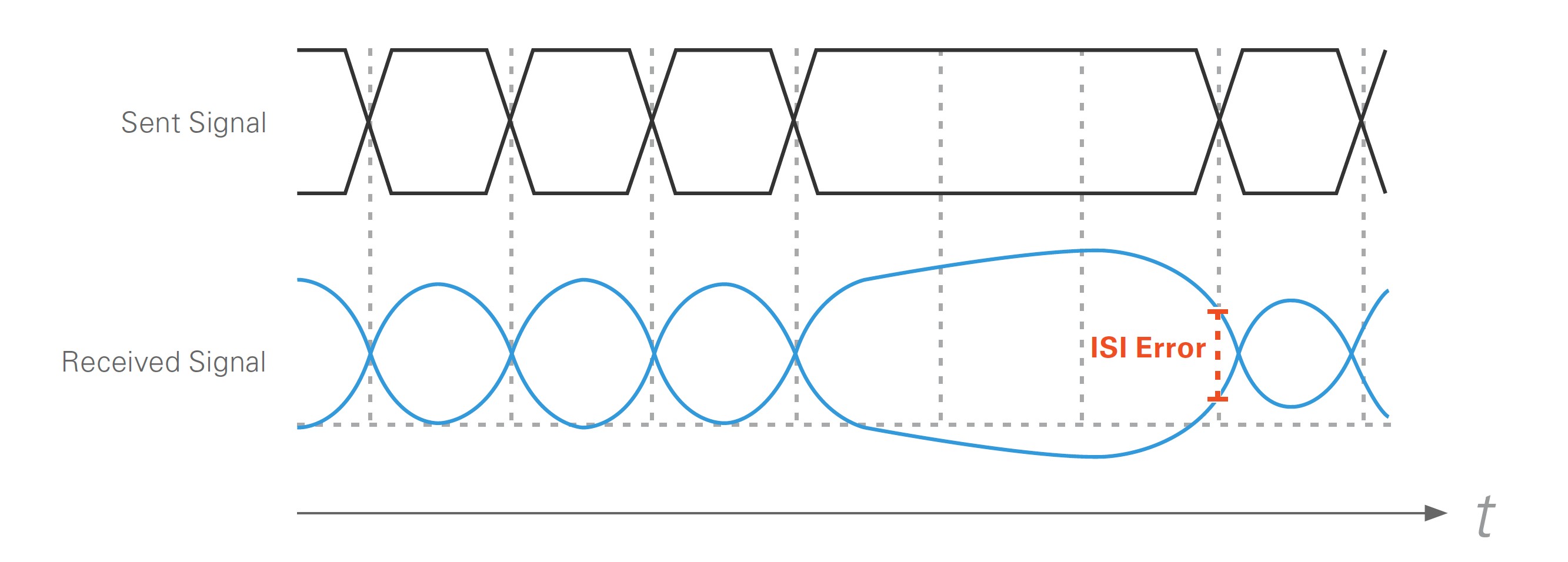

La pré-accentuation fait généralement référence à l’égalisation du côté de l’émetteur d’une liaison série haut débit. Elle est principalement utilisée pour surmonter les difficultés analogiques présentées par l’interférence inter-symbole (ISI). À des débits élevés, les bits de données commencent à s’influencer les uns les autres lors de la transmission. Par exemple, si trois 1 sont transmis d’affilée, suivis d’un seul 0, la ligne de données a du mal à abaisser rapidement le 0, car la ligne a accumulé une polarisation positive.

Figure 5 : La dégradation du signal due à l’ISI se produit lorsqu’un manque de transitions de bits provoque une polarisation sur la ligne, ce qui complique le passage rapide de la première transition au bit opposé.

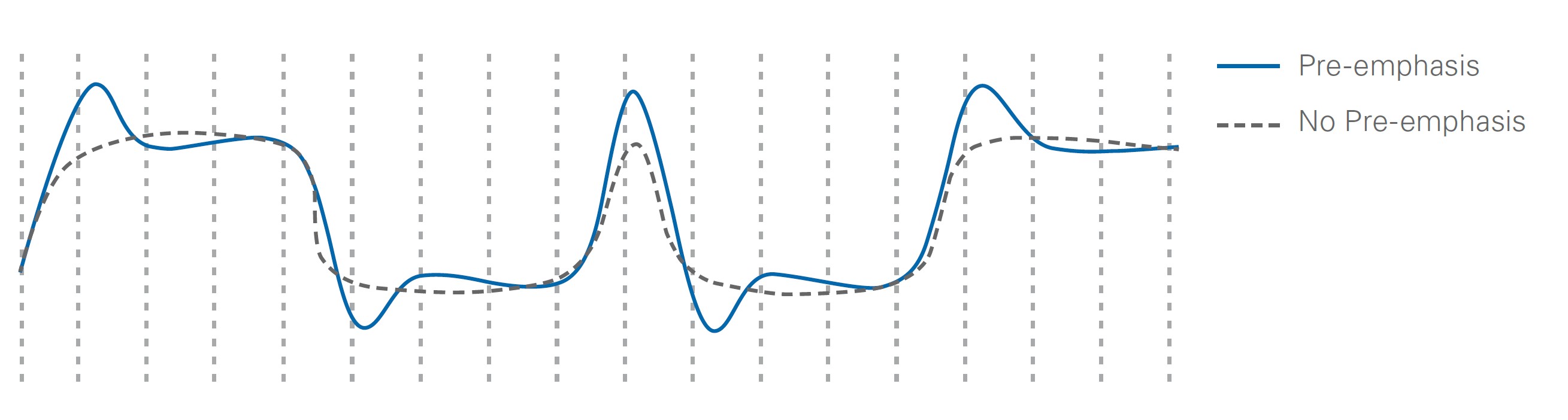

Il y a deux façons de surmonter l’ISI. Si vous savez que seul le premier bit après une transition de bas à haut ou de haut à bas pose problème, vous pouvez amplifier uniquement le premier bit après une transition. Le signal obtenu est celui de la figure 6.

Figure 6 : La pré-accentuation est conçue pour exagérer le premier bit après une transition d’un signal. Cela permet d’atténuer des problèmes tels que l’ISI.

Une approche plus courante pour obtenir une forme d’onde similaire consiste à atténuer les bits après la première transition au lieu d’amplifier le premier bit. Le filtrage passe-haut y parvient, car les bits de transition (fréquence plus élevée) sont moins atténués que les bits de non-transition.

Couche de liaison de données

La couche de liaison de données manipule les données afin d’améliorer l’intégrité du signal, d’assurer une bonne communication et de faire correspondre les bits physiques aux données. Les fonctionnalités qui permettent cela sont les schémas de codage et les caractères de contrôle pour l’alignement, la correction d’horloge et le « channel bonding ».

Schémas de codage

L’objectif du codage est de garantir des transitions de bits fréquentes pour une CDR réussie, et d’assurer un équilibrage CC pour les données. Pour une CDR réussie, le schéma de codage doit veiller à ce que le signal de données présente suffisamment de transitions pour que le circuit CDR reste en phase avec le flux de données. Si la PLL à l’intérieur du circuit CDR ne peut pas rester verrouillée à cause d’un manque de transitions, le récepteur ne peut pas garantir l’horloge synchrone des bits de données, et des erreurs de bits ou une défaillance de liaison se produisent. Pour réaliser la CDR, vous devez vous assurer que les symboles avec des transitions de bits fréquentes sont transmis, ce qui entraîne l’ajout de bits supplémentaires aux données.

L’équilibre CC est également important pour assurer le bon fonctionnement de la liaison série. Si vous ne régulez pas la quantité d’équilibre CC, les signaux risquent de s’éloigner de leurs niveaux logiques haut et bas idéaux, et des erreurs de bits peuvent se produire. L’équilibre CC est assuré en équilibrant la quantité statistique de 1 et 0 dans les symboles transmis. Dans un signal équilibré en courant continu, le nombre de 0 et de 1 transmis au fil du temps est statistiquement égal.

Codage 8b/10b

Un schéma de codage courant est le 8b/10b. Pour chaque tranche de huit bits de données, deux bits supplémentaires sont ajoutés pour le codage. Ces deux bits supplémentaires fournissent quatre fois plus de représentations de bits (symboles) que huit bits de données. L’encodeur 8b/10b réduit ses nombreuses options de symboles en choisissant les symboles prédéfinis avec le plus grand nombre de transitions et le meilleur équilibre CC pour correspondre à des mots de données et des symboles de contrôle spécifiques. Il stocke ces symboles dans des tables de correspondance utilisées pour coder et décoder les données.

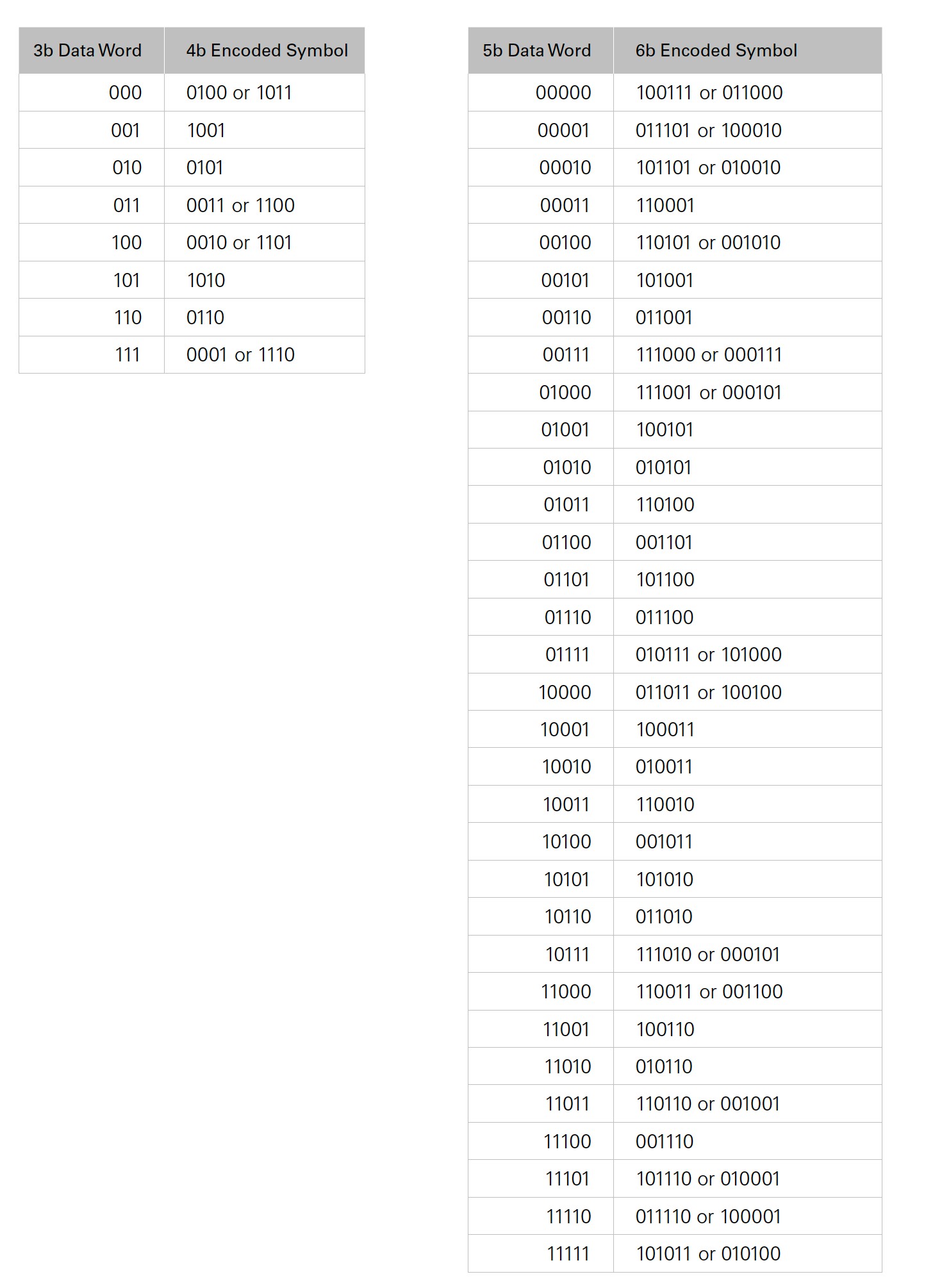

Lorsqu’un bloc de données de 8 bits est prêt à être codé, le codeur le décompose en cinq et trois bits, et effectue un codage séparé 5b/6b et 3b/4b sur le bloc de données. Il envoie les cinq bits les moins significatifs de la table 5b/6b et les trois bits les plus significatifs de la table 3b/4b.

Tableau 1 : L’encodeur encode des blocs de données de 8b en envoyant les trois bits les plus significatifs à une table 3b/4b et les cinq bits les moins significatifs à une table 5b/6b. L’encodeur les combine ensuite en fonction de la disparité en vigueur pour former un symbole 10b avec des transitions fréquentes pour le circuit CDR.

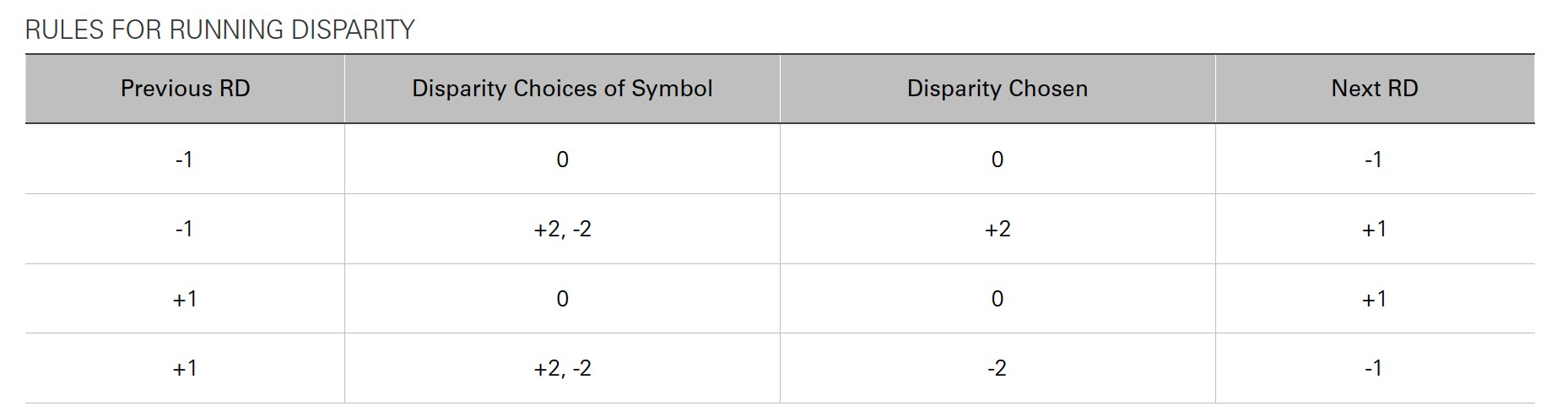

Dans une situation idéale, tous les symboles présentent un nombre égal de 0 et de 1 pour maintenir l’équilibre du courant continu. Mais ce n’est pas le cas pour les symboles des tables 5b/6b et 3b/4b. Des règles ont donc été mises en place pour prendre des décisions basées sur un concept connu sous le nom de « disparité courante ». Il s’agit de la différence cumulée entre le nombre de 1 et de 0 qui ont été transmis. Il n’y a pas assez de symboles avec un nombre égal de 1 et de 0 pour représenter 8 bits, de sorte que certains blocs de données sont représentés par deux symboles : un symbole avec plus de 0 que de 1 et un symbole avec plus de 1 que de 0. Par exemple, le symbole de la table 3b/4b de 1101 peut également être représenté par 0010. Lorsque vous choisissez la version du symbole à utiliser, l’encodeur essaie toujours d’équilibrer la disparité courante. La disparité d’un symbole 8b/10b complet est toujours 0, +2 ou -2. La table 2 montre comment l’encodeur décide du symbole qu’il doit utiliser.

Table 2 : Les règles de la disparité courante déterminent la version du mot-code utilisée pour assurer l’équilibre du courant continu.

Prenons l’exemple du codage du mot 10010001 contenant des données. Les trois bits les plus importants (100) sont envoyés à la table 3b/4b, et les cinq bits les moins importants (10001) sont envoyés à la table 5b/6b. Si c’est le premier mot envoyé sur la ligne, l’encodeur suppose une disparité -1 ; par conséquent, cet exemple suppose que la disparité courante est -1. La partie 5b/6b n’a pas de choix à faire, tandis que la partie 3b/4b décide si la disparité est de +2 ou de -2. La disparité courante étant de -1, le code 3b/4b avec disparité +2 (1101) est choisi. Lorsque les codes 3b/4b et 5b/6b sont combinés, le symbole encodé total est 1101100011. Une fois ce symbole transmis, la disparité courante est maintenant +1 = -1 + 2.

Codage 64b/66b

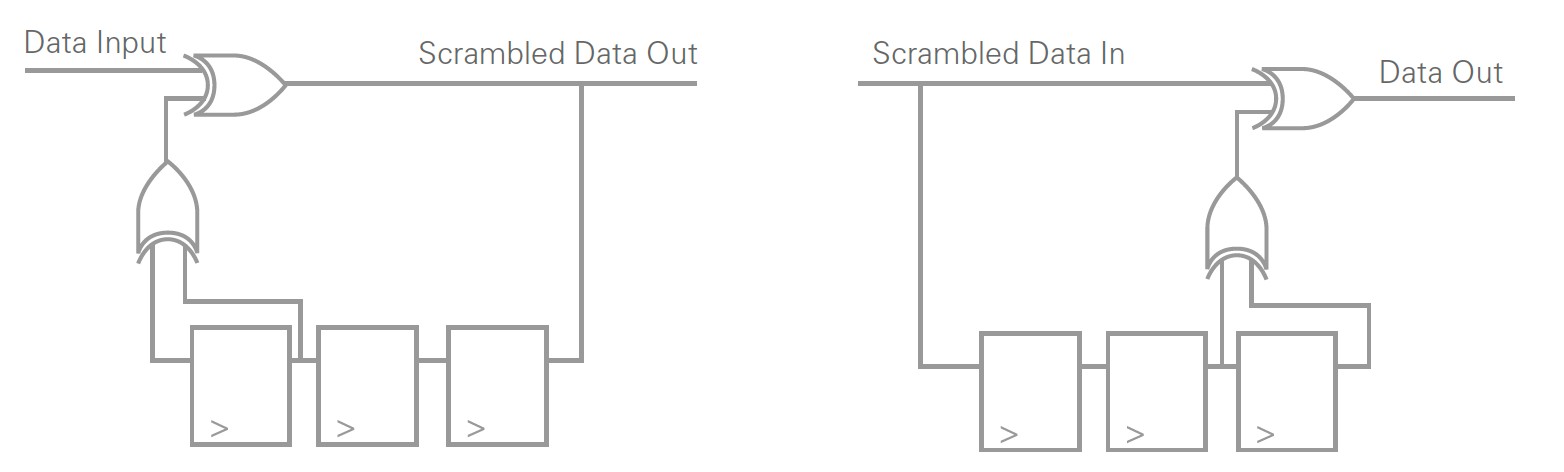

En utilisant une approche différente du codage 8b/10b, le codage 64b/66b peut accomplir des tâches similaires. Au lieu de tables de code, il utilise le brouillage. Le brouillage nécessite un circuit matériel qui offre une forte probabilité d’obtenir des 0 et des 1 multiples, espacés de façon relativement régulière. Le brouillage permet aux données codées d’apparaître comme aléatoires avec des transitions fréquentes, mais elles peuvent toujours être désembrouillées du côté du récepteur.

Figure 7 : Un circuit de brouillage fait apparaître les données de sortie comme aléatoires et équilibrées en courant continu, mais les données peuvent toujours être désembrouillées du côté du récepteur. Le brouillage est une méthode alternative au codage des données avec une table de correspondance.

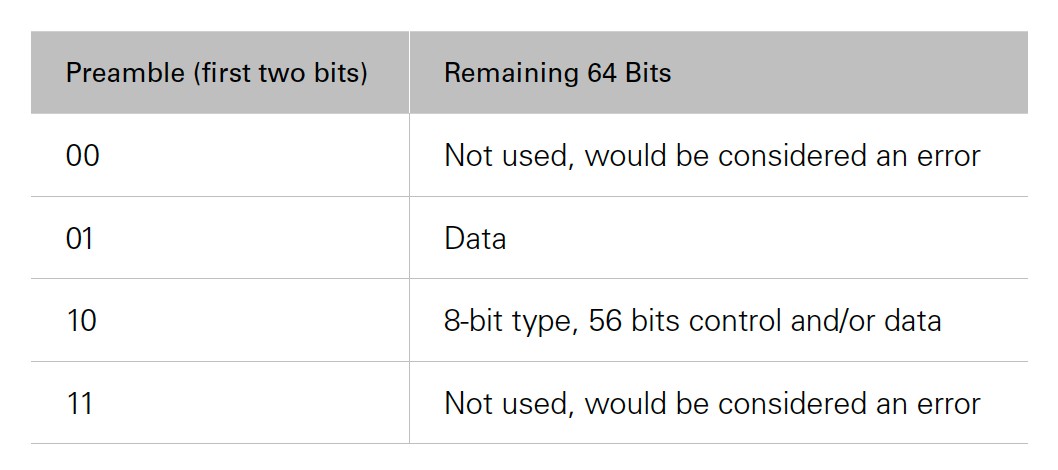

Les deux premiers des 66 bits sont considérés comme le préambule et fournissent des informations sur les 64 bits restants. Le principal avantage du 64b/66b par rapport au 8b/10b est la réduction de la surcharge. Le 64b/66b comporte un peu plus de 3 % de surcharge, tandis que le 8b/10b en comporte 20 %. L’un des inconvénients du codage 64b/66b est qu’il n’a pas de limite sur l’équilibre en courant continu comme le codage 8b/10b. Bien que les circuits de brouillage se soient avérés très efficaces pour donner l’impression d’être aléatoires et pour présenter un déséquilibre de courant continu statistiquement insignifiant, le codage 64b/66b n’est pas limité comme le codage 8b/10b.

Table 3 : Les deux premiers bits d’un symbole 64b/66b sont considérés comme un préambule. Le préambule fournit au décodeur des informations sur les 64 bits qui le suivent. Les significations du préambule de la table 3 s’appliquent à 10 Gigabit Ethernet.

64b/67b

Certains appareils électroniques sont trop sensibles au décalage du courant continu au fil du temps. C’est peut-être le cas pour le schéma de codage 64b/66b. Il peut ne pas être intéressant pour les concepteurs parce que le décalage de courant continu n’est pas limité. Dans ces situations, les ingénieurs sont confrontés à la surcharge plus élevée (20 %) du schéma 8b/10b. Le schéma 64b/67b ajoute un bit supplémentaire de surcharge, ce qui lui permet de limiter la disparité courante à ±96.

L’émetteur surveille la disparité courante et calcule la disparité des nouveaux mots-codes brouillés. Si le nouveau mot-code réduit le nombre de disparités, il transmet ce symbole. Si le nouveau mot-code augmente le nombre de disparités, l’encodeur inverse les 64 bits brouillés (il n’est pas nécessaire d’inverser le préambule dont la disparité est nulle). Le bit supplémentaire est appelé bit d’inversion et indique au décodeur s’il doit inverser les données ou non. Cela permet aux composants électroniques sensibles au décalage de courant continu de bénéficier d’un système de codage à faible surcharge qui présente également un décalage de courant continu limité.

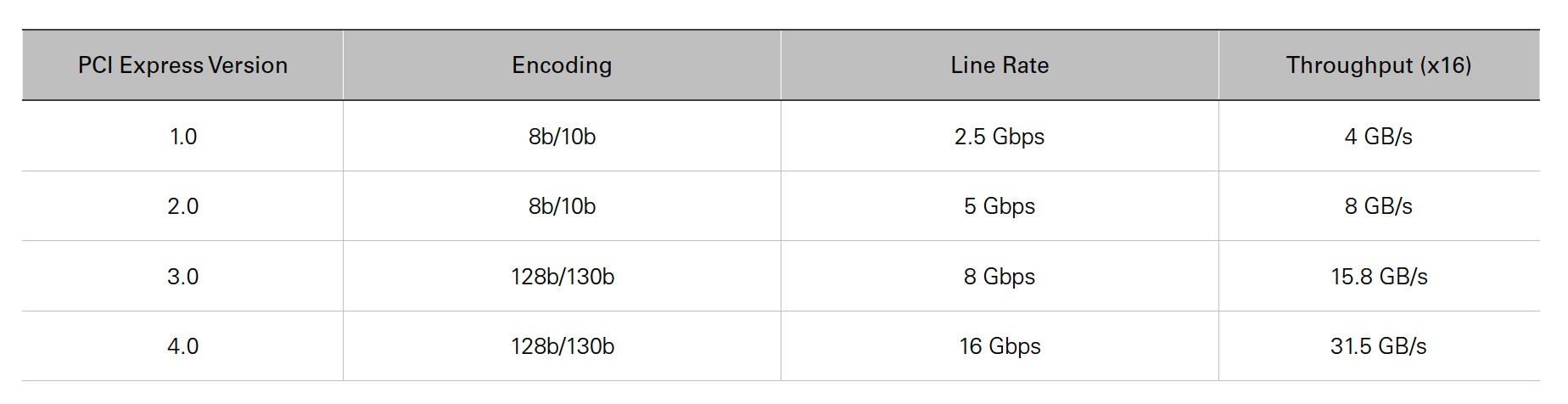

128b/130b

PCI Express 1.0 et 2.0 utilisent tous deux 8b/10b, tandis que PCI Express 3.0 et 4.0 sont passés à 128b/130b pour obtenir un débit de données plus élevé avec une fréquence de ligne réalisable. Imaginez le schéma 128b/130b comme 64b/66b avec une charge utile doublée et toujours seulement deux bits de préambule. La table 4 présente les spécifications de PCI Express.

Table 4 : Cette table présente les spécifications des quatre générations de PCI Express. PCI Express 3.0 et 4.0 sont passés à 128b/130b pour augmenter leur débit de données, tout en maintenant leurs fréquences de ligne à une vitesse plus gérable.

Symboles de contrôle (caractère spécial « K »)

Les symboles de contrôle, également connus sous le nom de caractère spécial « K » dans le cadre du codage 8b/10b, constituent une fonction importante des liaisons série haut débit. Ce sont des symboles qui peuvent être différenciés des données, de sorte que le récepteur peut les utiliser pour différentes tâches de contrôle, telles que l’alignement des limites d’octets avant le décodage, les techniques de correction d’horloge et le « channel bonding » pour la cohérence des données sur plusieurs voies.

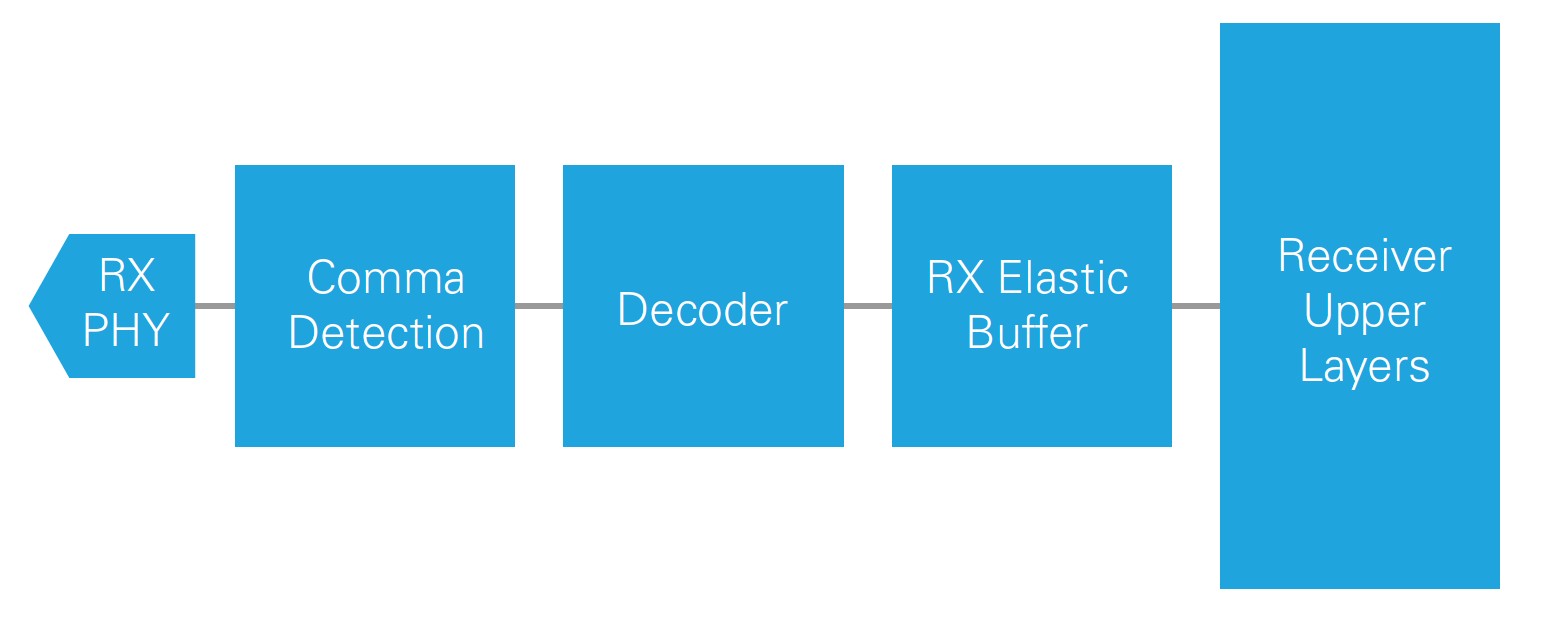

Alignement et détection des virgules

Pour que le décodage fonctionne correctement, le récepteur doit connaître les limites de mot correctes des données codées. Le récepteur analyse les données entrantes à la recherche du caractère de contrôle, également appelé virgule lorsqu’il est utilisé pour l’alignement dans le schéma 8b/10b. Le caractère de contrôle définit la limite des données codées. Une fois que le récepteur a identifié le caractère d’alignement, il comprend les limites du mot pour les données codées, de sorte que les données codées peuvent être envoyées à la logique de décodage.

Caractères de correction de l’horloge

La correction d’horloge est nécessaire chaque fois que l’horloge d’émission n’est pas verrouillée sur la même source que l’horloge de réception. Même si ces horloges ont la même fréquence nominale, elles s’éloignent lentement l’une de l’autre en raison de petites imprécisions dans la fréquence de l’horloge. Le fait de recourir au principe « premier entré, premier sorti » (PEPS ou FIFO en anglais) permet au récepteur de tenir compte des différences d’horloge mineures entre l’émetteur et le récepteur et de mettre en œuvre une correction d’horloge.

Figure 8 : Le tampon élastique RX entre les couches supérieures du décodeur et du récepteur est nécessaire pour mettre en œuvre la correction d’horloge. Il met les données en mémoire tampon pour éviter les erreurs dues à la dérive des horloges déverrouillées l’une par rapport à l’autre et permet les communications entre deux périphériques sans qu’ils partagent une horloge de référence.

La logique de correction d’horloge garantit que la mémoire tampon élastique n’est jamais saturée. Si l’horloge d’émission est légèrement plus rapide que l’horloge de réception lors de la lecture du tampon élastique, un débordement peut se produire si vous ne disposez pas de techniques de correction d’horloge. Si l’horloge d’émission est légèrement plus lente que la logique de lecture du récepteur, un soupassement de capacité peut se produire en l’absence de correction d’horloge.

Un caractère de contrôle est choisi comme caractère de correction d’horloge. L’émetteur envoie ce caractère de correction d’horloge périodiquement entrelacé avec des données réelles, et la fréquence de ce caractère de correction d’horloge dépend des besoins de correction d’horloge de l’application et de la conception du matériel. Si la logique de correction d’horloge du récepteur détecte que la mémoire tampon élastique du récepteur connaîtra un soupassement, la logique de correction du récepteur peut insérer des caractères de correction d’horloge supplémentaires pour garantir que le soupassement de la mémoire tampon ne se produise pas. Si la logique de correction d'horloge détecte que la mémoire tampon élastique est trop pleine et prête à déborder, elle peut jeter les séquences de correction d'horloge dans la mémoire tampon afin de créer de l'espace supplémentaire pour les données.

Channel Bonding

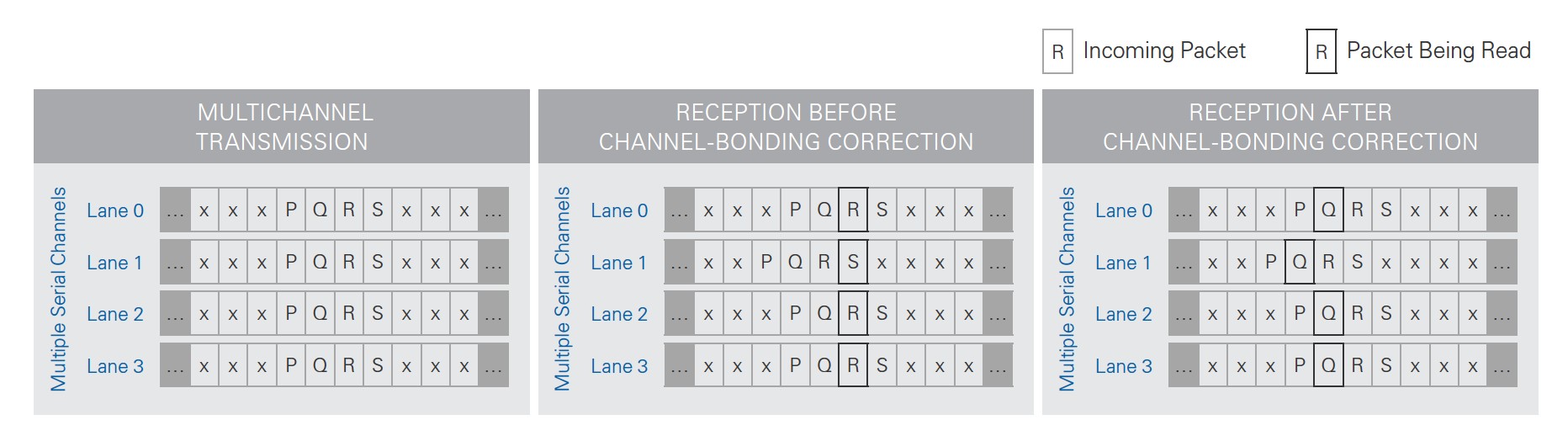

Si la fréquence de ligne et le schéma de codage ne permettent pas d’obtenir le débit de données dont vous avez besoin sur une seule voie série, vous pouvez utiliser plusieurs voies. Les normes HDMI utilisent, par exemple, trois voies de données série pour atteindre leur largeur de bande globale. Lors de l’envoi de données sur plusieurs voies, les temps de propagation font que les données arrivent à différents moments sur chaque voie de réception au niveau du récepteur. Selon l’application, vous devrez peut-être aligner les données sur toutes les voies du récepteur, un processus connu sous le nom de « channel bonding ». Le tampon élastique dans chaque voie de réception du récepteur utilisé pour la correction de l’horloge est également utilisé pour le « channel bonding ».

Pour réaliser le « channel bonding », vous devez choisir un caractère de contrôle spécial et le réserver au « channel bonding ». La liaison série comporte un canal « maître », les autres étant considérées comme des canaux « esclaves ». Le maître et tous les esclaves envoient le caractère de « channel bonding »en même temps à partir des émetteurs. Lorsque le récepteur maître voit la séquence de liaison de canal à un certain endroit de la mémoire tampon élastique, il demande à tous les esclaves de trouver leurs séquences de liaison et ajuste les pointeurs de lecture de toutes les mémoires tampons élastiques au décalage de l’emplacement de la séquence de liaison de canal. Comme chaque voie de données a son propre décalage pour sa propre mémoire tampon élastique, le récepteur peut lire à partir de différents emplacements de chaque mémoire tampon élastique, ce qui permet de lire des données alignées.

Figure 9 : Le « channel bonding » modifie les pointeurs de lecture de la mémoire tampon élastique sur chaque canal de réception afin de permettre au récepteur de lire des données synchrones sur plusieurs canaux de données.

Caractères de synchronisation

Le caractère de synchronisation est un autre cas d’utilisation important des caractères de contrôle. Pour que l’horloge et la récupération des données restent en phase, l’émetteur doit continuellement envoyer des bits. Lorsqu’il n’a pas de données à envoyer, il doit envoyer un caractère de synchronisation. Il s’agit d’un autre caractère de contrôle déterminé par le protocole, et le récepteur sait que ce caractère n’est pas une véritable donnée.

Couches supérieures supplémentaires

Des couches supérieures supplémentaires se trouvent au-dessus de la couche de liaison de données pour vous aider à adapter la communication à vos besoins spécifiques. Certains protocoles ont des normes spécifiques pour les fonctions de la couche supérieure, tandis que d’autres protocoles vous laissent le choix. Les personnalisations de communication courantes incluent le contrôle et la correction des erreurs, les informations d’en-tête pour les communications par paquets ou même les informations sur l’état de la liaison.

Les couches au-dessus de la couche de liaison de données et de la couche physique sont les couches les plus souvent adaptées pour répondre aux besoins spécifiques des applications. La détection et la correction des erreurs par le contrôle de redondance cyclique (CRC) et la correction d’erreur directe (FEC) sont des exemples d’adaptations courantes de la couche supérieure. En contrepartie de l’efficacité du transfert de données, vous pouvez utiliser des schémas pour détecter ou corriger des erreurs. Le CRC met en place des règles pour détecter les erreurs de bits dans la transmission, mais ne peut pas les corriger. Vous pouvez personnaliser l’application pour qu’elle demander à nouveau des données. La FEC, au contraire, contient des informations de correction d’erreur supplémentaires dans les données transmises qui peuvent permettre au récepteur de récupérer un nombre limité d’erreurs de bits. Ceci est utile pour les canaux bruyants ou les vitesses de communication si élevées que les erreurs de bits dues à l’intégrité du signal sont plus fréquentes. L’inclusion de la FEC est une décision de conception qui sacrifie l’efficacité de la vitesse des données pour des exigences d’intégrité du signal moins strictes.

Conclusions

Vous devez surmonter de nombreux défis à plusieurs couches du lien série haut débit pour communiquer avec succès. La compréhension des différents concepts à chaque niveau vous aide à mettre en œuvre et à tester différentes couches. Pour qu’une couche fonctionne, les couches inférieures doivent fonctionner correctement. En utilisant l’une des nombreuses spécifications définies pour les couches physiques et de liaison de données, vous n’avez pas besoin de déterminer vous-même les détails de bas niveau. Un autre avantage de l’utilisation d’une couche physique et d’une couche de liaison de données standard est le protocole Internet (IP) qui met en œuvre tous ces détails de bas niveau pour vous. Le protocole Aurora de Xilinx en est un bon exemple : il s’agit d’un IP gratuit qui met en œuvre un protocole léger de couche de liaison de données pour les communications série point à point. Cela vous permet de faire abstraction des petits détails tels que la correction d’horloge, la liaison des canaux, le caractère d’inactivité, le codage/décodage, etc., afin que vous puissiez vous concentrer sur les couches supérieures, spécifiques à l’application.

Avec les avantages d’une taille et d’une puissance réduites, associés à une amélioration des performances, les liaisons série haut débit gagnent rapidement en popularité. L’industrie des communications améliore continuellement les technologies série haut débit pour atteindre des fréquences de ligne plus rapides et rendre possible le monde des big data.