El controlador para FlexRIO: Una exploración profunda de la instrumentación desplegable

Información general

El controlador para FlexRIO es una solución comercial diseñada para aplicaciones que requieren E/S de alto rendimiento y procesamiento de señales en tiempo real en un formato compacto y autónomo. La combinación de E/S modular, un FPGA programable en LabVIEW y un procesador interno, brinda a los estudiantes la habilidad de reconfigurar completamente el hardware para aplicaciones específicas, lo cual diferencia al controlador para FlexRIO de la mayoría instrumentación comercial. El controlador también comparte los mismos módulos adaptadores, FPGAs y la experiencia de software de FlexRIO en PXI, lo cual lo hace un dispositivo ideal para soluciones desarrolladas en la plataforma PXI. Aunque tiene mucho en común con FlexRIO en PXI, que está dirigido a aplicaciones embebidas, donde se prefieren soluciones más pequeñas, más ligeras y de menor potencia.

Contenido

- Arquitectura interna

- Interfaz del módulo adaptador para FlexRIO

- FPGA

- Serial de alta velocidad

- Sincronización

- Procesador

- Conectividad

- Empaque físico

- Resumen

- Pasos siguientes

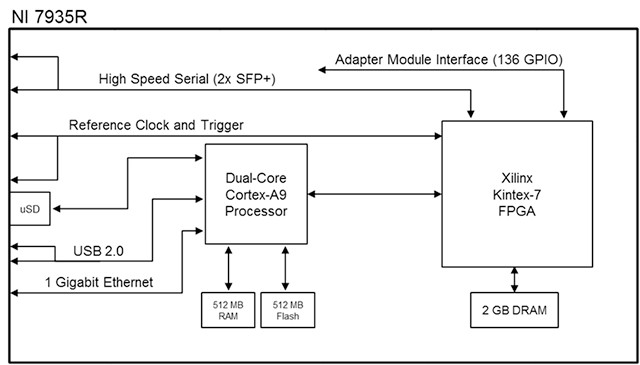

Figura 1: El controlador para FlexRIO es un dispositivo autónomo de adquisición de datos y procesamiento de señales con E/S de alto rendimiento y un FPGA Kintex-7 grande.

Arquitectura interna

El controlador para FlexRIO está desarrollado en base a un FPGA Kintex-7 grande que está conectado a una interfaz de E/S modular, un procesador y DRAM DDR3 de 2 GB. Con más de 400,000 segmentos de lógica, 1,540 segmentos de procesamiento digital de señales (DSP) y 28 Mb de BRAM, una cantidad importante de procesamiento de señales puede ser implementada en el FPGA. El procesador ARM dual-core ofrece conectividad USB y en red para conectar con otros dispositivos, así como almacenamiento interno para registro de datos y parámetros.

La combinación de un FPGA grande y un procesador de baja potencia es particularmente valioso cuando la mayoría de los algoritmos pueden ser implementados en el FPGA, lo cual deja al procesador ARM dual-core para la configuración y monitoreo del sistema de encendido. Esta arquitectura lleva la inteligencia cerca del límite, donde puede usarse un FPGA de alto rendimiento para convertir datos de alta velocidad en información importante.

Figura 2: Con un FPGA Kintex-7 grande, el controlador para FlexRIO es ideal para aplicaciones en las que los algoritmos de procesamiento de señales necesitan ejecutarse en tiempo real.

Si los datos de alto ancho de banda necesitan ser agregados a una ubicación local, los modelos NI 7932R y NI 7935R también tienen dos puertos seriales de alta velocidad para transferir datos directamente desde el FPGA usando protocolos de 10 Gigabit Ethernet UDP, Xilinx Aurora o personalizados.

Interfaz del módulo adaptador para FlexRIO

Figura 3: El NI 5772 es un módulo adaptador de digitalizador de alta velocidad de 2 canales, usado comúnmente en medidas en el dominio de frecuencia y dominio del tiempo.

Aprenda más sobre el kit de desarrollo de módulo para FlexRIO

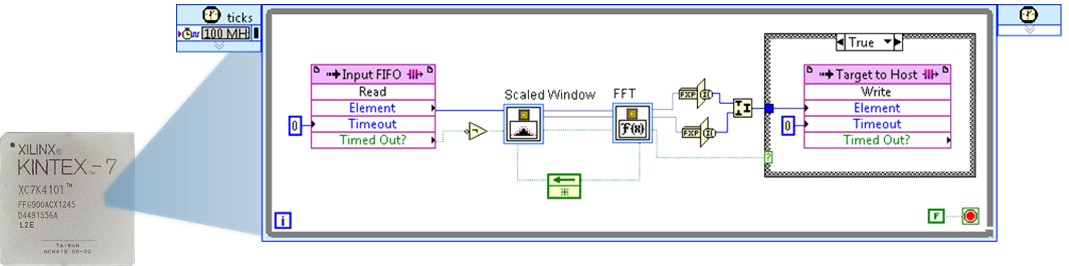

FPGA

Los usuarios programan el FPGA usando el software de desarrollo de sistemas LabVIEW con el módulo LabVIEW FPGA, permitiendo captura de algoritmos basada en LabVIEW e integración de VHDL/Verilog. Las bibliotecas existentes de LabVIEW pueden usarse para acelerar el desarrollo con infraestructura de movimiento de datos, funciones avanzadas de procesamiento de señales como un transformada rápida de Fourier (FFT) de banda ancha y algoritmos de re-muestreo paralelo y escritura DMA. Los diseños pueden ser simulados en LabVIEW antes de compilar localmente o a través del servicio de compilación en nube. Después de que el bitfile FPGA es compilado usando LabVIEW FPGA y Xilinx Vivado, los bitfiles son implementados a través de LabVIEW en la máquina de desarrollo; por aplicaciones en tiempo real, desarrolladas con LabVIEW o C/C++ que se ejecutan en el controlador o desde la memoria del dispositivo en el encendido. En muchos diseños de FlexRIO, la lógica es sincronizada a cientos de megahertz, donde puede ser más difícil cumplir con las restricciones de tiempo. NI recomienda que los desarrolladores de LabVIEW FPGA más nuevos comiencen revisando la guía para desarrolladores de LabVIEW FPGA de alto rendimiento para conocer las prácticas recomendadas para temporización y optimización de recursos.

Figura 4: LabVIEW simplifica la programación del FPGA al proporcionar un entorno de desarrollo gráfico e integrado para diseño, simulación, depuración e implementación.

Los ingenieros pueden elegir entre dos opciones de FPGA: un Xilinx Kintex-7 K325T y un K410T más grande. Para desarrollo inicial, usar el FPGA más grande disponible tiene ventajas importantes. No solamente brinda la flexibilidad de añadir características durante el desarrollo, sino también ofrece la habilidad de compilar el mismo código en un FPGA más grande, lo cual generalmente reduce los tiempos de compilación durante el diseño, haciendo la iteración lo más rápida posible. Con interfaces de E/S proporcionadas por NI, el código LabVIEW FPGA escrito por un dispositivo de hardware puede conectarse rápidamente a otro hardware de NI, incluso hardware con diferentes capacidades de E/S y FPGAs.

FPGA | Slices | LUTs | Flip Flops | Segmentos DSP | RAM en bloques (kb) | DRAM interna |

Kintex-7 K410T | 63,550 | 254,200 | 445,200 | 1,540 | 28,620 | 2 GB |

Kintex-7 K325T | 50,950 | 203,800 | 407,600 | 840 | 16,020 | 2 GB |

Figura 5. El Controlador para FlexRIO tiene dos diferentes FPGAs Xilinx, así los usuarios pueden elegir la parte correcta para la aplicación. NI recomienda usar el FPGA más grande para desarrollo inicial antes de intentar optimizar el diseño para desarrollo.

DRAM es un recurso que añade valor en algoritmos de procesamiento de señales en varias etapas y transferencia de datos entre buses no determinísticos. Para hacer posibles estos tipos de operaciones, las tres variantes del controlador para FlexRIO tienen un banco de 2 GB de DRAM DDR3 adjunto al FPGA. La interfaz DRAM tiene una amplitud de datos de 512 bits y se tiene acceso de manera eficiente a velocidades de reloj hasta 166 MHz, lo cual resulta en un ancho de banda teórico máximo de 10.6 GB/s entre la DRAM y el FPGA. El acceso aleatorio lee y escribe la disminución del rendimiento de DRAM, sin embargo, NI tiene lecturas y escrituras secuenciales arriba de 9 GB/s. DRAM se puede resolver usando LabVIEW Memory Item en LabVIEW FPGA o como un FIFO usando la Memory Instrument Design Library (IDL).

Aprenda a usar DRAM de manera efectiva.

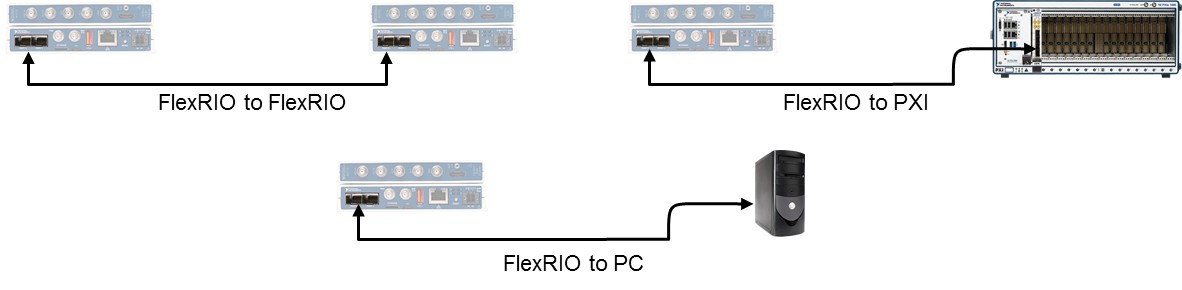

Serial de alta velocidad

Para aplicaciones que requieren escritura de datos de alto ancho de banda después de que las señales han sido adquiridas y procesadas, el NI 7932R y el NI 7935R están equipados con dos transceptores seriales de alta velocidad, cada uno puede transferir datos a hasta 10.3125 Gb/s. Esta tecnología depende de transceptores multi-gigabit (MGTs) Xilinx GTX que son enrutados desde el FPGA a dos conectores SFP+ en el panel frontal. NI proporciona proyectos ejemplo de LabVIEW FPGA para protocolos de 10 Gigabit Ethernet UDP y Xilinx Aurora. Los usuarios con experiencia con VHDL pueden implementar otros protocolos como Serial RapidIO o personalizados.

Ejemplos de configuraciones de escritura de datos que usan estos puertos seriales de alta velocidad incluyen compartir datos entre múltiples controladores usando Xilinx Aurora, escribir datos en PXI usando Aurora o 10 Gigabit Ethernet, y escribir datos a una PC de escritorio, registrador de datos, Network Area Storage (NAS) o servidor usando 10 Gigabit Ethernet.

Figura 6: Los puertos seriales de alta velocidad están diseñados para escritura de datos de alto ancho de banda a numerosos dispositivos. Los protocolos de comunicación son definidos en LabVIEW FPGA y cada transceptor puede ejecutarse a 10.3125 Gb/s.

Conozca más sobre la tecnología serial de alta velocidad en los productos de NI

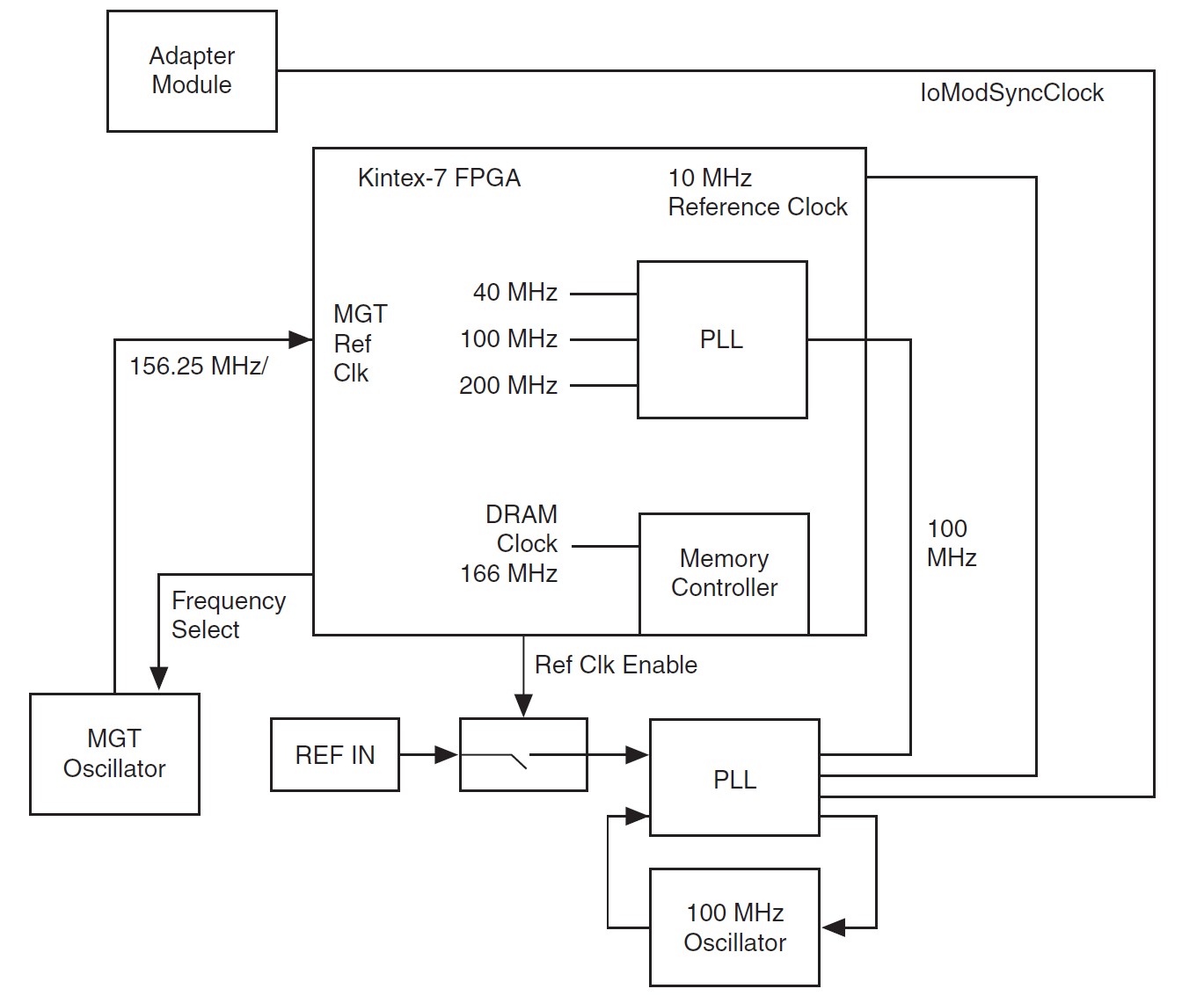

Sincronización

Los ingenieros que trabajan con FPGAs y E/S de alta velocidad por lo general pasan una buena cantidad de tiempo implementando la arquitectura adecuada para temporización y sincronización. Para simplificar este proceso, el Controlador para FlexRIO tiene una variedad de opciones para sincronización, incluyendo entrada de reloj de referencia de 10 MHz, una línea de disparo bidireccional, un oscilador interno de 100 MHz y la habilidad de fijar la frecuencia a una referencia externa. Para garantizar transferencia de datos sincrónicos entre el módulo de E/S y el FPGA, el reloj de muestreo del módulo de E/S se comparte con el circuito de sincronización del controlador para FlexRIO. También se pueden derivar relojes adicionales en el FPGA.

Figura 7: Con el circuito de sincronización en el controlador para FlexRIO, los usuarios pueden sincronizar múltiples dispositivos con precisión sub-muestreo.

Para sistemas distribuidos y estampa de tiempo, puede ser conectado un receptor GPS para suministrar un reloj de 10 MHz a la entrada de reloj de referencia y una entrada de 1 pulso por segundo al disparo SMA. Para requisitos menos estrictos, el dispositivo NI Linux Real-Time también soporta IEEE 1588 basado en software. Para sistemas en los que es posible la sincronización eléctrica, se puede usar una fuente de 10 MHz como el Ettus Octoclock para proporcionar un reloj de referencia compartido. En el caso en que varias unidades están agrupadas, vale la pena considerar las características avanzadas de temporización y sincronización de la plataforma PXI.

Procesador

El procesador dual-core ARM Cortex-A9 añade la flexibilidad y la conectividad necesarias para implementar el controlador para FlexRIO en el campo. Puede usarse para proporcionar datos a una red, ajustar los parámetros de configuración, registrar datos y mensajes o incluso actualizar el software y firmware de FPGA que se ejecutan en el dispositivo. El procesador ejecuta el SO NI Linux Real-Time, el cual ofrece mayor determinismo y fiabilidad, junto con los beneficios estándares del kernel de Linux. El sistema operativo en tiempo real (RTOS) es programable a través de LabVIEW con el LabVIEW Real-Time Module y también soporta el desarrollo C/C++ usando su entorno de desarrollo integrado (IDE) preferido. Las aplicaciones de programación y desarrollo de LabVIEW brindan acceso a los desarrolladores a bibliotecas pre-construidas para comunicación en red y archivos de E/S, lo cual simplifica enormemente el desarrollo.

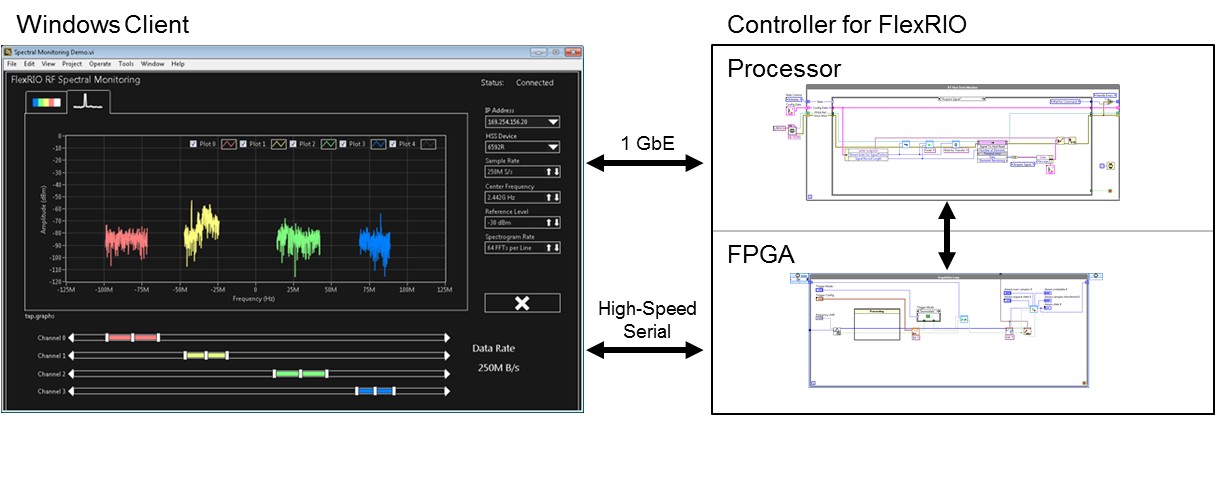

Para los usuarios familiarizados con FlexRIO, la principal diferencia al cambiar del FlexRIO en PXI al controlador para FlexRIO es que es añadida una capa de comunicación en red entre el FPGA y un cliente Windows tradicional. En lugar de seleccionar el FPGA directamente desde Windows, el código desarrollado para dispositivos NI Linux Real-Time se dirige al FPGA y el usuario es responsable de programar cualquier comunicación en red para monitoreo o configuración del sistema. En el NI 7932R y NI 7935R, los usuarios pueden aprovechar los dos puertos seriales de alta velocidad para escritura de datos directamente desde el FPGA a través de 10 Gigabit Ethernet UDP o Xilinx Aurora.

Figura 8: Un sistema implementado por lo general tiene tres capas de aplicación: firmware que se ejecuta en FPGA, código LabVIEW o C/C++ que se ejecuta en el host Linux Real-Time y una aplicación de cliente para configuración remota, monitoreo o registro de datos.

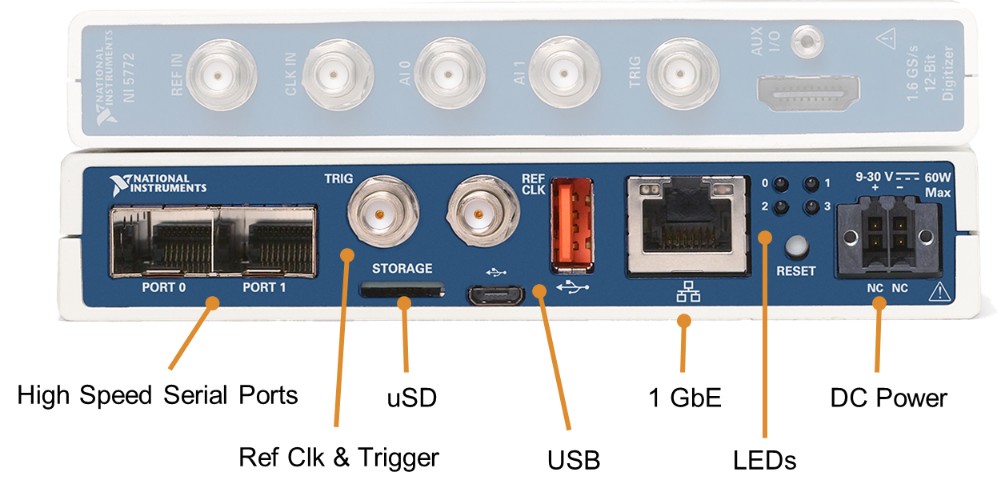

El procesador también tiene acceso a 512 MB de memoria y 512 MB de su propio RAM, junto con una interfaz 1 Gigabit Ethernet, interfaces de servidor y dispositivo USB 2.0 y una ranura de tarjeta µSD. La interfaz principal para aplicaciones implementadas debe ser 1 Gigabit Ethernet porque soporta sustancialmente más ancho de banda; sin embargo el puerto USB del dispositivo puede ser usado para instalación, configuración y diagnóstico.

Conectividad

Toda la conectividad es expuesta en una sola cara del hardware para hacer que el dispositivo sea más fácil de integrar en sistemas más grandes. Aunque la E/S es modular, los módulos adaptadores analógicos también proporcionan al FPGA con E/S a través de un conector de E/S auxiliar. El controlador acepta potencia DC entre 9 volts y 30 volts, lo cual significa que puede ser alimentado con baterías para sistemas portátiles.

Figura 9: Aparte de la conectividad que proporcionan los módulos adaptadores FlexRIO, el controlador para FlexRIO tiene interfaces estándares en la industria para escritura de datos, los conectores SMA para temporización y sincronización, los puertos USB para comunicación con periféricos y LEDs para indicador LED de estado visual.

Todos los conectores tienen medidas para retención de cable con la excepción de los dos puertos USB. El puerto principal USB (color naranja) está especialmente diseñado para alta retención, mientras que el puerto de dispositivo USB está hecho para ser utilizado principalmente para diagnósticos.

Empaque físico

La cubierta de aluminio del dispositivo elimina la necesidad de diseñar mecánica personalizada y está diseñada para ser fácil de integrar al proporcionar rendimiento consistente, analógico y térmico en una variedad de escenarios. Con el kit de montaje, la unidad también puede ser montada en panel de manera segura.

Figura 10: El controlador para FlexRIO está empaquetado para aplicaciones embebidas en las que el tamaño, el peso y la potencia están limitados.

El paquete también incluye varias características para garantizar fiabilidad y funcionabilidad a largo plazo. Primero, los desarrolladores tienen acceso a ganchos del software para monitorear temperaturas del procesador y FPGA. En el caso de que la temperatura del procesador o FPGA exceda los límites de seguridad, el dispositivo se apaga automáticamente para evitar daños a los componentes internos. El enfriamiento activo se proporciona con un ventilador reparable por el usuario y que puede ser monitoreado en software y ajustado automáticamente con la temperatura del dispositivo. A 40 °C, el tiempo medio entre fallas (MTBF) del ventilador es de más de siete años.

Para escenarios en los que el impacto, la vibración, la temperatura o la humedad son una preocupación, el controlador para FlexRIO se clasifica de manera similar a PXI, soportando impacto senoidal medio de 30 g, vibración de 0.3 grms entre 5 Hz y 500 Hz, temperaturas ambiente de 0 °C a 55 °C y 5% a 95% de humedad sin condensación.

Resumen

La habilidad de generar prototipos rápidamente de algoritmos que se ejecutan en tiempo real, ha sido una ventaja que NI ha proporcionado por más de una década con la arquitectura de E/S reconfigurable (RIO) y LabVIEW FPGA. Para ingenieros y científicos que generan prototipos de nuevas tecnologías en áreas como radar, monitoreo de espectro, comunicaciones, maquinaria industrial, ultrasonido e imágenes médicas, esta plataforma hace posible la generación de prototipos más rápida con máxima reutilización de código durante la producción o implementación.

Pasos siguientes

- Aprenda más sobre FlexRIO

- Compre módulos adaptadores FlexRIO

- Vea las variantes del controlador para FlexRIO

La marca comercial registrada Linux® se utiliza conforme a una sublicencia otorgada por LMI, el licenciatario exclusivo de Linus Torvalds, propietario de la marca en todo el mundo.