Una introducción a los instrumentos seriales PXI de alta velocidad PXI

Información general

Instrumentos seriales PXI de alta velocidad ayudan a los ingenieros a validar, conectar y probar protocolos seriales de alta velocidad. Los dispositivos seriales de alta velocidad seleccionados, como el PXIe-7903 y el PXIe-7902, fueron diseñados para ingenieros que necesitan capacidades de co-procesamiento FPGA de alto rendimiento para lograr un movimiento de datos de alto volumen y procesamiento de señales en línea en tiempo real. Este hardware tiene un FPGA Xilinx Kintex™ UltraScale+™ o serie 7, que usted puede programar con el LabVIEW FPGA Module para una máxima personalización y reutilización específicas de la aplicación. Estos instrumentos aprovechan los transceptores multigigabit (MGT) FPGA para soportar velocidades de línea de hasta 28.2 Gbps y hasta 48 líneas TX y RX. Como parte de la plataforma PXI, se benefician de las capacidades de sincronización, disparo y movimiento de datos de alta velocidad de PXI, incluyendo la transmisión hacia y desde el disco, así como la transmisión peer-to-peer (P2P) a velocidades de hasta 7 GB/s .

Contenido

- El surgimiento de las interfaces seriales de alta velocidad

- Módulos seriales de alta velocidad

- Aplicaciones de ejemplo

- Habilidades requeridas

- Pasos siguientes

El surgimiento de las interfaces seriales de alta velocidad

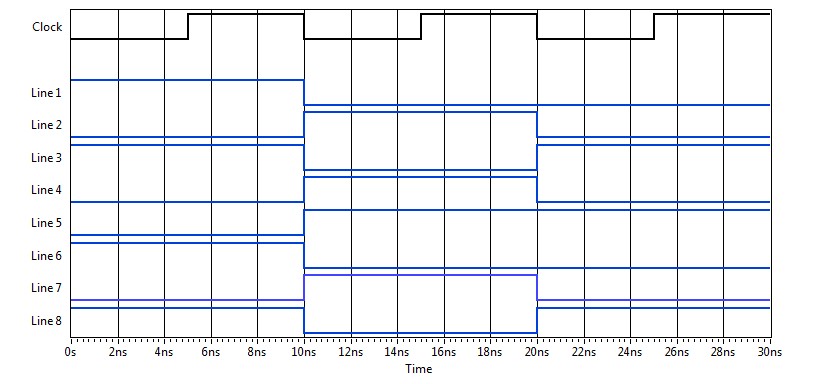

Con la creciente demanda de un mayor ancho de banda de datos, las interfaces cableadas han aumentado sus velocidades de reloj y paralelismo para mantenerse al día. Sin embargo, con los buses de datos paralelos tradicionales, la menor cantidad de desfase entre el reloj y las líneas de datos puede amenazar la razón de error de bits de la interfaz. Los enlaces de datos seriales ofrecen una solución a este problema al incorporar el reloj en el flujo de datos de un par determinado de trazas diferenciales, lo que elimina la posibilidad de desfase entre el reloj y los datos. Esta característica requiere electrónica adicional en el extremo receptor de la interfaz, así como codificación adicional para la recuperación del reloj; sin embargo, permite velocidades de datos dramáticamente más altas, lo que satisface la demanda de ancho de banda.

Figura 1. Reloj paralelo (negro) y datos (azul) versus reloj embebido en datos (rojo), con ancho de banda de datos equivalente.

Los protocolos modernos de comunicación de datos han pasado de estas interfaces paralelas a interfaces seriales de alta velocidad, como los estándares de video PCI Express, HDMI y DisplayPort, IEEE 1394b, USB 3.0 y más. Para los ingenieros de diseño y pruebas, validar estas interfaces representa nuevos desafíos que requieren nuevo hardware de pruebas. Tradicionalmente, los ingenieros han utilizado osciloscopios costosos o probadores de razón de error de bits (BERT) para caracterizar las interfaces físicas y han utilizado analizadores y generadores específicos del protocolo para validar que la pila de protocolos se implementa correctamente y que la transmisión y recepción de datos funcionan de manera eficiente. Sin embargo, para pruebas automatizadas de V&V y fabricación, no existe hardware optimizado para probar estas interfaces seriales. Los osciloscopios y los probadores de razón de error de bits a menudo son demasiado costosos y lentos para justificar la cobertura que brindan, mientras que el hardware específico del protocolo a menudo no es lo suficientemente flexible como para integrarse en sistemas de pruebas automatizadas. El hardware específico del protocolo, por otro lado, no se puede reutilizar para otras pruebas o reutilizar para otros dispositivos bajo prueba (DUT).

Los FPGAs proporcionan una solución para estos desafíos. Los FPGAs modernos y de alto rendimiento generalmente incluyen varios MGTs que funcionan con una variedad de interfaces seriales de alta velocidad. Cuando se combina con la IP específica del protocolo apropiado, la programación gráfica a través del LabVIEW FPGA Module y las ventajas del ecosistema PXI, surge un nuevo instrumento serial de alta velocidad diseñado por software.

Módulos seriales de alta velocidad

|  |  |  |  |  | |

| Especificación | PXIe-6591 | PXIe-6592 | PXIe-6593 | PXIe-6594 | PXIe-7902 | PXIe-79032 |

| Velocidad de línea | 500 Mbps–12.5 Gbps¹ | 500 Mbps–10.3125 Gbps¹ | 500 Mbps–16.3 Gbps | 500 Mbps–28.2 Gbps | 500 Mbps–12.5 Gbps | 500 Mbps–28.2 Gbps |

| Canales | 8 TX/RX | 4 TX/RX | 8 TX/RX | 8 TX/RX | 24 TX/RX | 48 TX/RX |

| FPGA | Kintex 7 K410T | Kintex 7 K410T | Kintex UltraScale KU040, KU060 | Kintex UltraScale+ KU15P | Virtex™ 7 485T | Virtex UltraScale+ XCVU11P |

| DRAM | 2 GB | 2 GB | 4 GB | 8 GB | 2 GB | 20 GB |

| Hostancho de banda de transmisión | 3.2 GB/seg | 3.2 GB/seg | 7 GB/seg | 7 GB/seg | 3.2 GB/seg | 7 GB/seg |

| Connector | Mini-SAS HD | SFP+ | QSFP28 | QSFP28 | Mini-SAS HD | Mini-SAS HD |

| Opciones de cableado | Cobre u óptico | Cobre u óptico | Cobre u óptico | Cobre u óptico | Cobre u óptico | Cobre u óptico |

| Aux DIO | 20 SE | 4 SE | 8 GPIO | 8 GPIO | N/A | 8 GPIO |

Tabla 1. Instrumentos PXI seriales de alta velocidad.

¹Brecha en las velocidades de línea alcanzables entre 8 Gbps y 9.8 Gbps.

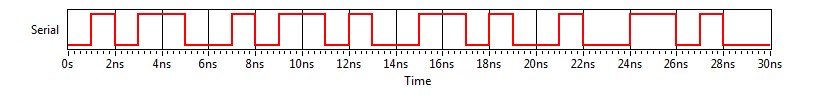

²El PXIe-7903 es un módulo de 2 ranuras.

La conectividad y el cableado son fundamentales con aplicaciones que tienen altas velocidades de datos y anchos de banda analógicos que superan los 20 GHz. El PXIe-7903, PXIe-7902, PXIe-6594, PXIe-6593, PXIe-6592 y PXIe-6591 proporcionan distintas opciones para simplificar la conectividad para casos de uso específicos. Los tres módulos cuentan con un FPGA Xilinx programable por el usuario en su núcleo.

Los transceptores Xilinx Serie 7 GTX son la tecnología clave detrás de estos instrumentos. Utilizan lógica de modo de corriente (CML), que es una interfaz diferencial que presenta una pequeña oscilación de señal de 800 mVpp (nominalmente, 1,000 mVpp máximo) para reducir el consumo de energía y las emisiones radiadas, y una impedancia diferencial de 100 ohm (50 ohm por rama de señal ) para minimizar los reflejos y las aberraciones de señal resultantes a altas velocidades de datos. Además, para una fidelidad de señal óptima, estos transceptores incluyen una amplitud de transmisión programable para compensar cables largos, así como transmisión de pre y post-énfasis y ecualización del receptor auto-adaptable para superar el ancho de banda limitado del cable/canal analógico.

Todas las interfaces seriales de alta velocidad requieren un reloj de referencia que opere a un divisor entero de la velocidad de línea. Para una máxima flexibilidad, los transceptores GTX incluyen un ciclo de sincronización de fase (PLL) que puede multiplicar el reloj de referencia hasta 100 veces para producir la velocidad de datos seriales. También incluyen convertidores serial a paralelo y paralelo a serial con relaciones de hasta 80X, lo que limita las frecuencias de reloj FPGA y permite altas velocidades de datos seriales. Además, los transceptores tienen estructuras de codificación y decodificación 8b/10b, 64b/66b y 64b/67b integradas para garantizar un número suficiente de transiciones de señal para la recuperación del reloj y para evitar consumir recursos FPGA de uso general. La guía del usuario de transceptores FPGAs GTX/GTH de la Serie Xilinx 7 proporciona más detalles sobre los transceptores Xilinx GTX.

Además de proporcionar transceptores seriales de alta velocidad, los FPGAs Xilinx en los instrumentos sirven para otros propósitos vitales. Implementan la lógica para el protocolo en uso, así como cualquier lógica de usuario específica de la aplicación para la configuración del hardware y la generación, recepción y movimiento de los datos en todo el sistema.

Figura 2. PXIe-7903 arquitectura de hardware con interfaces clave y velocidad de datos

| Especificación | FPGA | LUTs | Segmentos DSP | RAM de bloque embebida |

| PXIe-6591 | Kintex-7 K410T | 254,200 | 1,540 | 28 Mb |

| PXIe-6592 | Kintex-7 K410T | 254,200 | 1,540 | 28 Mb |

| PXIe-6593 | Kintex UltraScale KU040 | 242,400 | 1,920 | 21.1 Mb |

| Kintex UltraScale KU060 | 331,680 | 2,760 | 38 Mb | |

| PXIe-6594 | Kintex UltraScale+ KU15P | 523,000 | 1,968 | 34.6 Mb |

| PXIe-7902 | Virtex-7 485T | 303,600 | 2,800 | 37 Mb |

| PXIe-7903 | Virtex UltraScale+ XCVU11P | 2,835,000 | 9,216 | 341 Mb |

Tabla 2. Instrumentos seriales PXI de alta velocidad y sus respectivas especificaciones de FPGA.

Directamente conectados a los FPGAs hay hasta 20 GB de DRAM DDR3 interna que se puede leer o escribir a velocidades de hasta 25 GB/s (máximo teórico) en patrones de acceso definidos por el usuario. El FPGA también incluye una interfaz PCI Express x8 Gen 3 al plano trasero PXI Express para transferencia de datos hacia y desde el host y el disco, o P2P a otros dispositivos habilitados para FPGA en el sistema a velocidades unidireccionales de hasta 7 GB/s y velocidades bidireccionales de hasta 7 GB/s. a 2.4 GB/s en cada dirección (4.8 GB/s agregado).

Un reloj de referencia de alta fidelidad y baja fluctuación es un componente crítico de cualquier sistema de comunicaciones seriales de alta velocidad. Todos los módulos tienen un sintetizador interno de cualquier velocidad para operación MGT en el rango completo de los transceptores Xilinx GTX, con el PXIe-6591, PXIe-6592 y PXIe-7902 operando desde 500 Mbps a 8 Gbps y 9.8 Gbps a su máxima velocidad de dispositivo, mientras que el PXIe-6593, PXIe-6594 y PXIe-7903 opera sin esa brecha entre sus velocidades de línea mínimas y máximas. El PXIe-6591, PXIe-6592, PXIe-6593 y PXIe-6594 cuentan con conectividad coaxial en el panel frontal para exportar el reloj de referencia integrado, y los cuatro módulos tienen conectividad para importar un reloj de referencia externo. Finalmente, los dispositivos pueden enrutar los relojes del plano trasero PXI Express de 100 MHz o DStarA como referencia para los MGT.

Software

Un instrumento diseñado por software proporciona la misma funcionalidad que un instrumento de función fija, pero los usuarios pueden personalizar el hardware de instrumentación a través de un FPGA abierto y programable por el usuario. Este nivel de personalización es necesario en un instrumento serial de alta velocidad PXI para soportar una variedad de protocolos y aplicaciones. Como tal, no existe una sola API de alto nivel para programar estos dispositivos. En cambio, se programan directamente en el software LabVIEW para el código host (CPU) y FPGA, interactuando entre los dos con la API NI-RIO de nivel inferior. Para ayudar a los usuarios a ponerse en marcha rápidamente, una multitud de ejemplos demuestran el uso de diferentes protocolos, así como diferentes modelos de uso para estos instrumentos.

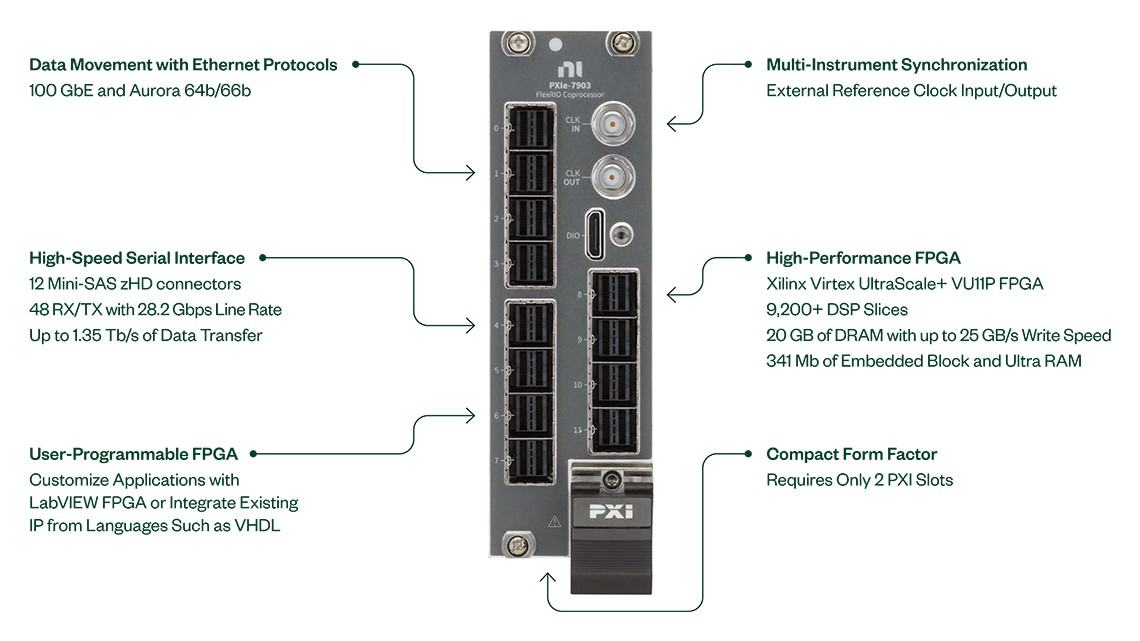

El FPGA abierto proporciona un grado de personalización que no se encuentra en otros instrumentos. En primer lugar, implementa el protocolo serial para el cual está configurado el instrumento. Esto por sí solo hace posible que el PXIe-7903, PXIe-7902, PXIe-6594, PXIe-6593, PXIe-6592 y PXIe-6591 soporten una multitud de protocolos seriales estándares e incluso personalizados. Más allá del protocolo, la funcionalidad de hardware definida por el usuario permite tipos de pruebas que antes no eran posibles. Por ejemplo, la generación de datos algorítmicos en el FPGA reduce la memoria de almacenamiento de forma de onda y el ancho de banda del sistema requeridos para descargar estas formas de onda, lo que acelera el rendimiento de la prueba. Los análisis de datos algorítmicos, como la comparación de respuestas, el disparo inteligente y la reducción y compresión de datos, reducen drásticamente la cantidad de datos que debe procesar la CPU principal, lo que también disminuye el tiempo de prueba.

El acceso a DRAM definido por el usuario permite flexibilidad en cómo se divide la DRAM en regiones de estímulo y respuesta. También permite algoritmos personalizados de compresión y descompresión, lo que permite un uso óptimo del tamaño y el ancho de banda de DRAM. La captura y reproducción de forma de onda estándar es ciertamente posible, pero dependiendo del protocolo, la velocidad de línea y el número de líneas, el ancho de banda de E/S puede exceder el ancho de banda de DRAM. Finalmente, el movimiento de datos definido por el usuario hacia y desde un instrumento serial de alta velocidad y el host u otros instrumentos brinda una flexibilidad significativa para la integración a nivel del sistema. Por ejemplo, es posible convertir datos analógicos en muestreos digitales con un digitalizador de alta velocidad, usar transmisión NI P2P para transferir esos datos a un instrumento serial de alta velocidad a velocidades de hasta 7 GB/s, y luego transmitir esos muestreos digitales a un dispositivo externo a través de un protocolo serial. Alternativamente, un instrumento serial de alta velocidad puede capturar un flujo de datos seriales y transferirlo a la CPU host y a un arreglo RAID de alto ancho de banda durante horas o incluso días de almacenamiento continuo, nuevamente a velocidades de hasta 7 GB/s.

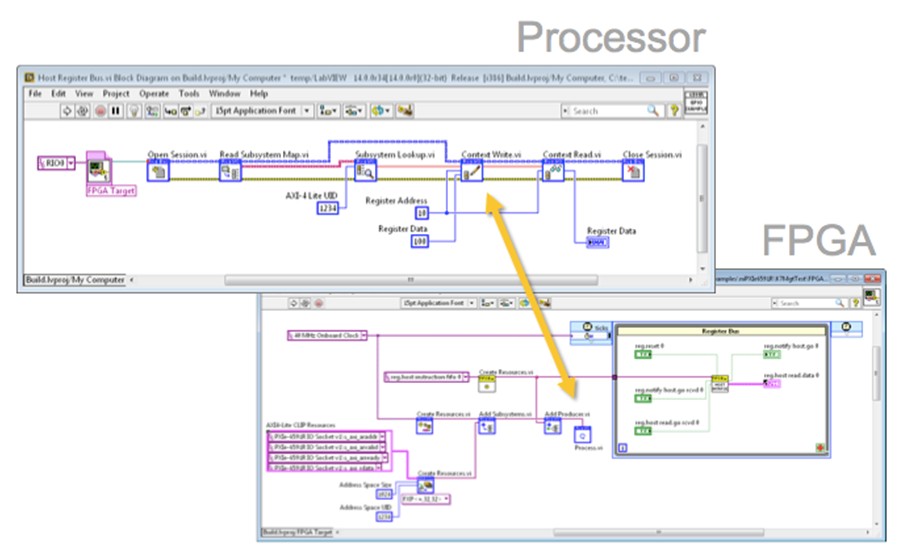

LabVIEW FPGA simplifica la configuración y la programación de estos instrumentos seriales de alta velocidad. La Figura 3 resalta las interfaces clave accesibles a través de LabVIEW, junto con el código representativo. LabVIEW FPGA y la API de NI-RIO proporcionan mecanismos eficientes para la transferencia de datos basada en PCI Express entre la CPU principal y el FPGA, incluyendo lecturas y escrituras de registros, así como transferencias DMA bidireccionales. El acceso a DRAM, generalmente una interfaz difícil de administrar en lenguajes de descripción de hardware (HDL) de nivel inferior, se simplifica a través de interfaces de solicitud, lectura y escritura abstraídas, manteniendo un alto rendimiento y proporcionando arbitraje básico de lectura/escritura. La configuración del transceptor GTX generalmente es específica del protocolo, y la IP ya existe para muchas interfaces seriales de alta velocidad (ya sea HDL o netlist) con configuración de transceptor integrada. Esta interfaz de protocolo serial está expuesta en LabVIEW FPGA a través de una interfaz IP a nivel de componente (CLIP). Los nodos CLIP permiten la operación asincrónica de código no implementado en LabVIEW, pero tienen una interfaz bien definida para el diagrama LabVIEW FPGA. Un escenario común utiliza IP específica del protocolo Xilinx (incluyendo la configuración del transceptor) del catálogo de IP de Xilinx Vivado y una capa delgada de VHDL para definir la interfaz para LabVIEW FPGA. Una vez que se implementa el protocolo, LabVIEW FPGA ofrece un lenguaje enriquecido para implementar lógica de usuario arbitraria, como toma de decisiones, implementación de la máquina de estado, control del DUT, procesamiento de señales y movimiento de datos.

Figura 3. LabVIEW FPGA proporciona acceso gráfico a aspectos clave del FPGA programable por el usuario en instrumentos seriales de alta velocidad PXI.

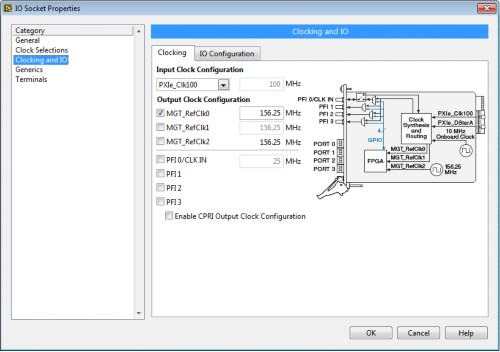

Más allá de definir la lógica que se implementará en el FPGA programable por el usuario, LabVIEW simplifica la configuración del hardware a través de su jerarquía de proyectos y las páginas de configuración asociadas. Por ejemplo, la configuración del reloj de referencia en estos instrumentos seriales de alta velocidad requiere un algoritmo complejo para determinar cientos de configuraciones de registro que se aplicarán a hasta cuatro circuitos integrados separados, además de la lógica requerida para aplicar estos registros cuando el FPGA se enciende. LabVIEW FPGA expone esto como un cuadro de diálogo con una representación gráfica de las opciones, junto con reglas de diseño y orientación para aplicar configuraciones válidas. Este enfoque simplifica la configuración del sintetizador de reloj de cualquier velocidad y los circuitos de enrutado a una tarea que lleva minutos en lugar de horas o días.

Figura 4. LabVIEW FPGA ofrece una interfaz gráfica e intuitiva para la configuración del reloj que simplifica un proceso complejo.

Para permitir la reutilización del código y simplificar las tareas comunes, los instrumentos seriales PXI de alta velocidad soportan ciertas bibliotecas de diseño de instrumentos, que son bibliotecas de código host y FPGA con interfaces de LabVIEW diseñadas para funcionar entre sí y proporcionar capacidades genéricas. El framework de instrucciones es una biblioteca de diseño de instrumentos para la configuración dinámica de hardware durante el tiempo de ejecución. Aunque la mayoría de la funcionalidad de hardware de estos instrumentos seriales (por ejemplo, la configuración del reloj) se puede configurar de forma estática en el proyecto de LabVIEW , los usuarios pueden aprovechar el framework de instrucciones para controlar los parámetros del firmware específicos de la aplicación. Por ejemplo, el framework de instrucciones simplifica la configuración del host de los ajustes de registro expuestos a través de las interfaces AXI-4 Lite en el FPGA, que comúnmente se encuentran en la IP del protocolo serial Xilinx.

Figura 5. Procesador y código FPGA para escribir y leer registros a través de una interfaz AXI-4 Lite.

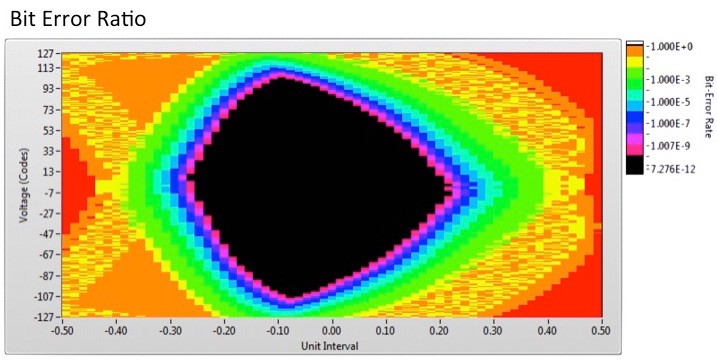

Construida sobre el framework de instrucciones, la biblioteca de diseño de instrumentos Eye Scan proporciona capacidades de depuración para los canales de recepción serial de alta velocidad. Los transceptores Xilinx GTX cuentan con dos comparadores de receptor por canal. Mientras que un comparador rastrea automáticamente el centro del ojo serial en función de la frecuencia y la fase del reloj recuperada, el otro comparador puede cambiar de forma independiente en amplitud y fase. Al variar los parámetros del último comparador y al comparar los resultados con los del primero, la biblioteca de diseño de instrumentos Eye Scan puede crear un diagrama de ojo estadístico y útil para determinar el margen del enlace de la interfaz, con precisión para el piso de la razón de error de bits de los transceptores Xilinx GTX. Además, debido a que la biblioteca de diseño de instrumentos Eye Scan utiliza un conjunto independiente de recursos de hardware, puede coexistir con otro protocolo IP y ejecutarse simultáneamente con otra funcionalidad específica de la aplicación.

Figura 6. Las bibliotecas de diseño de instrumentos de LabVIEW para instrumentos seriales PXI de alta velocidad incluyen un diseño de referencia para realizar escaneo visual estadístico usando una configuración de loopback.

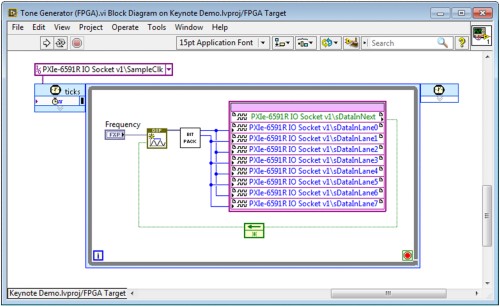

Más allá de estas bibliotecas de diseño de instrumentos, otros instrumentos diseñados por software de NI proporcionan bibliotecas para una variedad de funciones útiles, como multi-registro, así como adquisición y generación basadas en DRAM. Aunque no son compatibles ni probados oficialmente en PXIe-7903, PXIe-7902, PXIe-6594, PXIe-6593, PXIe-6592 y PXIe-6591, dependiendo del agnosticismo del hardware de la biblioteca de diseño de instrumentos, se pueden usar con instrumentos seriales PXI de alta velocidad también.

Figura 7. Los ingenieros pueden usar la biblioteca de diseño de instrumentos DSP para sintetizar una sinusoidal para una transmisión a un convertidor digital a analógico a través del protocolo serial JESD204B.

Protocolos

Los transceptores Xilinx GTX en los instrumentos seriales PXI de alta velocidad soportan una amplia variedad de protocolos. NI proporciona una serie de ejemplos de software para demostrar cómo integrar protocolos comunes, así como arquitecturas de LabVIEW para varios patrones de aplicación. Cada ejemplo viene con un archivo de bits FPGA pre-compilado para el instrumento compatible, junto con el código fuente asociado y la IP del protocolo. Si este código requiere modificación para la aplicación final, ciertos protocolos requieren una licencia de IP de Xilinx para recompilar el FPGA. Este protocolo IP está disponible para compra a través de Xilinx o revendedores como Avnet o DigiKey.

Xilinx Aurora

Xilinx Aurora proporciona un protocolo ligero, de baja latencia y de tamaño reducido, diseñado para interfaces seriales punto a punto. Soporta la velocidad completa de los transceptores seriales Xilinx GTX, así como la unión de carriles para un ancho de banda aún mayor. Diseñada principalmente para el movimiento de datos de alto ancho de banda, Aurora proporciona control de flujo, marcos flexibles y opciones para canales simplex o full-duplex. Puede encontrar más información sobre Xilinx Aurora en los siguientes enlaces:

http://www.xilinx.com/products/design_resources/conn_central/grouping/aurora.htm

El controlador para bibliotecas de diseño de instrumentos para instrumentos seriales de alta velocidad instala un diseño de referencia de proyecto de ejemplo para Aurora 64b66b, y NI tiene un ejemplo web para Aurora 8b10b.

JESD204B y JESD204C

A medida que aumentan las velocidades de muestreo y las resoluciones del convertidor analógico a digital (ADC) y del convertidor digital a analógico (DAC) para satisfacer las demandas de las transmisiones digitales moduladas de banda ancha inalámbrica, han aumentado las velocidades de datos hacia y desde estos convertidores. Con las interfaces de datos y reloj paralelo tradicionales, esto requiere más pines de circuito integrado con tolerancias más estrictas. JESD204B y JESD204C enfrentan este desafío al hacer la transición de estas interfaces a seriales de alta velocidad, que está diseñado para proporcionar un alto ancho de banda de datos con baja latencia y para facilitar la sincronización de múltiples convertidores. JESD204B soporta hasta 12.5 Gbps y 32 líneas para los últimos ADCs y DACs de alto ancho de banda, alta velocidad y gran cantidad de canales. Mientras que JESD204C soporta velocidades de hasta 32 Gbps. JESD204B usa codificación 8B/10B mientras que JESD204C soporta 8B/10B, 64B/66B y 64B/80B.

10 Gigabit Ethernet

Con una velocidad de línea de 10.3125 Gbps, 10 Gigabit Ethernet (10 GbE) proporciona un ancho de banda práctico de aproximadamente 1 GB/s. La mayoría de las interfaces 10 Gigabit Ethernet son ópticas o de conexión directa SFP+ (cobre), con interfaces basadas en 8P8C/RJ45. El ejemplo de 10 Gigabit Ethernet para el PXIe-6592 soporta interfaces ópticas 10GBASE-SR, LR y ER, así como conexión directa SFP+, utilizando el núcleo IP Xilinx 10 Gigabit Ethernet PCS/PMA y el controlador de acceso a medios 10 Gigabit Ethernet de OpenCores.org. Una pila UDP ligera implementada en LabVIEW FPGA se basa en esta solución MAC/PHY. Puede encontrar más información sobre los núcleos IP de 10 Gigabit Ethernet en los siguientes enlaces:

https://www.xilinx.com/products/intellectual-property/10gbase-r.html

El controlador para bibliotecas de diseño de instrumentos para instrumentos seriales de alta velocidad instala un diseño de referencia de proyecto de ejemplo para 1 GbE y 10 GbE.

100 Gigabit Ethernet

100 Gigabit Ethernet (100GbE) puede transmitir marcos Ethernet a una velocidad de 100 gigabits por segundo (Gbit/s), una velocidad significativamente mayor que 10 Gigabit Ethernet. 100 GbE ofrece diferentes interfaces ópticas y eléctricas y diferentes números de hilos de fibra óptica. Algunas de las interfaces clave incluyen 100GBASE-KR2, 100GBASE-CR2 y QSFP28.

LabVIEW FPGA incluye un ejemplo para 100 GbE.

CPRI

CPRI define la interfaz óptica entre el control de equipos de radio (REC) y el equipo de radio (RE) comúnmente conocido como cabezales de radio remotos (RRH). Facilita la configuración y sincronización del cabezal de radio, así como la transmisión de datos digitales I/Q (banda base). Puede encontrar más información sobre el núcleo IP CPRI de Xilinx en el siguiente enlace:

https://www.xilinx.com/products/intellectual-property/do-di-cpri.html

Serial RapidIO

Serial RapidIO es un protocolo de interconexión serial de alto rendimiento optimizado para sistemas embebidos de bajo consumo, como infraestructura de telecomunicaciones, cómputo embebido militar y aeroespacial, dispositivos de ciencias biológicas de alto ancho de banda y control industrial. Cuenta con velocidades de hasta 6.25 Gbps, enlace de cuatro líneas, baja latencia, control de flujo, entrega de paquetes en orden y un tamaño relativamente pequeño. Puede encontrar más información sobre el núcleo IP Serial RapidIO de Xilinx en el siguiente enlace:

http://www.xilinx.com/products/intellectual-property/ef-di-srio.html

Un diseño de referencia de Serial RapidIO para el PXIe-6592 está disponible en la Comunidad de NI. Para interfaces SRIO más grandes que x2, NI recomienda el PXIe-6591.

Protocolos adicionales

Los ejemplos anteriores no son una lista exhaustiva de todos los protocolos que son compatibles con los instrumentos seriales PXI de alta velocidad. Los ingenieros de ventas locales de NI pueden responder preguntas sobre protocolos específicos, personalizar los ejemplos anteriores o sobre la integración de protocolos personalizados o patentados.

Aplicaciones de ejemplo

La arquitectura flexible de los instrumentos seriales PXI de alta velocidad les brinda la capacidad de soportar una variedad de casos de uso, cada uno con diferentes patrones de movimiento de datos, protocolos seriales y capacidades de software.

Prueba funcional del protocolo

Un caso de uso común para los instrumentos seriales PXI de alta velocidad es realizar pruebas funcionales específicas del protocolo en un DUT determinado. Estas pruebas están diseñadas para confirmar que el DUT puede comunicarse de manera confiable con el "mundo exterior" a través de un protocolo serial. Dichas pruebas pueden escribir y leer registros en el DUT, realizar pruebas de rendimiento de datos y latencia, o ejercitar otros atributos específicos del protocolo o modos de prueba integrados. También pueden probar cómo responde el DUT a escenarios de fallas, como tiempos de espera de respuesta, errores inyectados o comandos de control de flujo ignorados. Las tareas relacionadas incluyen medidas de razón de error de bits de enlace, pruebas de esfuerzo de la capa física, como velocidades de línea máximas y mínimas, pruebas de funcionamiento e incluso vigilancia del bus, en las que el instrumento realiza análisis, disparos personalizados y captura de datos en el FPGA.

Control, estímulo y respuesta del DUT

Otro caso de uso común para los instrumentos seriales PXI de alta velocidad es el control del DUT, el estímulo y la captura de respuesta. En este escenario, el instrumento no necesariamente está probando el protocolo serial de alta velocidad directamente, sino que envía o recibe datos del DUT utilizando un protocolo serial de alta velocidad, para que se puedan probar otros aspectos del dispositivo. Además, la E/S digital auxiliar se puede utilizar para controlar el DUT utilizando protocolos paralelos o seriales de baja velocidad, como SPI.

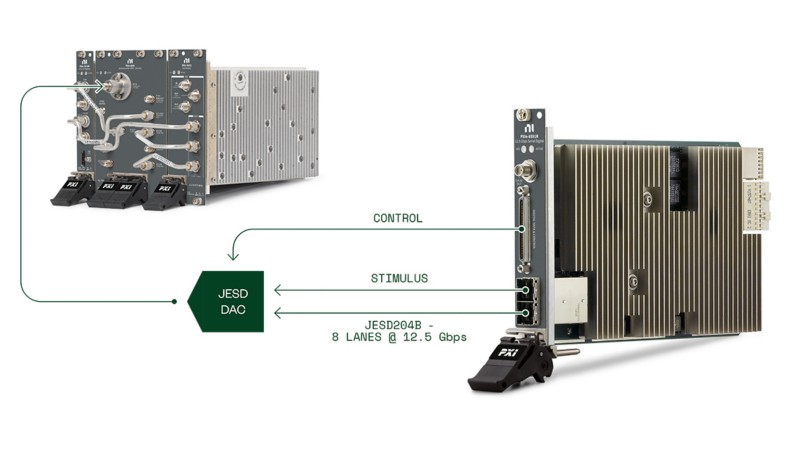

En el siguiente ejemplo, un PXIe-6591 estimula un DAC utilizando el protocolo JESD204B para probar las características de salida analógica del DAC.

Figura 8. Muchos DACs y ADCs modernos de alto rendimiento incluyen comunicación utilizando el protocolo serial de alta velocidad JESD204B.

Movimiento de datos de alto ancho de banda

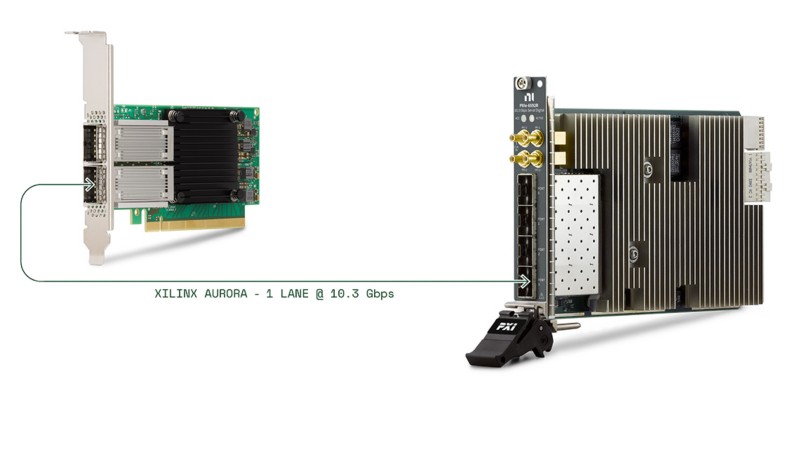

Muchas aplicaciones embebidas de alto rendimiento pueden beneficiarse de la plataforma PXI y requieren movimiento de datos de alto ancho de banda y baja latencia hacia y desde hardware de terceros y dispositivos NI PXI. Para estas aplicaciones, los instrumentos seriales PXI de alta velocidad ofrecen beneficios como procesamiento de hardware LabVIEW FPGA, transmisión de datos P2P a instrumentos PXI Express y transmisión de alto ancho de banda hacia y desde el disco y proporcionan conectividad de alto ancho de banda a dispositivos externos a través de un estándar serial de alta velocidad.

En el siguiente ejemplo, un osciloscopio de NI muestrea una señal analógica y luego envía los datos digitalizados sin procesar a un instrumento serial de alta velocidad PXIe-6592 utilizando la transmisión de datos P2P. Luego, el instrumento procesa los datos en tiempo real utilizando un algoritmo implementado en LabVIEW FPGA. Finalmente transmite los datos procesados a un dispositivo de terceros utilizando el protocolo ligero Xilinx Aurora, que está diseñado para la comunicación serial de FPGA a FPGA.

Figura 9. Los instrumentos seriales PXI de alta velocidad son una excelente solución para el movimiento de datos de alto ancho de banda y baja latencia con un dispositivo de terceros.

Depuración de enlaces y pruebas paramétricas

Debido a que las interfaces seriales de alta velocidad emplean señales de muy alta frecuencia, la mala integridad de la señal puede interrumpir la comunicación. Cuando surgen tales problemas, las herramientas de depuración pueden proporcionar información valiosa sobre el estado del enlace. La biblioteca de diseño de instrumentos Eye Scan descrita anteriormente brinda a los diseñadores la capacidad de determinar el margen de enlace en las señales recibidas e identificar si los problemas de comunicación se deben a una baja integridad de la señal. Aunque está diseñado principalmente para la depuración durante el desarrollo de la aplicación, esta funcionalidad también se puede emplear en la validación del dispositivo o en la prueba de fabricación para obtener información sobre los parámetros de rendimiento específicos del dispositivo. Sin embargo, los instrumentos seriales PXI de alta velocidad cuentan con valores nominales para amplitud y precisión de temporización, y NI no proporciona rendimiento garantizado o trazabilidad en estos parámetros. La calibración o el ajuste en sitio pueden ser una opción para ciertas aplicaciones.

Otras pruebas paramétricas incluyen la razón de error de bits para una secuencia de bits pseudo aleatoria (PRBS) conocida, utilizando patrones estándares de la industria (PRBS-7, PRBS-15, PRBS-23 y PRBS-31) en lugar de un protocolo específico. Las velocidades de línea del transmisor y del receptor pueden variar para determinar el rango de velocidades de bits soportadas para un DUT en particular. Finalmente, la amplitud del transmisor, así como el pre-énfasis y el post-énfasis pueden variar para probar la sensibilidad del receptor, incluyendo el control automático de ganancia y la ecualización dinámica.

Puede encontrar recursos adicionales para PXIe-6591 y PXIe-6592 en la Comunidad de NI en el siguiente enlace: Herramienta de depuración NI MGT en la Comunidad de NI para obtener más herramientas de análisis de capa física para usar con instrumentos seriales PXI de alta velocidad. Para PXIe-6593 y PXIe-6594, consulte Usar Eye Scan con los dispositivos seriales PXIe-6593 y PXIe-6594 de alta velocidad.

Habilidades requeridas

Aunque LabVIEW y LabVIEW FPGA simplifican drásticamente la tarea de implementar tecnología serial de alta velocidad, cierta experiencia es esencial para garantizar el éxito al programar instrumentos seriales PXI de alta velocidad. Debido a que están diseñados en LabVIEW, la familiaridad con la programación gráfica de LabVIEW es esencial. La página de cursos de capacitación para desarrollo de aplicaciones de NI LabVIEW en ni.com puede ofrecerle esa ayuda. Además, para personalizar la lógica FPGA sin protocolo en LabVIEW FPGA, se requiere una comprensión detallada de la programación de LabVIEW FPGA de alto rendimiento. La guía del desarrollador de NI LabVIEW FPGA de alto rendimientoes un buen recurso para aprender más. Para protocolos con IP existente o ejemplos, se requiere conocimiento y experiencia en VHDL para definir la interfaz entre la IP del protocolo y el diagrama LabVIEW FPGA. Finalmente, para implementar protocolos nuevos o personalizados, se sugiere experiencia avanzada en diseño digital. Ciertos partners de NI ofrecen estas capacidades para aquellos que no las tienen internamente. Los representantes de ventas locales de NI pueden ayudarlo a encontrar un socio adecuado.

| Modelo de uso | LabVIEW | LabVIEW FPGA de alto rendimiento | VHDL | Amplia experiencia en diseño digital |

| Usar personalidad existente | — | — | — | |

| Personalizar el código FPGA, pero no el protocolo | — | — | ||

| Integrar el protocolo existente | — | |||

| Implementar un protocolo nuevo o personalizado |

Tabla 4. La programación de instrumentos seriales de alta velocidad requiere diferentes niveles de habilidades y herramientas dependiendo del nivel de cambios necesarios en la interfaz.

Pasos siguientes

- Aprenda más sobre maximizar el movimiento de datos y el procesamiento de señales con el módulo serial PXI de alta velocidad.

- Aprenda más sobre los conceptos fundamentales de los enlaces de comunicación serial de alta velocidad.

- Vea un diseño de referencia de ejemplo para implementar protocolos seriales de alta velocidad en sistemas de pruebas funcionales para transceptores de radio.

- Obtenga diseños adicionales de referencia de protocolo no incluidos en el controlador de hardware de los ejemplos e IP para instrumentos diseñados por software y la comunidad NI FlexRIO.

- Compre instrumentos seriales PXI de alta velocidad.

- Construya su sistema PXI.