An Introduction to Instrument Driver FPGA Extensions for NI Software-Designed Instruments

Overview

Introduction to Instrument Driver FPGA Extensions

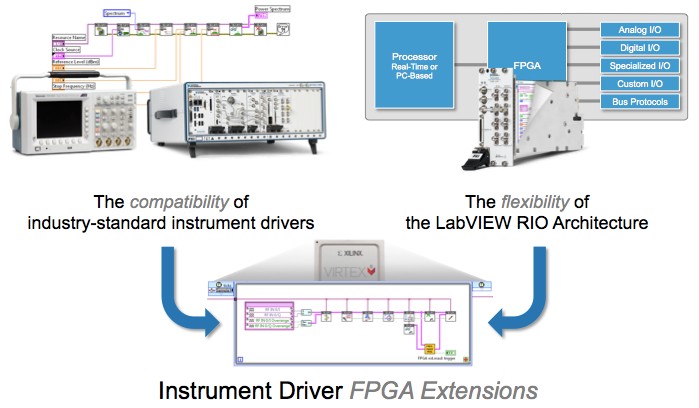

Instrument driver FPGA extensions allow you to customize a software-designed instrument FPGA in LabVIEW while preserving the full feature set of the instrument driver APIs (see Figure 1).

Figure 1: Instrument driver FPGA extensions bridge between the unparalleled flexibility of an open FPGA and the compatibility of standard instrument drivers. You get the best of both worlds in a user-friendly way.

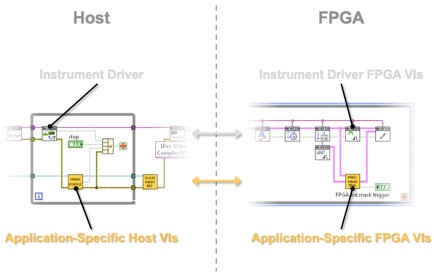

An abstraction layer in the FPGA source code implements the default FPGA capabilities required by the instrument driver API while exposing the relevant control and data signals necessary to enhance automated test applications. Test engineers can add application-specific FPGA IP to the base software-designed instrument FPGA design and then independently control this IP from their host programs in parallel with instrument driver API calls, as demonstrated in Figure 2 below.

Figure 2: Application-specific FPGA IP added to the base software-designed instrument FPGA design can be independently controlled from host programs in parallel with instrument driver API calls.

This architecture enables a variety of application-specific enhancements that take advantage of the parallelism, low-latency control, and processing performance of a software-designed instrument FPGA. These enhancements include custom and/or novel instrument capabilities such as frequency mask triggering; better system integration through hardware-timed device under test (DUT) control and the deterministic triggering of other instruments; accelerated test throughput with FPGA-based measurements and coprocessing; and even closed-loop or protocol-aware tests in which the instrumentation hardware responds to the DUT in real time.

Simple Custom Trigger Use Case

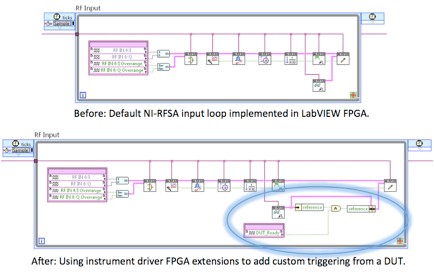

For example, a user may want to implement a custom trigger that waits for a digital signal from the DUT before acquiring data. Figure 3 below shows how instrument driver FPGA extensions and LabVIEW FPGA significantly abstract the complexity of making such a modification to the FPGA.

Figure 3: Example modification to the NI-RFSA input loop on an NI Vector Signal Transceiver in LabVIEW FPGA to implement custom triggering from a DUT.

In Figure 3, a digital signal from the DUT is easily accessed through a LabVIEW FPGA I/O node, and is combined with the default reference trigger made available through the FPGA-based NI-RFSA Trigger VI. The simplicity of this modification demonstrates how when using instrument driver FPGA extensions, you don’t have to understand the complete firmware and driver architecture to make such changes to the FPGA.