NI PXIe-5644R 向量訊號收發器的硬體架構

綜覽

NI 推出 NI PXIe-5644R 向量訊號收發器 (Vector Signal Transceiver,VST),將使用者可設定功能的高彈性 FPGA 加入 RF 儀器,藉此賦予儀器全新定義。

內容

高效能的創新設計

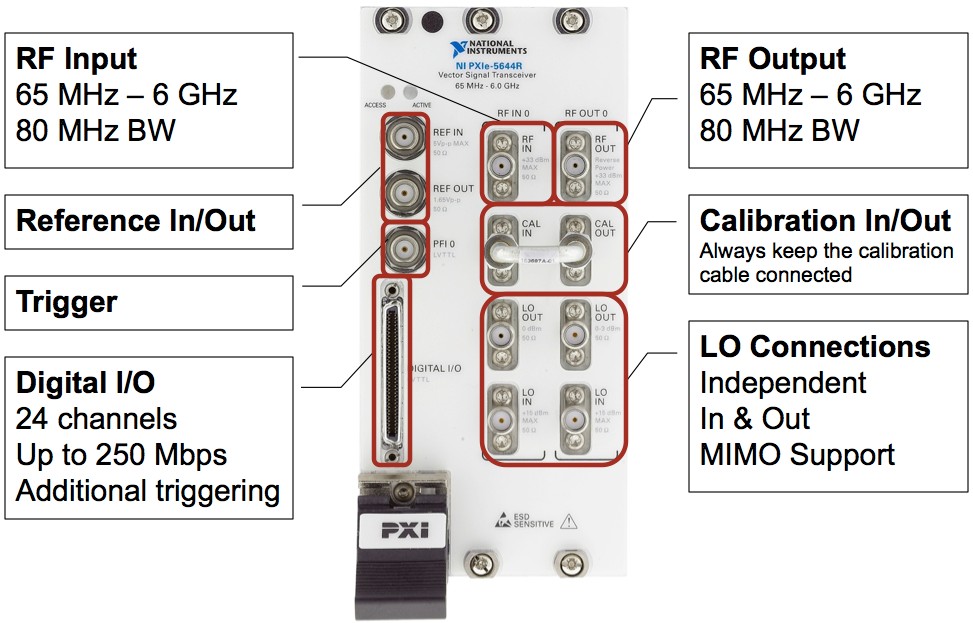

NI PXIe-5644R VST 結合了向量訊號分析器 (Vector Signal Analyzer,VSA) 與向量訊號產生器 (Vector Signal Generator,VSG) 常見的 RF I/O 功能,再加上 NI 或使用者所定義的功能,即可透過 FPGA 處理並控制訊號。RF 輸入與 RF 輸出都具有獨立的局部震盪器 (Local Oscillator,LO),頻率範圍從 65 MHz 至 6 GHz,瞬間頻寬則是高達 80 MHz。NI PXIe-5644R 屬於單一 3 槽式 PXI Express 模組 (參見下圖 1)。只要在單一 PXI Express 機箱中使用多個 VST 模組,即可建置多重輸入/多重輸出 (MIMO) 設定。

圖 1:NI PXIe-5644R 硬體人機介面

那麼 NI PXIe-5644R 到底有什麼魅力?說穿了很簡單,就是小巧機身卻蘊藏著優異效能。透過進階校準與寬頻數位校正,NI PXIe-5644R VST 的精巧機身就能發揮研發級儀器的出色效能。此外測試速度也變快了,再加上使用者可設定功能的高彈性 FPGA,NI PXIe-5644R 堪稱 RF 特性、檢驗、驗證、生產測試的理想選擇。

小巧機身與優異效能的確讓人刮目相看,不過 NI PXIe-5644R VST 最為創新的部分卻是使用者可設定功能的 Xilinx Virtex-6 FPGA,透過 LabVIEW FPGA Module 即可重新設定。FPGA 可連線至 VSA 與 VSG 基頻 I/Q 資料,以及 24 個數位 I/O 通道,資料傳輸率高達 250 Mbit/s。NI PXIe-5644R 集結了 RF、高速數位 I/O、FPGA 技術的強大威力,可因應各式各樣的應用需求,例如待測裝置 (Device Under Test,DUT) 即時控制、客制化觸發、功率伺服、軟體定義無線電、通道模擬等多種應用。

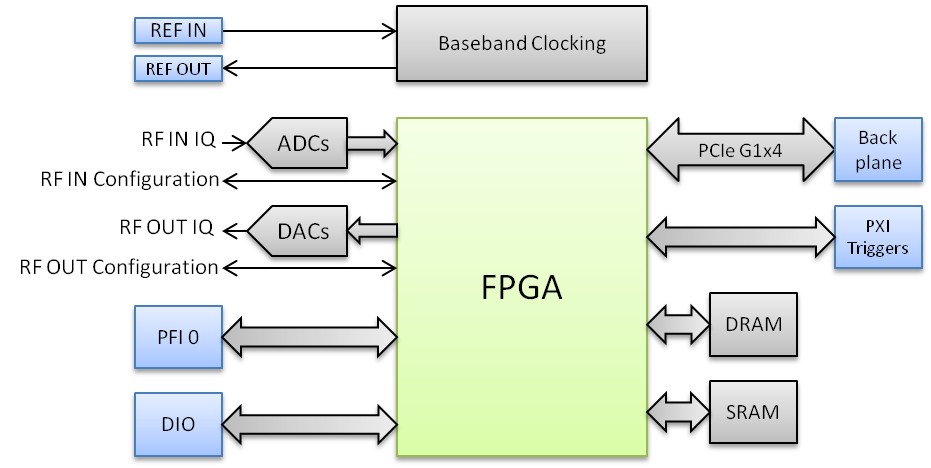

FPGA 基卡架構

NI PXIe-5644R FPGA 基卡 (basecard) 的組成元件包含 Xilinx Virtex-6 FPGA、基頻時脈電路、類比轉數位轉換器 (ADC)、數位轉類比轉換器 (DAC)、可設定功能的數位 I/O 通道 (PFI 0)、數位 I/O 接頭、PCI Express 介面、PXI 觸發器、DRAM、SRAM。

圖 2:NI PXIe-5644R FPGA 基卡的程式方塊圖

Xilinx Virtex-6 FPGA

NI PXIe-5644R 內含 Xilinx Virtex-6 LX195T FPGA,可用於系統設定、數位資料遷移、數位訊號處理。FPGA 可直接連接至 ADC、DAC、PCI Express 匯流排、DRAM、SRAM、PFI 0、數位 I/O 與 PXI 觸發器,所以能提供客制化設定功能,滿足各種應用類型的需求。

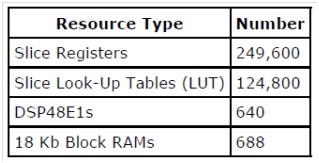

可重新設定的 FPGA 資源

Xilinx Virtex-6 LX195T FPGA 的資源請見下圖。

透過 LabVIEW FPGA 設定功能

透過 LabVIEW FPGA Module 即可充分客制化 NI PXIe-5644R 的 Xilinx FPGA 功能。LabVIEW 非常適合用來設定 FPGA 功能,因為能清楚呈現平行機制與資料流;無論使用者是否熟悉傳統的 FPGA 設計,都可以有效運用可重設硬體的強大效能。

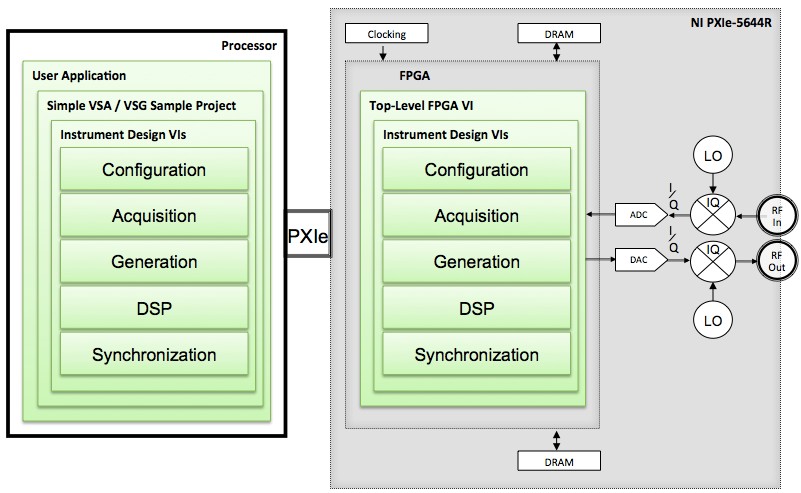

NI 專門針對 NI PXIe-5644R 提供 LabVIEW 範例專案與 Instrument Design VI,方便使用者馬上開始處理量測作業。Instrument Design VI 可讓使用者同時在電腦與 FPAG 上進行 LabVIEW 程式開發,這些 VI 也根據功能來分類,例如設定、擷取、產生、數位訊號處理 (DSP)、同步化 (參見下圖 3) 等。如需深入了解 NI PXIe-5644R VST 的軟體架構,請參閱 VST Software Architecture (VST 軟體架構) 技術文件,也可觀賞 VST 網路研討會。

圖 3:LabVIEW 範例專案與 Instrument Design VI 搭配 NI PXIe-5644R 硬體程式方塊圖

基頻時脈

NI PXIe-5644R 的 FPGA 有多個時脈。主要時脈為取樣時脈,用來計算 ADC、DAC、相關 FPGA 邏輯的時脈。

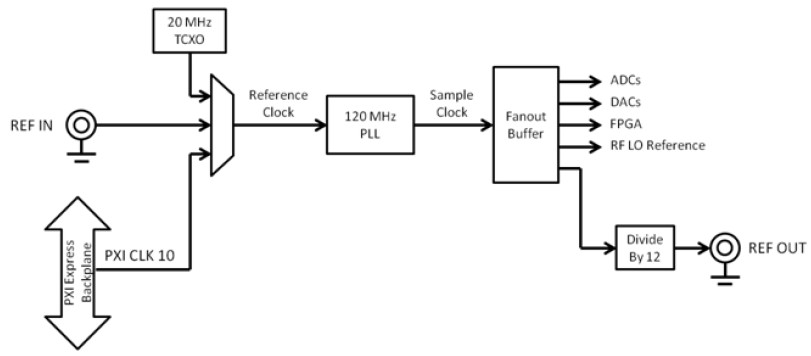

取樣時脈

取樣時脈的速率為 120 MHz,並且由相位鎖定迴圈 (Phase-Locked Loop,PLL) 匯出。使用者可選擇內建的 TCXO、NI 5644R REF IN 人機介面接頭,或 PXI_CLK 10 做為 PLL 的參考訊號。取樣時脈則是 RF IN 與 RF OUT 內接 LO 電路的參考訊號 (參見下圖 4)。雖然取樣時脈頻率固定為 120 MHz,仍可使用 FPGA 的 Fractional Interpolation 與 Fractional Decimation DSP VI 達到高解析度 I/Q 資料傳輸率。

圖 4:NI PXIe-5644R 時脈架構

FPGA 時脈

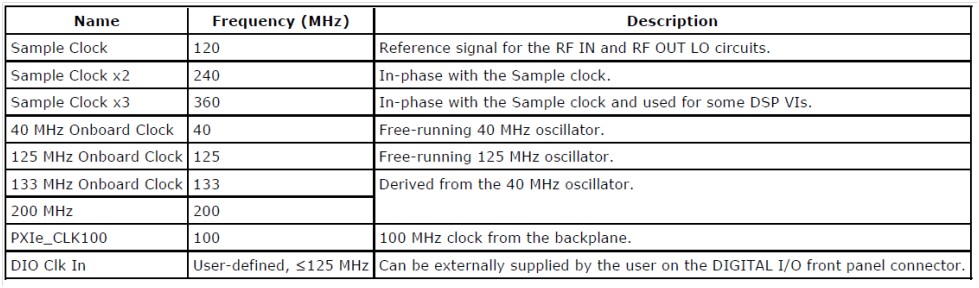

下表列出 FPGA 的時脈。除了這些時脈之外,LabVIEW FPGA 也可在使用者定義的頻率範圍內使用其他時脈。

ADC 與 DAC

NI PXIe-5644R 採用雙通道的 16 位元 ADC 與 DAC。ADC 與 DAC 的時脈設為 120 MS/s 以提供 80 MHz 的複雜頻寬,並且能自動與 FPGA 的取樣時脈域保持同步。這樣一來即可透過完整的同步化功能在相同時脈域內銜接 ADC 與 DAC,進而在接收與傳輸之間提供精確潛時 (deterministic latency)。RF IN 與 RF OUT IQ 資料串流位於 FPGA 的相同時脈域,所以能夠針對即時測試與嵌入式應用提供同步化與精確潛時功能,設計程式時也會更加方便。

PFI 0

PFI 0 是一種 3.3 v LVTTL、雙向、通用的數位 I/O 訊號。PFI 0 最常見的用途是做為觸發輸入或標記/事件輸出。但由於 PFI 0 I/O 緩衝區直接連接至 FPGA,所以使用者可透過 LabVIEW FPGA 針對客制化應用設定其功能。

數位 I/O

使用者可透過 VHCDI 埠使用 NI PXIe-5644R 的數位 I/O。其中有 24 個雙向 LVTTL 數位 I/O 通道,可針對每個連接埠進行設定,而每個連接埠都有 4 個通道 (共有 6 個連接埠)。數位 I/O 接頭還包含 Clock In 與 Clock Out 通道,以及 PFI 1 與 PFI 2 通道,可用於觸發功能,也可當做額外的雙向數位 I/O。由於數位 I/O 緩衝區直接連接至 FPGA,所以使用者可透過 LabVIEW FPGA 針對客制化應用來設定個別數位 I/O 訊號的功能。

連接線與配件

NI 提供豐富的連接線與配件,都與數位 I/O 接頭相容。請注意,這些連接線與配件均採用適合 NI PXIe-5644R 數位 I/O 的客制化針腳,可維持 50 ohm 的傳輸通道環境。因此我們不推薦使用其他的 VHDCI 連接線。

DRAM 與 SRAM

NI PXIe-5644R 具有 2 組 DRAM,每組的容量為 256 MB,預計的最高資料傳輸率為 2.1 GB/s,並且可分別透過 FPGA 存取。這些 DRAM 組適用於一般用途,但通常用來儲存要產生的波形或已擷取的波形。

此外還有 2 MB 的內建 SRAM,最高資料讀取速度為 40 MB/s,最高資料寫入速度則是 36 MB/s。SRAM 非常適合透過 FPGA 來串流資料 (比如說將 I/Q 轉換為數位資料)。

PCI Express 介面

NI PXIe-5644R 具有 PCI Express、Gen 1 x4 背板連接功能,可用於 DMA 傳輸、設定 I/O 與 P2P 串流。

接收器架構

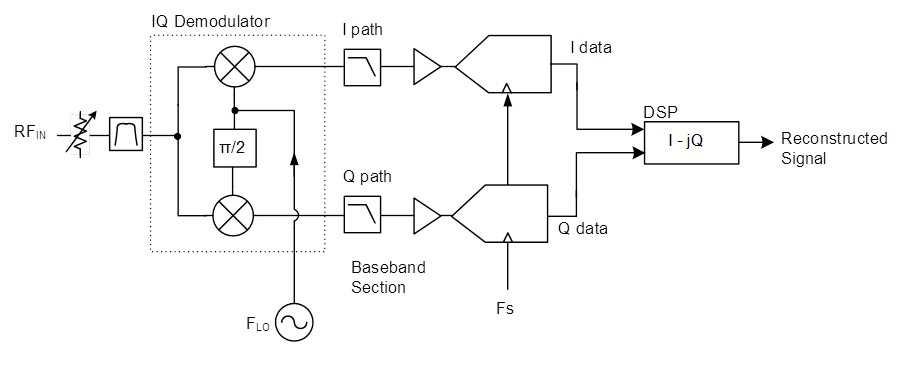

NI PXIe-5644R 配備零差 (homodyne) RF 接收器,也稱為同步 (synchrodyne)、零中頻 (zero-IF) 或降頻 (direct-down) 轉換接收器。就零差接收器而言,所接收的 RF 訊號會進入頻率混和器,這和傳統的外差接收器一樣,例如 NI PXIe-5665 與 NI PXIe-5663E VSA 的接收器。然而,不同於外差接收器的是,零差收發器的 LO 頻率和所接收的 RF 訊號頻率要不是一模一樣,就是非常接近,因此會造成以 DC 為中心的訊號或低 IF 訊號,例如 10 或 20 MHz。

輸入訊號會混和至基頻,並分為同相 (In-phase,I) 與正交 (Quadrature-phase,Q) 的部分,其中的載子是同相並且偏移 90 度。I 與 Q 路徑訊號接著會分別數位化,變成 I 資料與 Q 資料。最後,I 與 Q 資料串流會在軟體結合,處理原始訊號。圖 5 為簡化的零差架構,也稱為零中頻架構。

圖 5:零差 (零中頻) 架構基本程式方塊圖

零差 (零中頻) 接收器的好處

相較於傳統的外差架構,零差架構的優勢多不勝數,比如說設計更簡潔、成本更低、耗電量更少、選擇性更高,因此可區分訊號重疊的鄰近通道;其他優勢還有更高的可能頻寬、單一 LO 的精簡設計,以及隨之而來的小巧機身。更多詳細說明請見下列段落。

1. 頻寬:配備單一 ADC 的接收器針對訊號頻寬設有上限,也就是取樣時脈頻率的 40%。在相同的取樣時脈頻率中,零差架構可將頻寬加倍,或提供 80% 的取樣時脈頻率,主要是因為採用了 2 個 ADC。一般而言,ADC 如果具有較低的取樣時脈頻率,無雜波干擾動態範圍 (SFDR) 與訊噪比 (SNR) 效能也會較為出色。零差接收器可提供較寬的頻寬,卻不必犧牲 ADC 效能,這是單一 ADC 接收器所無法企及的。

2. 單一 LO:由於多通道量測系統對多重輸入/多重輸出 (MIMO) 應用而言越來越重要,所以必須共用 LO。零差架構只須共用一個 LO,傳統的外差架構卻得共用多個 LO,因此零差架構的成本效益較佳,設定系統時也沒那麼複雜。

3. 精簡設計:零差架構的 RF 設計比外差架構來得簡單多了。LO 訊號更少,也不需要龐大又昂貴的 RF 與 IF 濾波器,而且零差架構的轉換階段變少了,因此設計更加精簡。

零差 (零中頻) 接收器的挑戰

雖然好處多不勝數,但零差架構也帶來特有的挑戰,比如說無法執行封包偵測。NI PXIe-5644R 採用正交偵測與數位訊號處理功能,所以能解決這個問題。

DC 偏移是零中頻架構的另一項挑戰。任何在零中頻架構中混和至 0 Hz 的訊號都會造成 DC 的頻譜元件。在擷取資料的瞬間頻寬中段,這樣的失真狀況會減少。拼貼起來的已擷取資料會組成頻譜,瞬間頻寬則會補償這些資料的頻率,接著此頻譜會顯示每項資料擷取中段所複製的 DC 偏移。只要套用偏移值,就可以在經過數位化的 I/O 資料串流中消除 DC 偏移。每個 LO 頻率都應該額外套用另一個消除程序,只要執行 NI PXIe-5644R 的自我校準程序即可自動完成此程序。

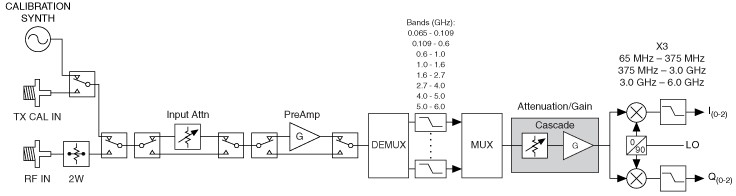

接收器訊號路徑

NI PXIe-5644R 接收器設計的高階架構請見圖 6。此程式圖的重點為校準合成器、可選購較高功率的衰減器、可選購較低功率訊號的放大器、頻外選擇濾波器、額外增益與衰減訊號處理,以及根據頻率對 3 個混合器之一執行解調變作業。

圖 6:NI PXIe-5644R 接收器程式方塊圖

選擇濾波器組共有 8 個不同的路徑,包含低通 (lowpass) 或帶通 (bandpass) 濾波器。這些濾波器可讓接收器過濾出大量不想要的雜訊,僅集中在重要的訊號範圍內。執行選擇過濾與某些額外的訊號處理作業之後,RF 訊號就會接著傳送到 3 個解調變器之一,視頻率而定。每個解調變器都會在特定頻帶中運作,以便最佳化增益與相位。

接收器路徑包含好幾個固態衰減器,提供 80 dB 以上的衰減值,以 1 dB 為變化單位。RF 輸入則是 AC 耦合。此外還有 3 個可切換的增益放大器和 1 個前置放大器,可擴大動態範圍並改善雜訊係數。

至於內建的低相位雜訊 LO 可以單一 LO 來源連接至多個降轉換器。採用相同的 LO 來源對相位同調訊號擷取應用來說非常實用,例如多重輸入/多重輸出 (MIMO) 系統。使用此設定時,每個共用通用 LO 的 NI PXIe-5644R RF 通道都會調整至相同的 RF 頻率。

經過降轉換的基頻訊號會直接傳輸至 NI PXIe-5644R 的內接 ADC 通道。ADC 通道會在 16 位元的動態範圍內以 120 MS/s 的速度將基頻類比訊號數位化,接著把結果傳輸至內建的 FPGA 以便進一步處理,最後再傳輸至主機。

降轉換器

NI PXIe-5644R 接收器具備單階段、直接轉換 (I/Q) 降轉換器。RF 訊號會從已設定的 LO 頻率降轉換至 DC,在此基頻訊號會經過數位化以利後續處理。此架構可提供更大的瞬間頻寬,同時提高影像抑制並避免 LO 洩漏。寬頻正交校正可加強影像抑制與 LO 洩漏效能。接收器路徑經過最佳化,可當做向量訊號分析器並用於寬頻解調變。

低 IF 模式與帶內重新微調

低 IF 接收器是一種採用 IQ 解調變器的接收器,其程式方塊圖和圖 5 的零中頻接收器一模一樣。不同於零中頻接收器 (LO 頻率位於已調變訊號的頻率範圍內),低 IF 接收器的 LO 頻率則位於已調變訊號的範圍外。因此 DC 元件不會位於降轉換範圍內;而且許多與 DC 相關 (例如 DC 偏移、1/f 雜訊,有時候甚至包含基頻諧波) 的減損現象就不會造成任何影響。

使用者可結合 LO 微調與數位頻率轉換功能,進而以低 IF 模式操作 NI PXIe-5644R。透過載子以數位轉換頻率來擷取或產生重要訊號,即可避免直接轉換拓撲可能會有的 LO 洩漏現象。這時必須犧牲低 IF 收發器所能發揮的 BW 最大值,而且如果 ADC 取樣率相同的話,這只是零中頻接收器的一半而已。NI PXIe-5644R 最高支援 80 MHz 的複雜瞬間頻寬,此外還有額外的 4 MHz 複雜頻寬可用於數位頻率校正。額外的頻率轉換能減少可用的 80 MHz 頻寬至 (80/2) - (x- 2) MHz,這裡的 x 是規定的數位頻率轉換。

傳輸器架構

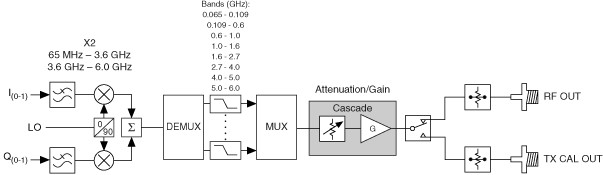

NI PXIe-5644R VST 的 RF 傳輸器架構包含 2 個調變器、1 個濾波器組,和額外訊號處理功能。高階程式方塊圖請見圖 7。

圖 7:NI PXIe-5644R 傳輸器程式方塊圖

傳輸器訊號路徑

NI PXIe-5644R 的 2 個調變器和 NI PXIe-5673E VSG 的調變器一模一樣,都已根據頻率針對相位與增益平衡進行優化。NI PXIe-5644R RF 傳輸器濾清器組則是和 RF 接收器所用的一樣,都具備 8 個路徑與低通/帶通濾波器,如圖 7 所示。

過濾之後,RF 訊號會進入串聯訊號處理階段,其中包含 3 個可設定功能的衰減器、1 個可選擇的放大器、2 個固定放大器。最後,RF 訊號會切換至 RF Out 或 Cal Out 人機介面接頭,取決於所校準的傳輸路徑為何。

升轉換器

NI PXIe-5644R RF 傳輸器路徑具備 1 個單階段、直接轉換 (I/Q) 升轉換器,可在已設定的 LO 頻率將基頻訊號從 DC 升轉換至 RF。此架構可提供更大的瞬間頻寬,同時提高影像抑制並避免 LO 洩漏。寬頻正交校正可加強影像抑制與 LO 洩漏效能。此路徑經過最佳化,可當做 CW 產生器或 VSG 並用於寬頻調變。

傳輸器路徑包含 4 個固態衰減器,具有 100 dB 以上的衰減值,以 1 dB 為變化單位。產生高功率訊號時還能使用額外的可切換增益放大器。

傳輸器路徑內建低相位雜訊 LO,可透過單一 LO 來源連接多個升轉換器。採用相同的 LO 來源對相位同調訊號產生應用來說非常實用,比如說 MIMO 系統。使用此設定時,每個共用通用 LO 的 NI PXIe-5644R RF 通道都會調整至相同的 RF 頻率。

考慮平均功率與波峰因數

波峰因數是峰值訊號功率與平均均方根 (RMS) 功率之間的功率變化。正弦波訊號的波峰因數為 3 dB,CW 模式也是如此。換句話說,正弦波訊號的平均 RMS 功率比峰值功率少了 3 dB。就已調變訊號而言,尤其是 OFDM,波峰因數可能會大許多,順序為 10 dB 到 12 dB。

設定裝置以利產生訊號時,務必要考慮到訊號的平均 RMS 功率與波峰因數。NI PXIe-5644R 最高支援 6 dBm 的平均功率輸出,同時最高支援 12 dB 波峰因數。如果超過 6 dBm 的平均功率,就無法保證裝置可受到校準且能線性產生訊號。更重要的是,如果平均功率設為超過 6 dBm,而訊號的波峰因數仍維持在 12 dB (或以上),可能會發生嚴重的過溢現象,否則 NI PXIe-5644R 的反向功率保護電路或許會因此啟動。

合成局部震盪器 (LO) 架構

NI PXIe-5644R 的頻率範圍為 65 MHz 至 6 GHz,微調解析度不到 1 Hz。微調解析度結合了 LO 步進功能與頻率轉換 DSP,而 FPGA 皆已配備這些功能。

其中共有 2 個 LO 步進模式:

NI PXIe-5644R 合成器 LO 會以 120 MHz 的時脈開始進入 PLL,而 3 個向量控制震盪器 (Vector-Controlled Oscillator,VCO) 的頻率分別為 2 至 2.5 GHz、2.5 至 3 GHz、3 至 4 GHz。如果想要的輸出訊號低於 4 GHz,那麼目前訊號就必須切換至分壓器;一樣的道理,如果想要的終端訊號為 4 至 6 GHz,那麼目前的訊號就得切換至雙倍器 (x2 乘法器)。接著是搭配額外分壓器的濾波器組,可在必要時移除諧波。

套用頻率增益之後,訊號就會切換至內接或外接震盪器,而外接震盪器主要用於需要相位同調 MIMO 的應用狀況。如要提高 MIMO 設定的效能,可在匯出前透過校準 ADC 來校準 LO 路徑。LO 訊號會接著進入濾波器組,搭配 NI PXIe-5644R RF 接收器/傳輸器所用的相同低通與帶通濾波器,如圖 8 所示。

圖 8:NI PXIe-5644R 合成器 LO 高階程式方塊圖

頻譜精純度

一旦所接收的 RF 訊號與 LO 混合,就會承接 LO 的頻譜外圍。因此 LO 務必具有優異的頻譜精純度。通常頻帶 VSA 會使用現成的整合式合成器,一般而言這種合成器比不上傳統的分離式合成器。我們將 NI PXIe-5644R 設計成一種寬頻儀器,因此內建了傳統的分離式整合器。這樣一來,NI PXIe-5644R 即可在整個儀器頻率範圍內提供出色的量測效能。

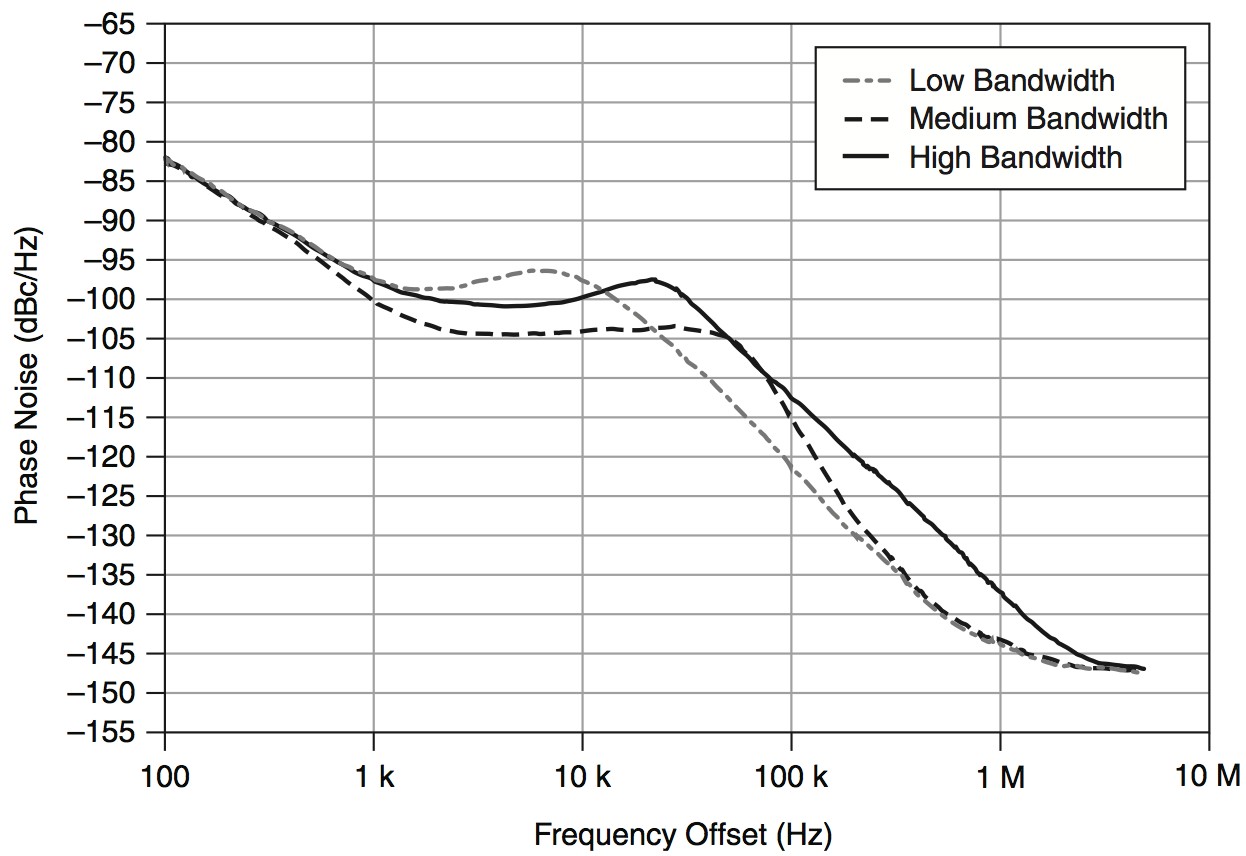

如下所示,NI PXIe-5644R 具備 3 種不同的 PLL 頻寬選項,這些選項都會影響相位雜訊對趨穩時間 (phase noise versus settling time)。

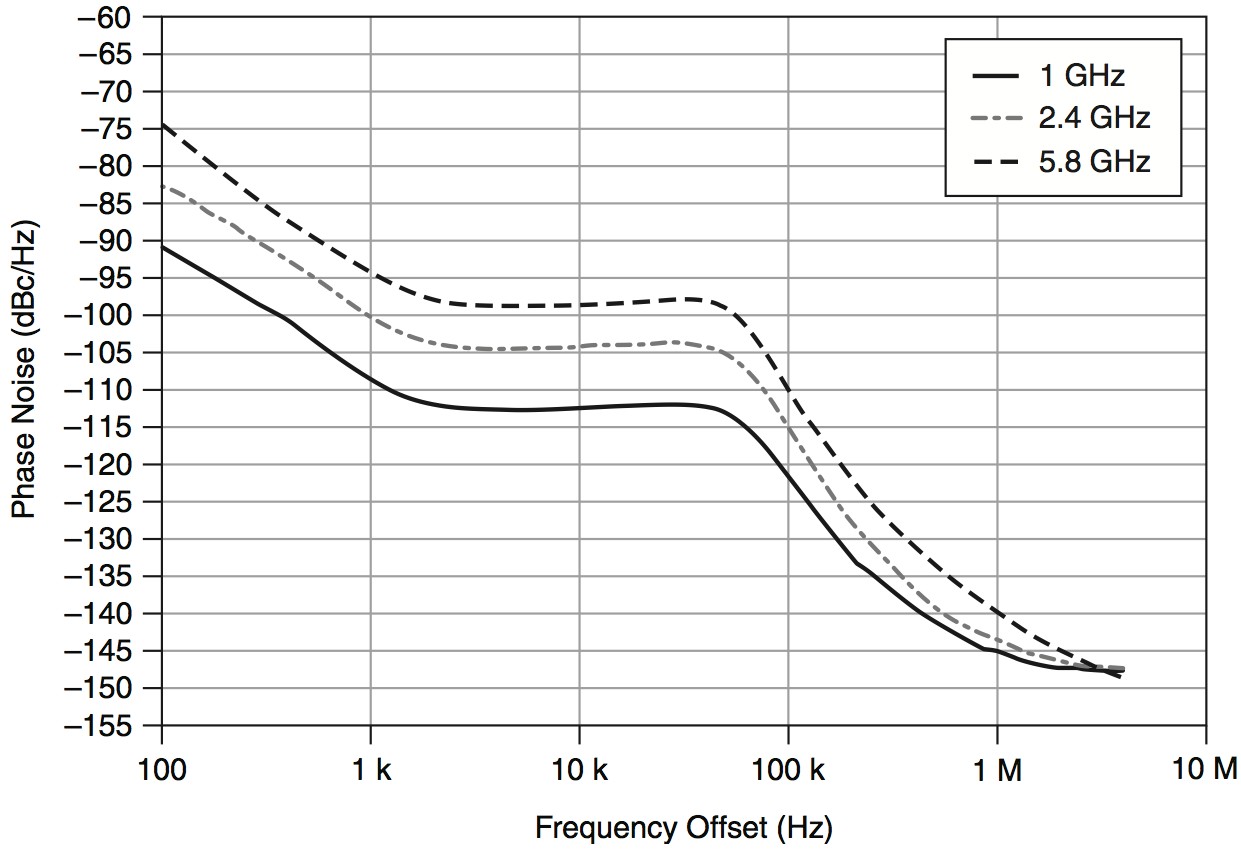

如需量測 802.11ac 與 LTE 等 RF 標準,我們推薦中頻寬選項;但如果不在意微調速度的話,低頻寬選項也會是不錯的選擇。如果選用高頻寬選項,可能會出現快速跳頻 (frequency hopping) 的狀況。圖 9 顯示出不同的 PLL 頻寬選項各有不同的相位雜訊。下圖 10 顯示出,僅選用中頻寬選項時不同頻率的相位雜訊分佈。

圖 9:2.4 GHz 與迴路頻寬所量測到的相位雜訊

圖 10:選擇 PLL 中頻寬選項時,於 1 GHz、2.4 GHz、5.8 GHz 所量測到的相位雜訊

校準

所有的 NI PXIe-5644R 都經過分別校準,以保持其出廠時的精確頻率與振幅響應。而且出貨產品均具備校準認證,確保可追蹤 NIST 的精確度。外部出廠校準會調整頻率參考、內接/外接 LO 路徑增益、RF 輸入/輸出增益。如果希望 NI PXIe-5644R 能持續保有所需規格,我們推薦客戶選用 1 年原廠校準 (如容許規格變化,我們亦提供 2 年校準)。

校準路徑

NI PXIe-5644R 必須仰賴裝置內 RF 輸入與 RF 輸出校準區之間的固定路徑。此路徑可透過 SMA-SMA 半精確接線 (連接 CAL IN 與 CAL OUT 人機介面接頭) 加快校準速度。請勿鬆開此接線,也請勿將此接線自裝置人機介面移除,因為這樣會影響有效的自我校準功能。

自我校準

此外,只要環境溫度變化超過 5°C,則建議客戶採用自我校準功能。溫度變化可能會有損許多 NI PXIe-5644R 規格的效能。執行自我校準功能即可針對特定的環境溫度來補償/優化效能。自我校準功能可調整下列 NI PXIe-5644R 參數,以便提高溫度校正速度:

- LO 路徑增益

- RF 輸入增益

- RF 輸出增益

- RF 輸入 LO 洩漏

- RF 輸出 LO 洩漏

- RF 輸入影像抑制

- RF 輸出影像抑制

校準合成器可提供穩定的頻率,搭配低失真放大器以提供穩定振幅。裝置的校準表包含頻率與功率,此外還有頻率的向量校準功能。NI PXIe-5644R 之所以能透過小巧機身提供研發級的儀器效能,這項進階校準技術可說是幕後推手之一。