管理 FPGA 佈署項目

綜覽

FPGA 的主要優勢之一,就是可以根據特殊的應用需求,載入不同的硬體特性 (personality)。但也因為 FPGA 非常靈活,所以必須針對開發、獨立佈署與維護等工作項目來選擇正確的實作方式。本文將探討 LabVIEW 環境中開發生命週期的各個相關階段的最佳實践。

內容

在磁碟上管理 FPGA 檔案

LabVIEW FPGA 應用程式是透過特定 NI FPGA 裝置專屬的 VI 開發而成的。FPGA VI 則會經過編譯程序,最後產生一個 bitfile,下載至 FPGA 時就會進行設定,並根據 VI 所指定的方式開始運作。如果 FPGA 經過修改,就必須重新編譯,然後覆寫儲存於開發機器上的 bitfile。這樣一來,最好採用版本控制系統 (Versioning System),才能確保同時適用於 FPGA VI 與 Bitfile。

由於應用程式會在 FPGA VI 進行設定,所以其通常會納入原始碼控制系統內。雖然無法開啟 bitfile 以參照應用程式邏輯,但應該可以納入版本控制系統,因為 bitfile 提供了編譯過的靜態檔,因而整個軟體開發流程都可以回去參照此檔案。

如果已實作 bitfile 版本控制,提交至原始碼控制之前可以重新命名為重要的數值,以便日後輕鬆參照。預設情況下,比特檔案位於與 FPGA VI 相同的「FPGA 比特檔案」資料夾中。要確認比特檔案的位置,請完成下列步驟:

- 在 LabVIEW 專案浏览器窗口中,瀏覽 FPGA VI,右鍵點擊,並選擇 Target-specific Properties...

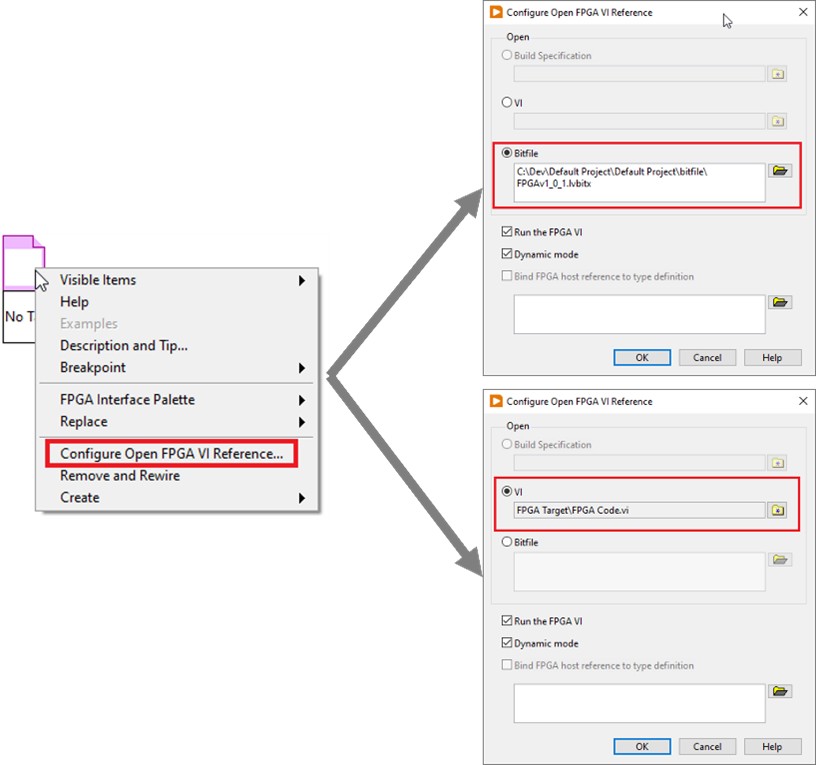

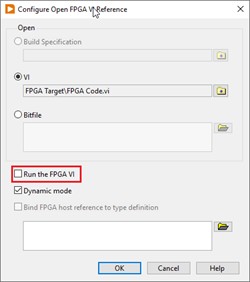

在主機應用程式中參照 FPGA 的方式取決於系統實作的版本控制。如要參照特定的 FPGA VI 版本,就必須透過原始碼控制加以檢查,接著必須更新主機 VI 的「Open FPGA Reference」函式以指向 VI (圖 1)。如果針對版本控制參照 Bitfile,就應該更新「Open FPGA Reference」以便指向 Bitfile,而不是 FPGA VI。

圖 1: Open FPGA VI Reference 可設定為參照 bitfile 或 FPGA VI。

在開發程序中檢驗 FPGA 邏輯

在開發 FPGA VI 的期間,必須測試程式邏輯,以便檢驗其運作狀況。如果要測試應用程式的運作狀況,可使用互動式的人機介面通訊方式,並且在開發環境中建立一個適用於 FPGA VI 的 Run 按鈕。然而,此程序涉及複雜的編譯程序,會把 LabVIEW FPGA VI 轉換成 bitfile,接著佈署至位置不一定的目標系統,這 需要數分鐘至數小時。此外,開發人員必須有目標裝置,才能佈署 FPGA 應用程式。

如果不想要針對每項測試作業重新編譯並佈署新的應用程式,LabVIEW FPGA Module 也提供了 FPGA 模擬環境,開發人員可藉此在開發機器上執行應用程式。這樣一來,即可在投入長時間的編譯程序之前檢驗整體的應用程式邏輯。此外,由於應用程式會在開發機器上執行,所以不需要實際的硬體,即可執行 FPGA 模擬。如要了解透過 LabVIEW 模擬 FPGA 系統的方式,請參閱 Efficient Development and Debugging with LabVIEW FPGA 這篇技術文章。

請切記,互動式人機介面通訊只能用於 FPGA 應用程式的開發階段,因為 FPGA 的設定隨時都會改變。如果裝置正在進行電力循環,bitfile 下載至 FPGA 之後就會不見,所以獨立佈署必須採取另一種方式。

佈署獨立式 FPGA 應用程式

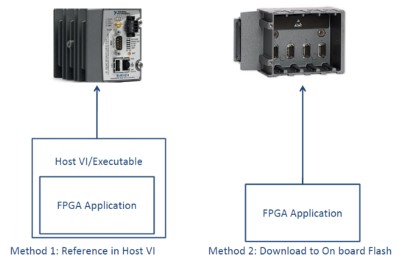

一旦完成 FPGA 應用程式的開發階段之後,就要把所產生的 bitfile (通常稱為「特性」,personality) 佈署至系統內。檔案的佈署方式取決於 FPGA 是否需要主機 VI。如果 FPGA VI 確實需要通訊或資料記錄功能,就必須開發主機 VI。然而,如果 FPGA 可以獨立運作,不需要其他系統,那麼其特性就會儲存在 FPGA 系統內的非揮發性快閃記憶體。圖 2 說明了這兩種佈署方式的關係,以及 FPGA 特性在 CompactRIO 的儲存位置。

圖 2:兩種獨立式佈署方式。

方式 1:在主機 VI 中參照 FPGA

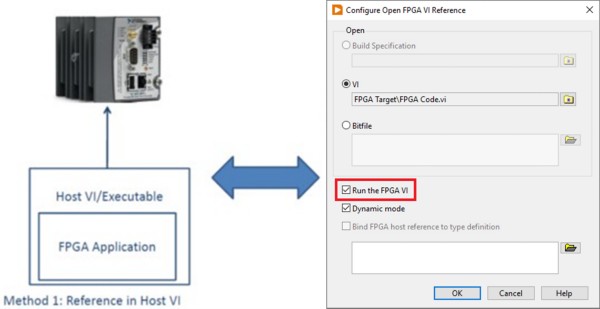

如圖 3 所示,部署 FPGA 個性最常見的方法是將其嵌入主機應用中。當主機執行中使用「開啟 FPGA 參考」函式時,應用會包含此項功能。之後只要主機應用程式編譯為可執行檔時,FPGA 應用程式就會嵌入此檔案。因此,一旦佈署並執行主機應用程式時,就會下載 bitfile,並且在呼叫「Open FPGA Reference」函式時開啟參照至 FPGA。

圖 3: 如果把 Open FPGA VI Reference 用於主機 VI,FPGA 的 bitfile 就會嵌入主機檔案。

由於 bitfile 已嵌入可執行檔,這種作法的好處之一就是能把兩個系統的應用程式納入同一個檔案。此外,由於主機檔案屬於一種可執行檔,只要使用 FTP 程式即可輕鬆傳送至主機。

同時請注意,載入 FPGA 應用程式之前必須透過主機應用程式來進行初始化作業,所以從裝置啟動到 FPGA 設定期間會出現延遲狀況。此外,啟動時無法確知系統的輸入與輸出通道狀態,因為 FPGA 尚未經過設定。所以如果 FPGA 完全獨立於主機應用程式之外,其特性就會儲存在內建的 FPGA 快閃記憶體。

方式 2:把應用程式儲存在 FPGA 系統的非揮發性快閃記憶體

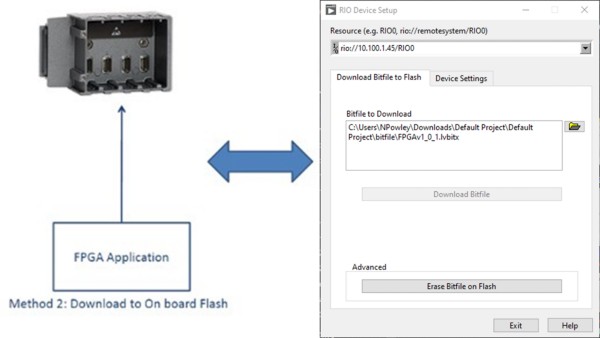

使用 NI-RIO 驅動程式隨附的 「RIO 裝置設定」 功能,即可把 bitfile 下載到 FPGA 目標裝置的快閃記憶體 (圖 4)。這樣一來,一旦系統重新啟動,就會馬上把特性從快閃記憶體載到 FPGA,無論主機應用程式的執行項目為何都一樣。此外,把特性下載到快閃記憶體後,就可以確保啟動裝置時,可以將所有的輸入與輸出通道驅動至已知狀態,因為已經立即載入 FPGA。

圖 4: RIO Device Setup 可用來把 FPGA bitfile 下載到 FPGA 的內建快閃記憶體。

如果確實出現主機通訊狀況,就必須修改主機應用程式,「Open FPGA Reference」函式才不會覆寫已自動載入 FPGA 的特性。如要關閉下載功能,可以取消選取「Open FPGA Reference」函式設定中的「Run the FPGA VI」選項 (圖 5)。此外,啟動時已立即從快閃記憶體載入 FPGA 特性,連接中的主機當下並無法控制 FPGA 的狀態。如果需要主機來控制 FPGA,該特性就應該會嵌入主機應用程式,而不是儲存在快閃記憶體內。

圖 5: 如果從內建快閃記憶體載入 FPGA 的 bitfile,就要關閉「Open FPGA Reference」設定視窗中的「Run the FPGA VI」選項,主機應用程式才不會覆寫 FPGA 的 bitfile。

取決於特定應用的需求,可能會需要不同的特性佈署架構。然而,就大多數的實作案例來說,最好把特性嵌入主機應用程式,因為 FPGA 通常會受限於主機應用程式。

大量佈署 FPGA 應用程式

如果要佈署許多 FPGA 架構系統,而且其中的內建快閃記憶體會用來儲存特性,那麼手動把特性載入每個裝置並非實際做法。透過複製與部署 (RAD) 公用程式,您可使用 RAD 複製即時目標的影像,以提高目標與系統的部署效率。

如果特性已嵌入主機應用程式,就會透過可執行檔傳送出去。這樣一來,如果必須佈署其中許多系統,可使用即時目標系統複製或 Windows 架構的安裝程式,以便自動執行佈署程序。

保持現有的 FPGA 應用程式

通常必須藉由修改過的特性版本,才能更新已佈署系統的影像。只要覆寫系統上的檔案,就可以透過一樣的方式重新執行佈署程序,就像剛開始那樣;然而,佈署位置等環境變數可能會影響佈署程序。RIO Device Setup 應用程式與 FTP 應用程式可解決這類問題,其可透過網路來傳輸檔案。

如果遠端位置沒有網路,而且 FPGA 特性已嵌入主機 VI,技術人員的機器只需要 FTP 功能,即可把更新資訊傳送到主機。如果特性儲存在 FPGA 內建的快閃記憶體,遠端機器就會需要安裝 NI-RIO 驅動程式,才能利用 RIO Device Setup 應用程式。

最佳實務概述

- 建立 FPGA VI 與 bitfile 備份,以便建置版本控制系統

- 在開發電腦上執行模擬作業即可檢驗 FPGA 邏輯,不必每次都要編譯並佈署至實際系統

- 僅在開發階段中使用互動式人機介面通訊佈署方式

- 開發主機應用程式,FPGA bitfile 可以嵌入此程式 (如果兩者互有影響),否則的話可以把應用程式載入內建快閃記憶體

- 若要大量部署 FPGA 應用,如應用已下載至內建觸控器,請使用複製與部署 (RAD) 公用程式 (Replicate and Deployment Utility)

- 請使用相同的維護佈署方式,就像剛開始佈署一樣