哪一種 USRP 適合您?

綜覽

如果您打算開發無線應用,並且需要選擇 Software Defined Radio (SDR),您可能會有一些疑問,例如:

- 我該從何處著手?

- 哪一種通用軟體無線電週邊設備 (USRP) 才適合我?

- 我該使用哪一種軟體開發工具?

此技術文章說明不同 USRP 型號的主要差別,同時有助於您選出適合的無線電。

內容

Software Defined Radio 簡介

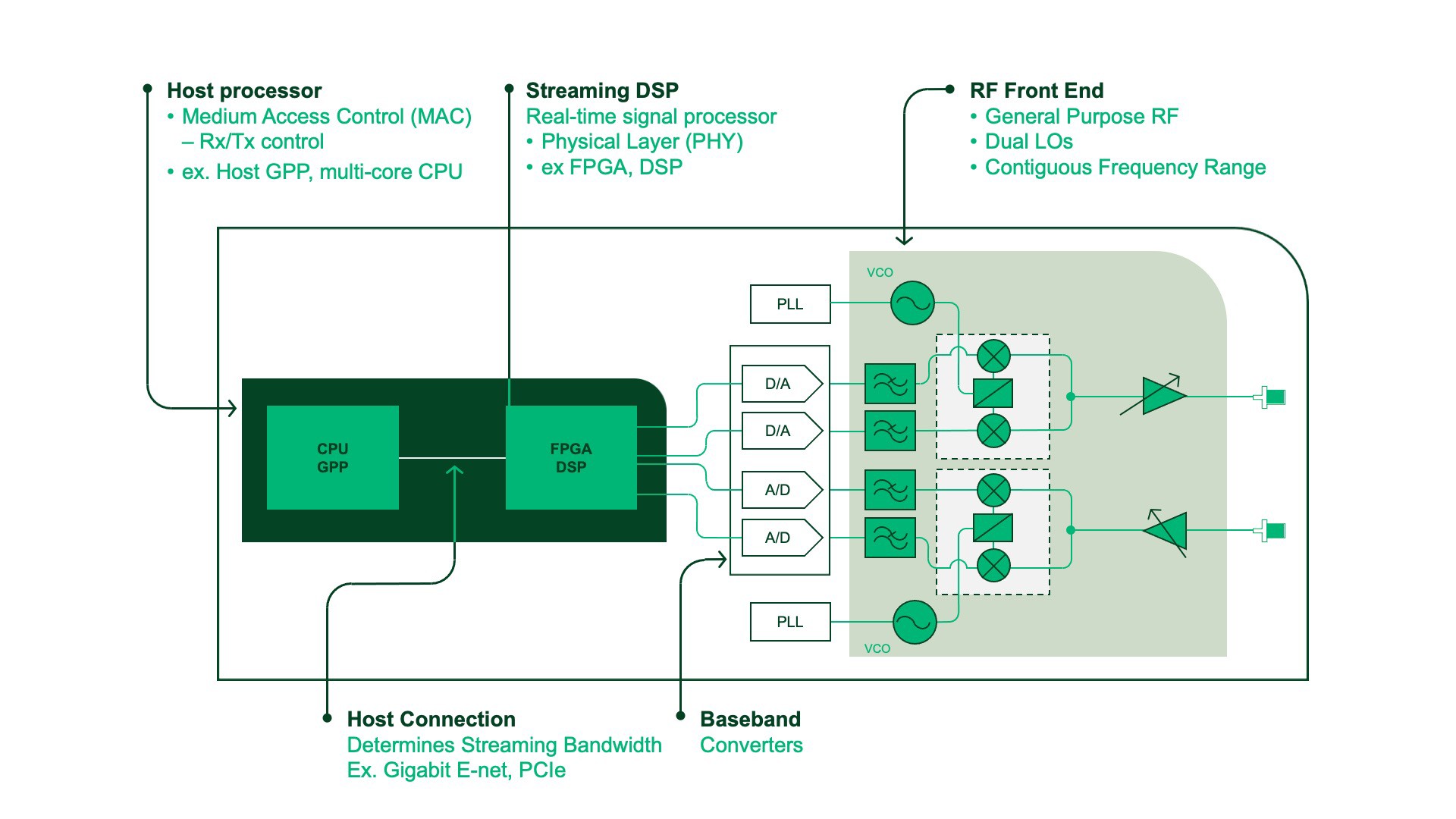

Software Defined Radio 是一種無線裝置,常用於無線研究原型製作以及已部署的應用。SDR 常用於通訊、新一代雷達、電子作戰、空中傳輸 (OTA) 測試,以及 5G 研究。大多數的 SDR 均採用一般硬體架構,包括通用處理器 (GPP)、FPGA,以及效能各異的 RF 前端。

圖 1: 一般 SDR 硬體架構

在開發主機應用程式碼時,工程師會使用以下這些常見的工具:

- LabVIEW

- C/C++ 或 Python 搭配開放原始碼的硬體驅動程式

- 開放原始碼的 SDR 架構,例如 Redhawk 或 GNU Radio

- MathWorks® MATLAB® 軟體與 Wireless Testbench™ 軟體

您可根據所用的軟體開發工具和作業系統,判斷哪一種無線電適合您的應用。

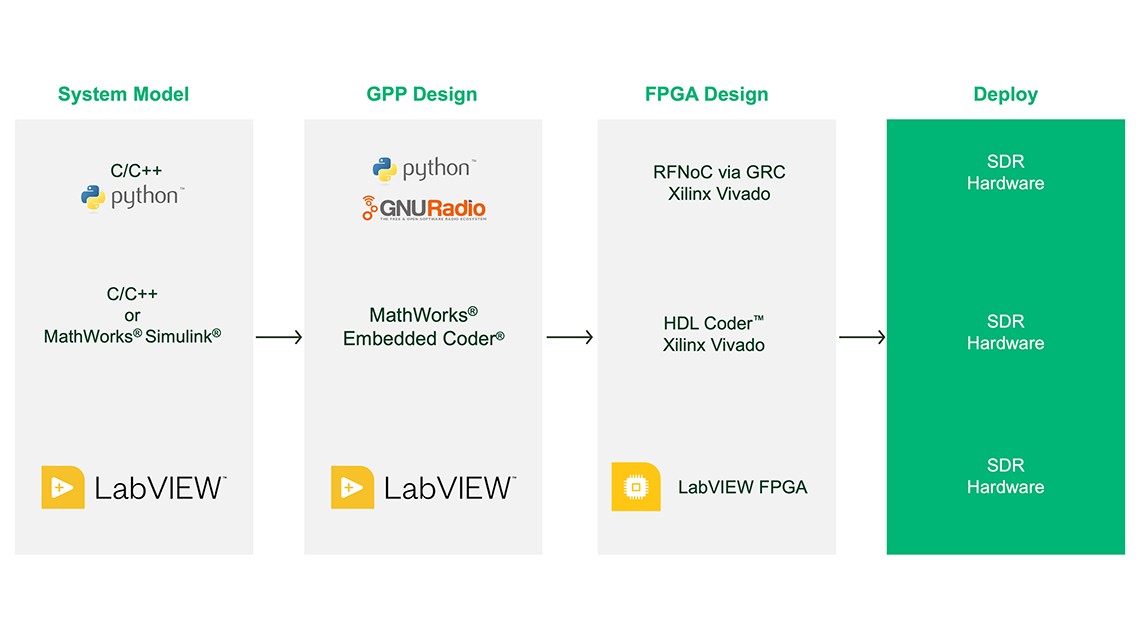

許多應用皆需要 FPGA 裝置所提供的訊號處理硬體加速功能。有多種 USRP 提供此功能,也有許多不同的 FPGA 開發方式 (稍後會深入探討)。

圖 2 概要說明了 USRP 上可用於軟體與 FPGA 開發的常見工具流程。

圖 2: SDR 軟體與 FPGA 選項

NI 與 Ettus Research 通用軟體無線電週邊 (USRP) 產品是一系列軟體定義無線電,其設計旨在因應各類無線原型製作與部署需求。接下來探討各種軟硬體相關注意事項,協助您選擇適合的無線電。

硬體選項

選擇適合您應用的 USRP 裝置時,建議可以先思考有關訊號參數、尺寸、重量、功率、成本 (SWaP-C)、效能,以及環境應用等需求的問題。問題 1:我需要什麼樣的中心頻率與頻寬?

這個問題不難,但下一個問題比較深入:我要如何規劃將訊號資料移到裝置上或從裝置移除?

這個問題突顯出資料介面的重要性。例如,USRP-290x 機型透過 USB 與主機連接,且受限於該介面的最大持續頻寬;而 Ettus USRP X440 則配備兩個 100 GbE 介面,能夠同時傳輸更多的資料。

若要深入了解 USRP 介面頻寬相關考量要點,請參閱 Ettus Research 知識庫有關 USRP 頻寬與取樣率的文章。

大部分 USRP 裝置的最大頻率上限為 6 GHz,有一些會更高;然而,NI Ettus USRP X410 的運作頻率可達 7 GHz 頻帶。根據所用的類比晶片組,有些無線電在較低的頻率端會降低至 75 MHz,有些則會降至跟 DC 一樣低。請見圖 16,了解每個型號的細節。

圖 3: Ettus USRP X410 採用 RFSOC 架構,是中心頻率最高 7.2 GHz 的高頻率寬頻 SDR。

成本與效能之間的取捨

在選擇 USRP 裝置時,有些方面需要權衡取捨,尤其是成本和效能方面。 如果您需要價格低廉的無線電,同時沒有進階 FPGA 或寬頻寬的需求,建議您選擇 NI USRP 290x 或 Ettus Research B200mini。如果您需要最寬的頻寬以及高達 7.2 GHz 的頻率,則最適合您的選擇可能是 NI Ettus USRP X410。 上述兩者僅為舉例說明,此外仍有其他許多選擇。 以下的圖 15 提供所有型號的完整細節。

圖 4: USRP 2901 與 USRP B200mini 低 SWaP-C SDR

如果需要最高 7.2 GHz 的頻率,NI Ettus USRP X410 可能是最合適的選擇。如果您要的瞬間頻寬必須越大越好,NI Ettus USRP X440 可能符合您的需求。除了這些範例之外,還有許多其他選擇;圖 16 列舉所有機型的完整細節。

圖 5:Ettus USRP X440 採用直接取樣收發儀架構,每通道頻寬最高 1.6 GHz

獨立 SDR 或主機連線 SDR

USRP 屬於電腦週邊,用途是進行軟體與電磁頻譜連線。第一代 USRP 推出後,已經陸續發展出許多用途,許多用途更要求內建嵌入式處理器。如果您的應用會讓 SDR 從集中控制系統實際分散或是獨立部署,便可能需要這種獨立式配置。如果獨立式配置是重要條件,您需確認 Xilinx Zynq 多處理器系統單晶片 (MPSoC) 或 RF 系統單晶片 (RFSoC) 是否夠用,抑或必須使用強大的 Intel X86 機載處理器。表 1 說明各種機型及其內建處理器的分析;如需深入了解,請參閱 USRP 規格文件。

| 無線電型號 | 內建處理器 |

|---|---|

| USRP N320、USRP N321、USRP N310 | Xilinx Zynq 7100 MPSOC |

| USRP E31X | Xilinx Zynq 7020 MPSOC |

| USRP E320 | Xilinx Zynq 7045 MPSOC |

| NI Ettus USRP X410、USRP X440 | Xilinx Zynq Ultrascale+ RFSOC ZU28DR |

| USRP-2974 | Intel Core i7 6822EQ (2 GHz 四核心) |

表 1:可獨立運作且內建處理器的 USRP 型號

圖 6: 內建 Intel Core i7 的 USRP 2974 獨立式 SDR

裝置強化,因應嚴苛環境

大多數 USRP 的使用場所都是在實驗室內,但某些應用會需要在戶外或更嚴苛的環境進行作業。如果您的應用需要更廣的作業溫度範圍,或是通風散熱的方式無法滿足應用需求,您可能需要考慮選用 Ettus Research 品牌的嵌入式系列。此外,Ettus Research 品牌也提供多種選擇讓您設定 USRP B205mini,利用具有低 SWaP 作業特性的工業級鋁製機殼組件,即可擁有更廣的作業溫度範圍。 或者,如果您有極端環境作業的需求,我們也很樂意向您推薦 NI 經驗豐富的裝置強化合作夥伴;如有這方面的需求,請與我們聯絡。

圖 7: 嵌入式系列,USRP E320

多通道同步化功能

許多應用需要多重輸入/多重輸出 (MIMO) 配置,以及不同程度的同步化。某些 MIMO 系統只需要 ADC 和 DAC 有共享時脈即可,其他系統則需要將每個通道鎖定為常用時脈,同時還需要局部震盪器來進行完整的相位同調作業。

常見的 MIMO 應用為具有空間多工的通訊。由於這類應用只需要時脈同步化,而大部分具有外部 10 MHz 參考時脈的 USRP 已足夠應付。 這類系統的其中一例,是由布里斯托大學與隆德大學所建立,當時,這兩所大學運用 SDR 架構的 Massive MIMO 系統打破了無線頻譜效率世界紀錄。 這類用途所用的系統包含內建 FPGA 的 NI USRP Software Defined Radio 裝置。

圖 8:內建 LO 分配介面的 USRP N320 與 N321

若完整的相位同調作業是必要條件,可以考慮下列幾個選項。如果需要最多四個接收專用通道,可以安裝配備兩個 TwinRx 子卡的 Ettus Research USRP X310,用於共用 LO 並以相位同調方式進行作業。如果必須用到四個以上的通道,則可考慮使用 Ettus Research USRP N320 與 N321 (如圖 8 所示) 或 NI Ettus USRP X440。USRP X440 採用直接取樣中頻 (IF) 架構,因此,在最多八個傳輸通道與八個接收通道共用取樣時脈就能做到同步作業。另外,USRP X440 也支援與外部提供的參考時脈訊號進行多裝置同步。

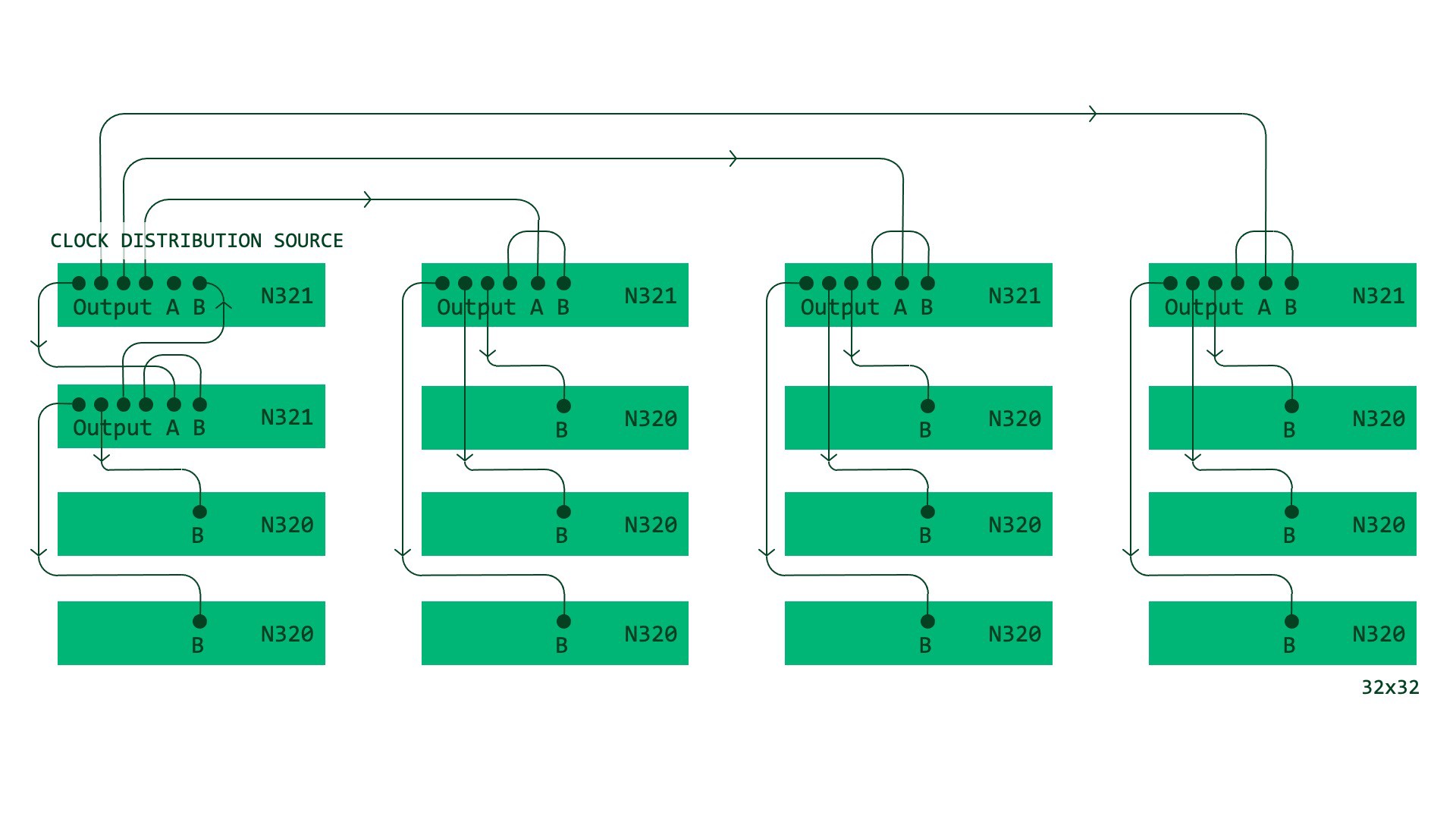

USRP N321 內建 LO 分配硬體,最高能同時進行 128 x 128 相位同調作業:圖 9 以 32 x 32 配置為例。

分散式多無線電同步化

在某些應用中,需要將分散各處的無線電進行同步化。在這種情況下,要進行完整的相位同調作業就相當不容易;然而,相關人員利用 GPS 式的同步化作業,透過 GPS 授時震盪器 (GPSDO) 來獲得穩定的頻率和相位。多數 USRP 型號均內建原廠的 GPSDO。如需深入了解,請參閱「NI USRP-293x Software Defined Radio 的全域同步化與時脈授時功能」。

圖 10:內建 GPS 授時震盪器的 USRP X310

行內訊號處理與 FPGA 的相關考量要點

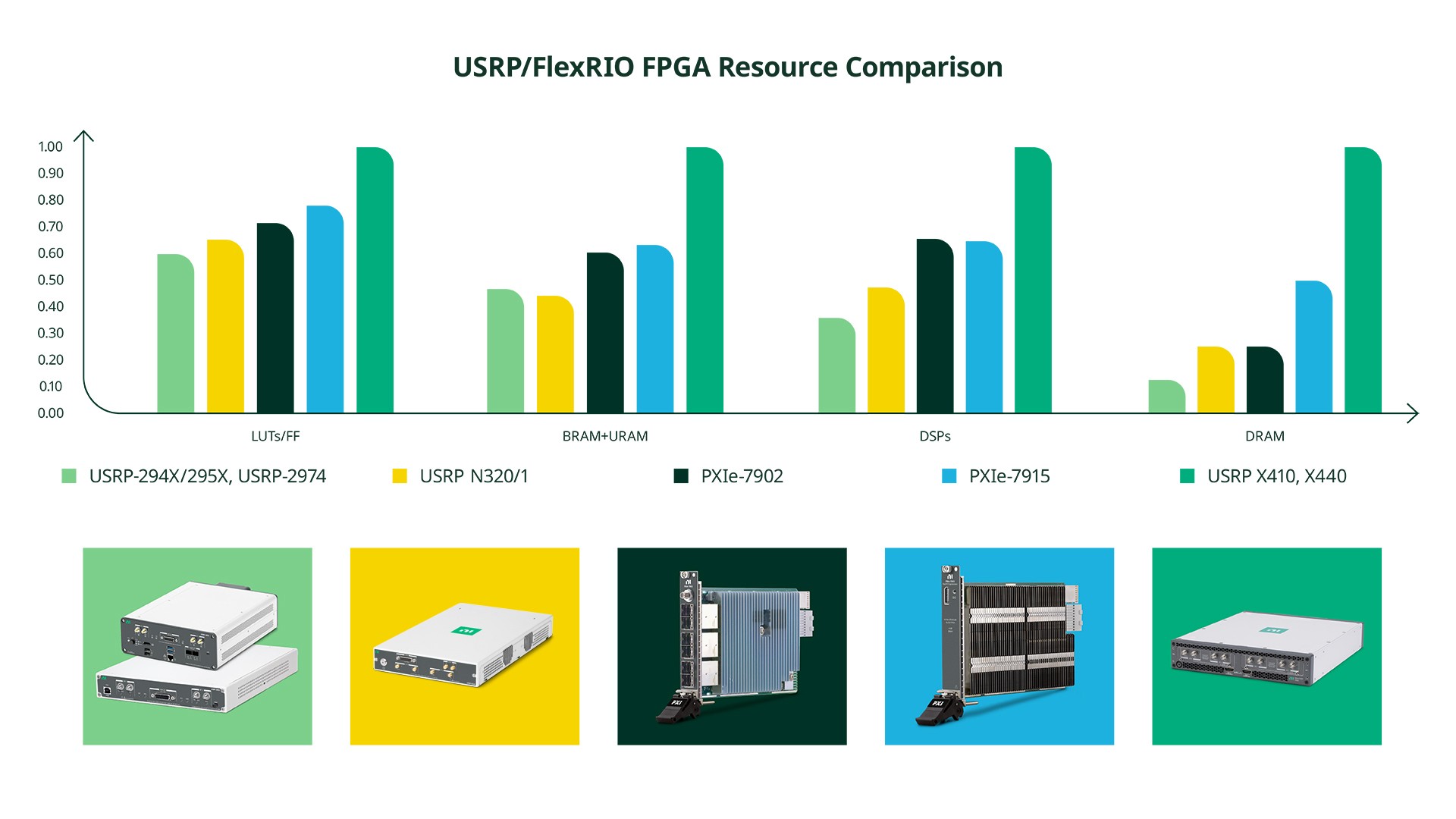

某些應用需要處理功能,而最佳選擇就是內建的 FPGA。這些應用通常擁有大範圍的訊號頻寬,或是低/精確潛時需求。在這種情況下,選擇無線電的考量重點就是程式化 FPGA 的能力。多數 USB 和 USRP B200mini 或 N210 之類成本較低的 USRP 機型,均採用較小型的 FPGA 裝置,因此沒有額外空間能加入使用者程式碼。許多較高階的無線電配備 Kintex 7 類別裝置,規格直上最先進的 Ettus USRP X410 和 X440 結合 Xilinx Zynq UltraScale+ RFSoC。採用 Xilinx Zynq 架構的裝置有額外的核心,例如內建軟決策前向錯誤修正 (SD-FEC)、多個 Arm 處理器,以及內建 ADC 與 DAC。

| USRP 型號 | 內建 FPGA |

|---|---|

| USRP N320、USRP N321、USRP N310 | Xilinx Zynq 7100 MPSOC |

| USRP E31X | Xilinx Zynq 7020 MPSOC |

| USRP E320 | Xilinx Zynq 7045 MPSOC |

| Ettus USRP X410、USRP X440 | Xilinx Zynq Ultrascale+ RFSOC ZU28DR |

| USRP 2974、USRP X310 | Xilinx Kintex 7 410T |

表 2: 具備 FPGA 功能的 USRP 比較表

圖 11:全系列 NI FPGA 產品的 FPGA 資源比較

軟體選項

程式設計功能是 SDR 的主要功能,能夠讓使用者將無線電週邊轉換成先進的無線系統。USRP 是市面上最開放且多功能的 SDR,當中提供各式各樣的軟體開發工具,讓工程師能同時在主機和 FPGA 上建立系統。

主機程式設計相關考量要點

如上面的圖 2 所示,有多種方式可以對 SDR 架構的系統主機進行程式設計。

使用 NI-USRP 驅動程式在 LabVIEW 上進行程式設計

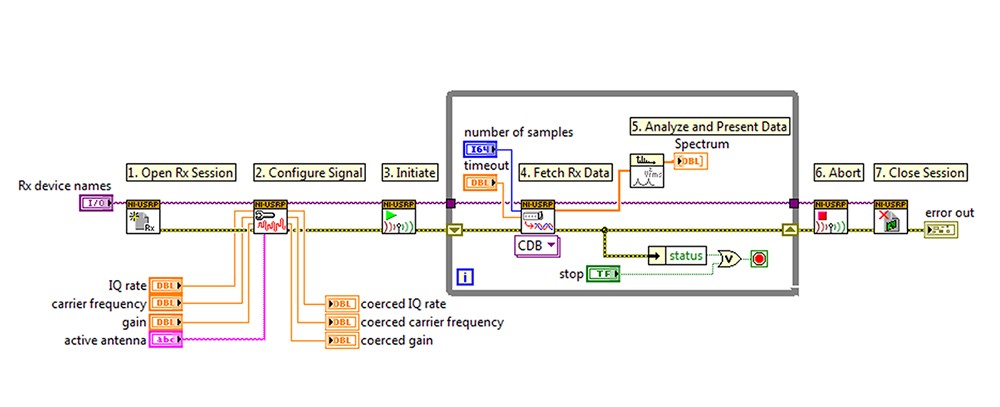

LabVIEW 是圖形化資料流程式設計環境,非常適合用來設計與執行通訊演算法。就最基本的層面而言,LabVIEW 使用 NI-USRP 驅動程式來指定 USRP 硬體配置,以及收發隨時可供主機端訊號處理且格式正確的基頻 I/Q 資料。

如果您偏好 LabVIEW 開發環境,請注意,LabVIEW 確實有提供部分的 Linux 作業系統支援,但主要是採用 Microsoft Windows 架構的工具。此外,部分 Ettus Research 品牌的 USRP 機型與配置可能不在支援範圍內;請見圖 16。

圖 12: NI-USRP 驅動程式 API 的 LabVIEW 程式方塊圖

使用開放原始碼工作流程進行程式設計:USRP 硬體驅動程式 (UHD) 和 GNU Radio

多數 SDR 使用者偏好使用以 C/C++ 和 Python 為架構的文字式開放原始碼工具流程,來程式化 USRP 硬體。所有的 NI 與 Ettus Research USRP 型號均支援 USRP 硬體驅動程式 (UHD),因此能輕鬆與開放原始碼社群開發工具整合,例如 GNU Radio。

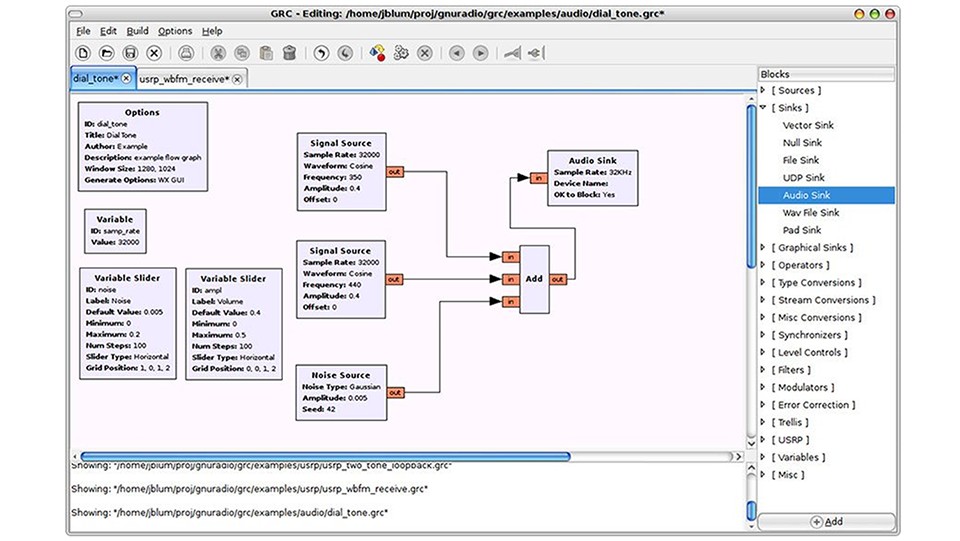

GNU Radio 是專門為 SDR 開發人員所建構的開放原始碼工具。USRP 並非唯一支援 GNU Radio 的無線電,但卻是最受歡迎且通過最多測試的無線電。如要深入了解 GNU Radio,請前往 gnuradio.org;如要查看 GNU Radio 所有現有社群共享的 IP,請前往 cgran.org。

圖 13:GNU Radio Companion 流程圖

以 MATLAB 進行程式設計

如果您偏好使用 MATLAB 工具來進行程式設計,則有數種 USRP 型號支援 MathWorks Communications Toolbox™。支援的型號包含 B200、B200mini、X300、N200 以及 N300 系列。此外,工程師也可以使用 MATLAB 指令碼節點,直接將 MATLAB 程式碼嵌入 LabVIEW。

MathWorks 也提供 Wireless Testbench,這項工具能運用 USRP 軟體定義無線電裝置的 FPGA,因此可以提供智慧型訊號擷取與硬體重新取樣等功能。這項支援使用者指定特定波形的特性,用於觸發訊號擷取並分析相關資料。

FPGA 程式設計相關考量要點

許多 USRP 配備大型 FPGA,可用容量充足,可供使用者根據其用途嵌入行內訊號處理功能。如同硬體介紹部分所述,部分 USRP 配備 Xilinx Zynq SOC 裝置,有些則採用如 Kintex 7 之類的傳統 FPGA 結構。在 USRP 存取 FPGA 的方式有兩種:LabVIEW FPGA 以及 RF 網路晶片 (RFNoC) 架構。

有別於多數 FPGA 開發機板或 COTS FPGA 機板,USRP 採用常見的 FPGA 架構,可提供較高級的抽象化功能。如此,在從最基本的 FPGA 機板支援組合建立 FPGA 式系統時,可減少相關流程的複雜性。

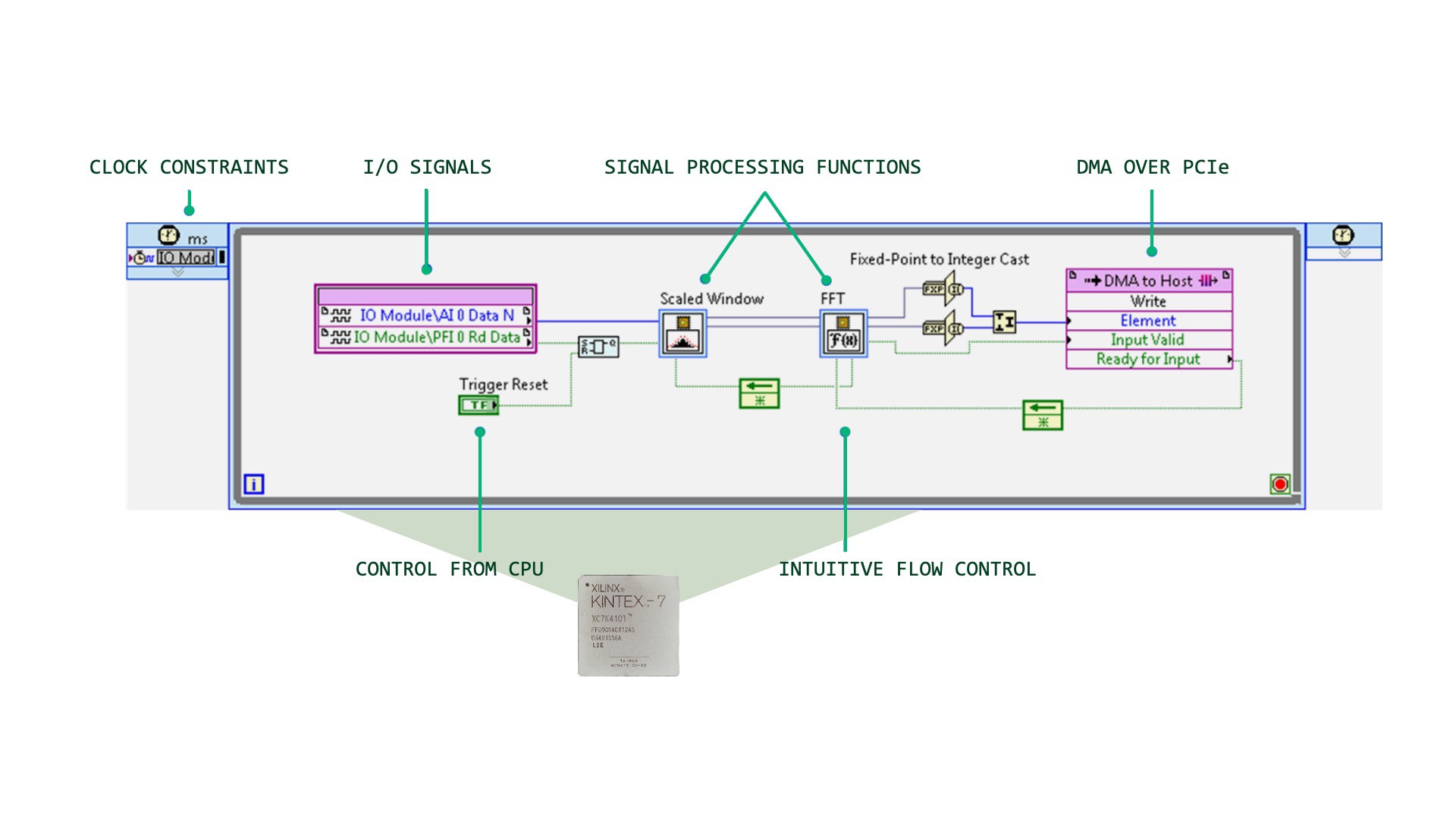

LabVIEW FPGA

LabVIEW FPGA 是 LabVIEW 的擴充外掛程式,可供使用者在 NI USRP RIO 裝置上以圖形化方式進行 FPGA 的程式設計。 雖然使用者必須熟悉諸如定點數學與時脈邏輯等 FPGA 概念,但 LabVIEW 提供了扼要的硬體與資料介面,並且簡化了暫存器設定與資料遷移作業。LabVIEW FPGA 的其中一項優勢,就是能透過一致的開發工具鏈,同時程式化主機和 FPGA。

您有想善加運用的舊款 IP 嗎?LabVIEW FPGA 可以透過 Component Level IP (CLIP) 節點匯入外部 VHDL 或 Verilog,並且允許匯入非 LabVIEW IP。此外,LabVIEW 還提供 Xilinx Vivado 專案匯出功能,可讓專業使用者直接在 Vivado 工具中進行作業。

如果您選擇使用 LabVIEW FPGA 做為主機程式設計的工具,請注意,此工具僅支援 Windows 架構的作業系統。 多數 Ettus Research 裝置 (例如 USRP N300 與 USRP E300 系列) 並不受 LabVIEW 或 LabVIEW FPGA 支援。請見圖 16 的完整清單。

圖 14:簡易 LabVIEW FPGA 程式方塊圖

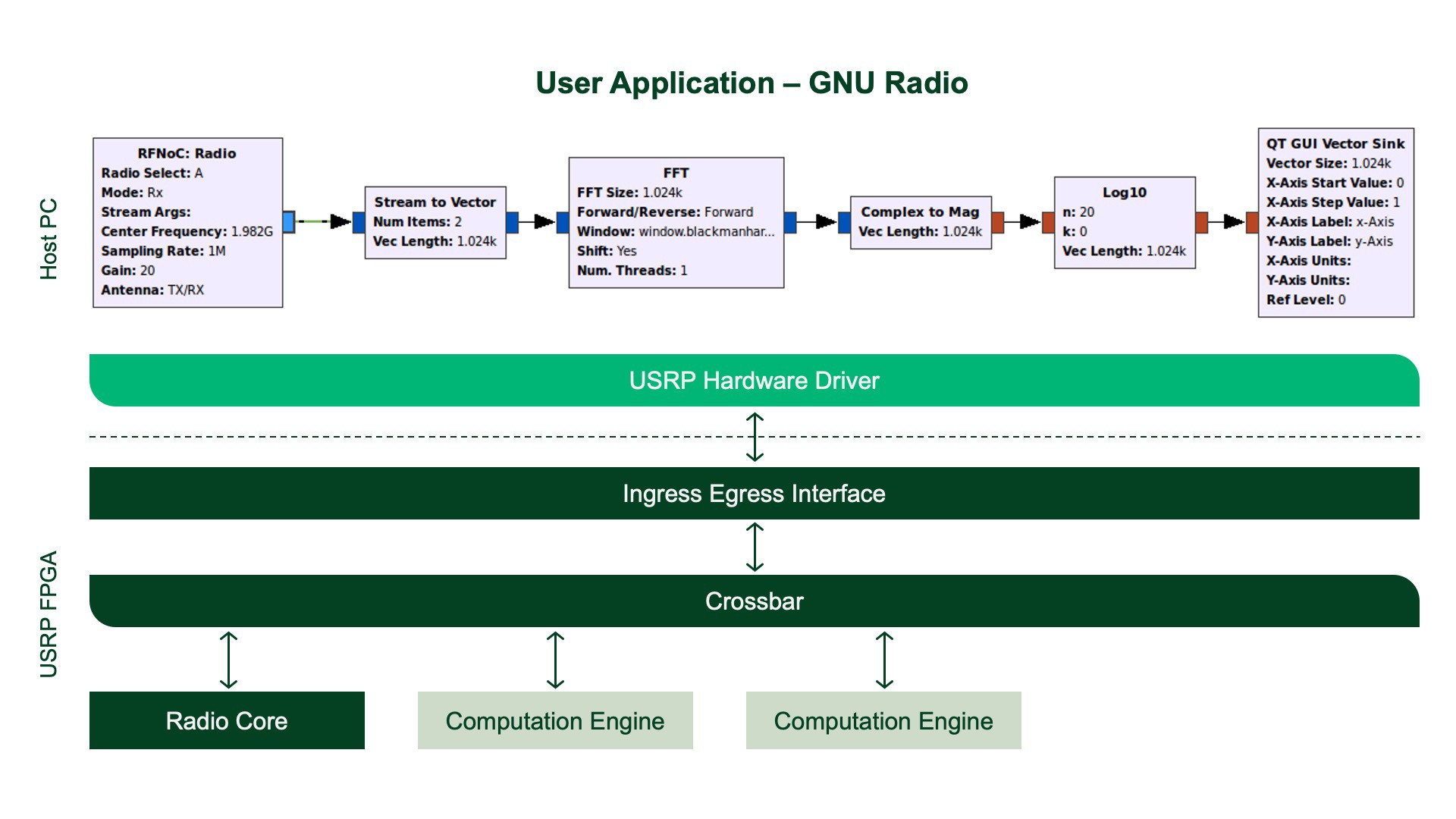

RF 網路晶片 (RFNoC) 架構

如果是開放原始碼 USRP 使用者,建議透過 RFNoC 架構的方式來程式化 FPGA。 RFNoC 與 LabVIEW FPGA 同樣屬於資料介面與指令抽象化架構,能簡化將 IP 加入 USRP 的作業,而不需要從頭重建整個 FPGA 機板支援組合。其運作方式可從名稱看出一二,也就是資料會以壓縮標頭網路封裝的形式,從無線電流經 FPGA。RFNoC 的核心架構是交錯器介面,可讓使用者直接將新的 IP 插入交錯器,再將資料路由至其他 IP 區塊,或是與主機來回路由資料。此網路交錯器設計免除了與主機之間來回傳送資料與指令的繁複作業。

若選擇在 Vivado 使用 RFNoC 編寫 USRP 的 FPGA 程式,可以根據用途考慮 USRP X300 系列、USRP E300 系列、USRP N300,以及 Ettus USRP X410 或 X440。深入了解如何使用 RFNoC、UHD 與 USRP N300 裝置製作多通道無線通訊系統原型。

圖 15: 整合 GNU Radio 的 RFNoC 概念程式方塊圖

| 類型 | NI USRP 型號 | NI Ettus USRP 型號 | #Tx | #Rx | 頻率範圍 | BW | LabVIEW | LabVIEW FPGA | OSS-UHD | OSS-FPGA |

|---|---|---|---|---|---|---|---|---|---|---|

| 獨立式、具備 FPGA 功能、高效能 | USRP X440 | 8 | 8 | 30 MHz 至 4 GHz | 1.6 GHz | — | ||||

| USRP X410 | 4 | 4 | 1 MHz 至 7.2 Ggz | 400 MHz | ||||||

| 不適用 | USRP N320、USRP N321 | 2 | 2 | 3 MHz 至 6 GHz | 200 MHz | — | ||||

| 不適用 | USRP N310 | 4 | 4 | 10 MHz 至 6 GHz | 100 MHz | — | ||||

| USRP-2974 | 不適用 | 2 | 2 | 10 MHz 至 6 GHz | 160 MHz | |||||

| 主機連線、具備 FPGA 功能、高效能 | USRP-2944 | USRP X310 + UBX | 2 | 2 | 30 MHz 至 6 GHz | 160 MHz | ||||

| USRP-2945 | USRP X310 + TwinRX | 0 | 4 | 10 MHz 至 6 GHz | 80 MHz | |||||

| USRP-2954 | USRP X310 + UBX + GPSDO | 2 | 2 | 30 MHz 至 6 GHz | 160 MHz | |||||

| USRP-2955 | USRP X310 + TwinRX +GPSDO | 0 | 4 | 10 MHz 至 6 GHz | 80 MHz | |||||

| 低 SWAP 獨立嵌入式 | 不適用 | USRP E310 / E312 / E313 | 2 | 2 | 70 MHz 至 6 GHz | 56 MHz | — | — | ||

| 不適用 | USRP E320 | 2 | 2 | 70 MHz 至 6 GHz | 56 MHz | — | — | |||

| 低 SWAP 平價 USB 連接 | 不適用 | USRP B200mini / B205mini | 1 | 1 | 70 MHz 至 6 GHz | 56 MHz | — | — | ||

| USRP-2900 | USRP B200 | 1 | 1 | 70 MHz 至 6 GHz | 56 MHz | — | — | |||

| USRP-2901 | USRP B210 | 2 | 2 | 70 MHz 至 6 GHz | 56 MHz | — | — | |||

圖 16:NI 與 Ettus Research USRP 機型對照表

結論

SDR 是功能強大的工具,非常適合用於無線研究、設計、原型製作與部署。由於產品選擇眾多,因此需要謹慎考量諸多因素,才能選出適合您應用的無線電。然而,只要審慎評估本技術文章所述的各種軟硬體因素,您就一定能使用到市面上最受歡迎的開放式 SDR。

後續步驟

Embedded Coder® 與 MATLAB® 是 The MathWorks, Inc. 的註冊商標。

Communications Toolbox™ 與 HDL Coder™ 是 The MathWorks, Inc. 的商標。