量測,從觸發開始

綜覽

內容

就示波器這類儀器而言,主要需求之一就是快速、可靠地偵測並觸發已知訊號流中的重點事件。如果能夠及時偵測特定事件,就能盡早針對電子設計過程中產生的問題進行除錯,進而縮短開發與製造的測試時間。

這點對於示波器廠商而言相當重要。為了讓使用者快速區分常見與不常見的訊號條件,許多廠商會提供 100 多個預定義的觸發器。這樣雖然增添了靈活性,但選出正確的觸發器本身比實際擷取訊號更為困難,因為觸發器具有各式各樣的類型、速度、頻寬、延遲與軟體等條件,而每個觸發器都要在靈活性與空滯時間之間做權衡。清楚了解觸發器的類型及各自的權衡條件,有助於辨別出最佳的觸發方式,進而大幅提升成功觸發事件的機率。

示波器的觸發器效能取決於兩方面:

- 觸發器靈活性表示能輕鬆定義觸發臨界或條件,進而調整受測訊號的條件以提升效率的程度。多數示波器提供廠商定義的各種觸發功能,其中設定了準位或寬度等參數的最低值,但是沒有提供客制化這些功能的方法。

- 觸發器停滯時間是指示波器在兩次訊號擷取之間,無法偵測到觸發器的時間長度。這意味著重點事件若發生在這段空滯時間內,就會錯過觸發條件。觸發器空滯時間是所有觸發器架構的固有特性,但是我們可運用幾種方法和技術,將這段空滯時間縮到最短。許多示波器廠商會提供軟體式觸發器來增加靈活性,但因為需要後處理,這類觸發器需要較長的空滯時間,並不適合極少見或發生頻率低的事件。

傳統觸發模式

邊緣觸發 (從上升邊緣或下降邊緣訊號轉變時開始擷取訊號) 是目前最常見的示波器觸發模式。大部分簡單的除錯與測試功能都是透過邊緣觸發器進行處理,但多數情況會需要更複雜的觸發情境,才能區分特定形狀的訊號或連續多種形狀的訊號。示波器通常也包含更進階的觸發選項,這些選項提供更優異的靈活性來擷取 I2C 或 SPI 等序列協定以及進階事件和訊號特性,例如抖動、矮波、寬度、轉換率以及超時等。

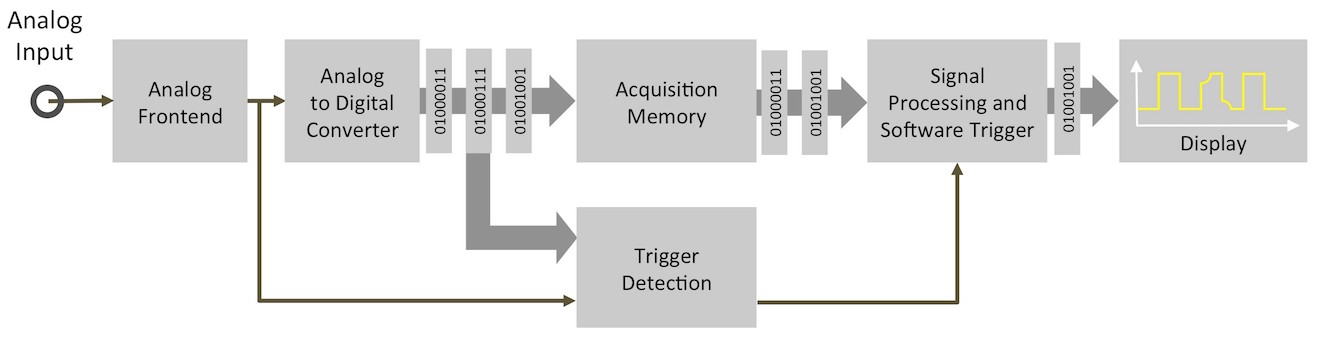

圖 1. 根據數位訊號處理顯示的示波器程式方塊圖。示波器的擷取更新速率與空滯時間,取決於擷取記憶體與訊號處理單元。

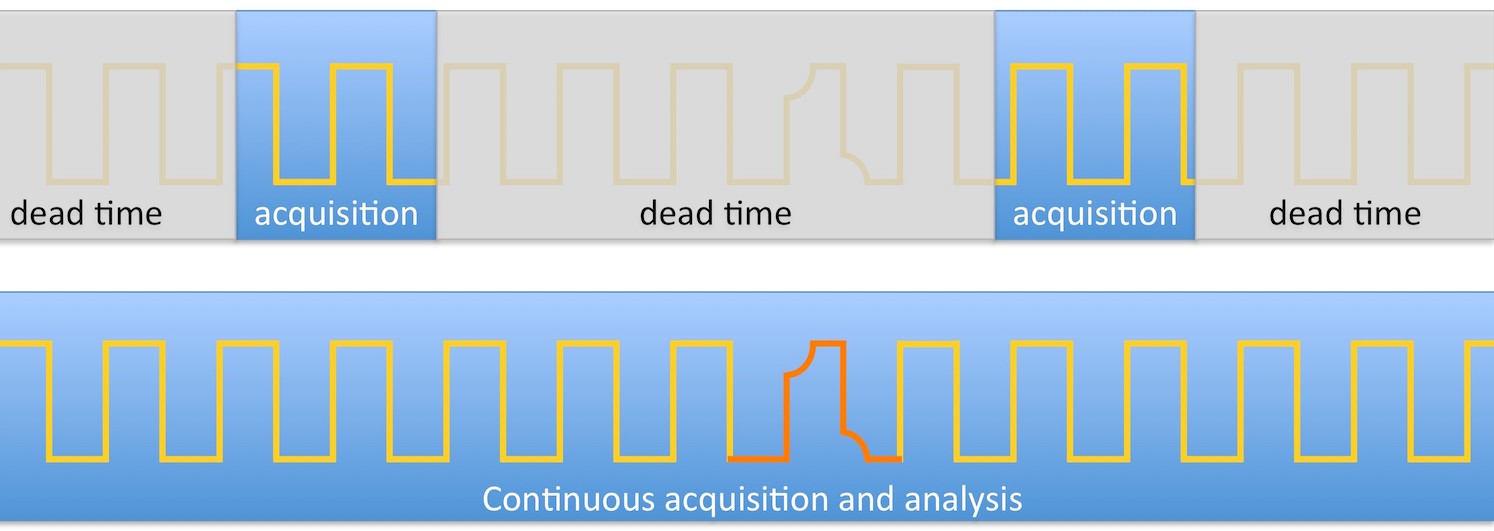

許多觸發條件均在硬體中執行,但更為複雜的觸發選項與訊號認證,通常卻是在軟體中執行,就像圖 1 所示。軟體觸發器具有最佳的靈活性,但是也增加了必要的資料傳輸與處理時間,而示波器在這段時間內無法偵測到新的觸發器,就像圖 2 所示。系統無法偵測到觸發器的時間稱為「空滯時間」,這段時間往往比實際擷取資料記錄的時間長,也就是說,示波器觸發系統的空滯時間可能超過 95%。這使得偵測到極少見或發生頻率低的事件變得更為困難,進而導致測試時間延長。更糟的是,使用者可能會誤以為預期事件沒有發生,因為預期事件發生的機率太低,以至量測過程中沒有偵測到。

圖 2. 這張圖顯示了傳統示波器的波形擷取與分析過程,波形擷取 (上) 與連續處理 (下) 之間有空滯時間。

如果示波器的可用觸發器或訊號分析功能無法滿足工作需求,使用者就只能擷取較長的波形片段,並將這些片段的原始資料下載到 PC,以進行後處理並找到特定事件。不過這樣會增加整體系統設計的複雜度,同時由於資料傳輸延遲與資料處理所需的時間,導致整個測試時間延長。

建立觸發器,無需權衡

多數軟體式或智慧型觸發選項都能滿足電路的設計與測試需求,但是如果不將極少見的事件迅速隔離或修正,這些事件往往會導致產品開發時間拉長。由於多數示波器觸發功能的侷限性,使用者只能使用廠商所提供的功能。

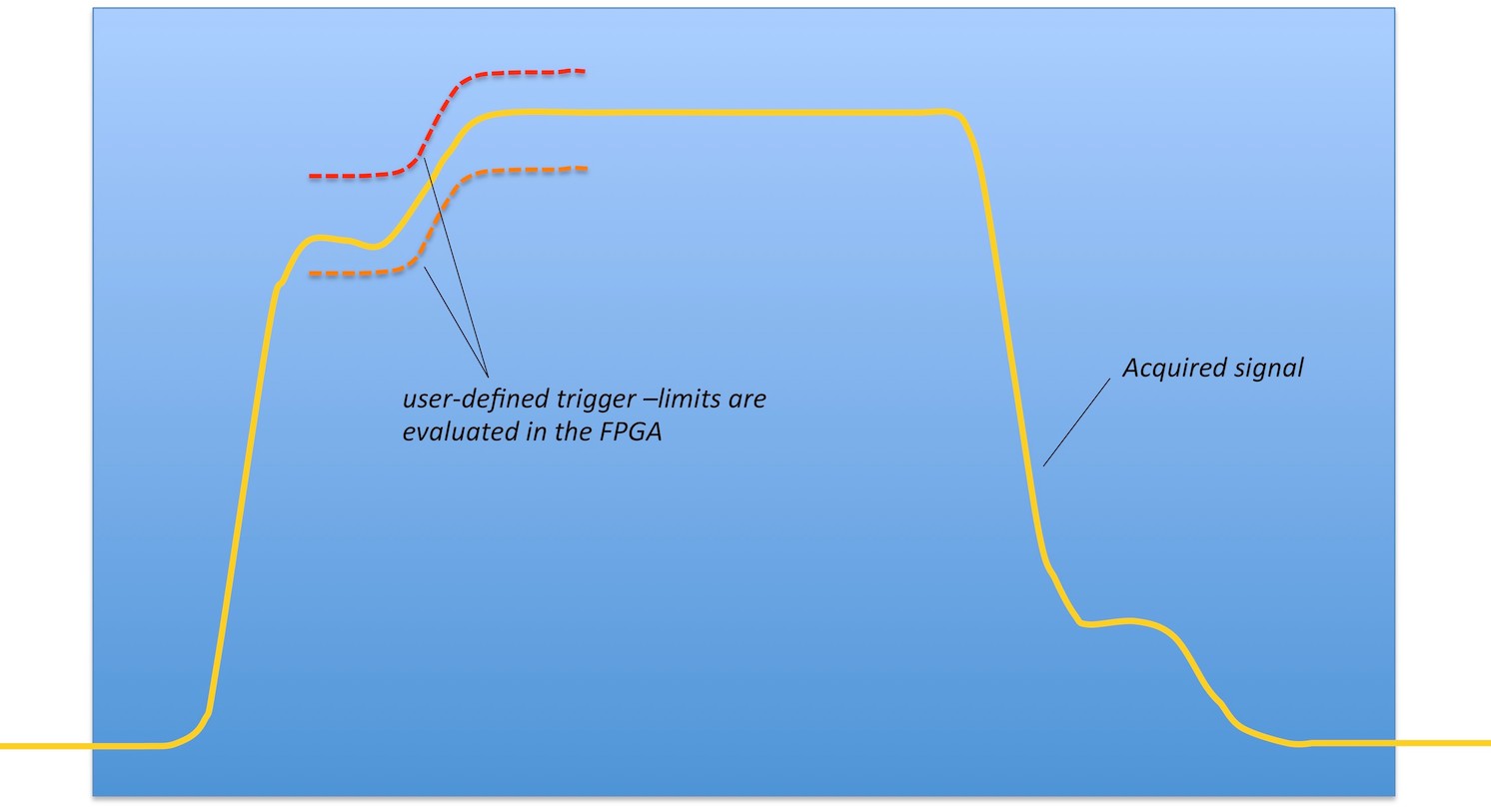

如果使用者能在示波器內執行自行開發的演算法,就可以針對特定工作客制化儀器功能,而不受限於廠商所定義的功能。例如,使用者可以針對特定應用自行定義觸發條件,以專門擷取某個訊號條件,他們就不需要在 PC 上進行資料後處理,進而大幅縮短測試時間 (如圖 3 所示)。

FPGA 是為示波器提供行內資料處理,以及重新程式設計演算法靈活性的關鍵技術;本質上而言,FPGA 算是可程式化晶片,能夠透過真正的平行機制,高速執行客制化訊號處理並控制演算法。FPGA 的靈活性讓使用者能夠修改或新增特定的觸發演算法,同時高傳輸率的處理功能可在擷取過程中即時分析資料樣本,無需再進行後處理。如此可以避免空滯時間、避免錯過觸發,並幫助使用者能更快偵測到極少見的事件。

使用者定義觸發器的一個例子,就是偵測不符合標準觸發器定義的訊號波形或準位轉換,例如圖 3 所示的訊號。這種數位訊號具有非單調邊緣,可能是訊號反射或受測電路的電源供應器故障所引起的。標準邊緣或寬度的觸發器不會偵測這種預期外的訊號,而且基本上也不可能以常規手段來進行偵測。我們需要建立新的觸發器,才能準確且連續地擷取這種事件。我們可以開發軟體觸發器來解決這種情況,然而這種方法的觸發器空滯時間較長,因此無法快速偵測到極少見的事件。或者,我們可以採用使用者可程式化的 FPGA 來提供多個視窗觸發器,當所有視窗觸發器同時偵測到有效觸發條件時,就會將擷取的樣本點與遮罩進行比對,從而產生組合觸發器來擷取訊號。

由於 FPGA 可連續即時地評估訊號,因此示波器可以擷取單一事件,也可以擷取連續事件,而且兩次擷取之間不會有空滯時間。

圖 3. 透過使用者定義的觸發器擷取特定訊號轉換;該功能在可重設示波器的 FPGA 中執行。

可重設示波器

多年來,測試工程師都在使用 LabVIEW 等軟體工具來代替傳統箱型儀器的固定式軟體,藉此自動化測試系統、分析與呈現量測結果,從而降低測試成本。這種方法具有靈活性,且運用了最新的 PC 與 CPU 技術。然而,使用者的需求往往不僅於此,他們通常需要修改儀器的量測方式,才能更妥善地因應應用需求。

傳統的現成可用儀器由廠商定義,並且只有固定的功能;而 NI 率先採用 FPGA 技術,提供更開放、靈活的儀器。因此,這款現成可用硬體綜合了雙方優勢:高品質的固定式量測技術、最新的數位匯流排整合,以及使用者可客制化的邏輯,這種邏輯不但具有高度平行的特色、能夠縮短延遲時間,還可直接銜接 I/O 以便用於行內處理。

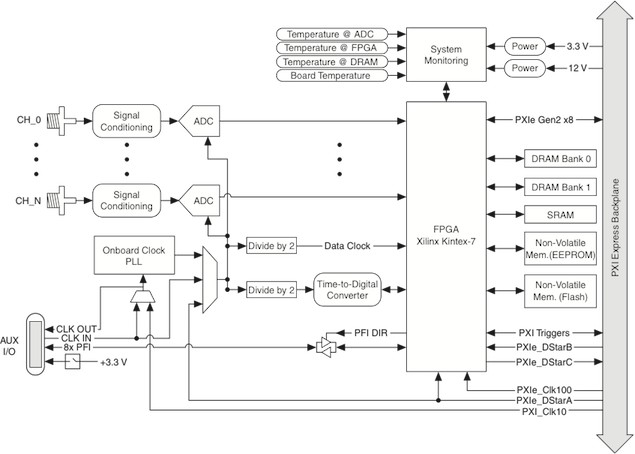

圖 4. 可重設示波器 NI PXIe-5171R 的程式方塊圖。

在過去,工程師必須深入了解如何使用 Verilog 或 VHDL 等工具進行數位硬體設計,才有辦法運用 FPGA 技術。但隨著 NI LabVIEW 軟體等高階系統設計工具的興起,FPGA 程式設計的規則也有了變化,所提供的創新技術可把圖形化程式方塊圖轉換成數位硬體電路。所有的 NI FPGA 硬體產品 (包含 NI PXIe-5171R) 皆搭載LabVIEW 可重設 I/O (RIO) 架構,其中配備強大的浮點處理器、可重設 FPGA 與模組化 I/O。LabVIEW RIO 架構可在設計進階的控制/監測/測試應用時,簡化開發作業,同時縮短上市時間。透過 LabVIEW,使用者可以擴充儀器的功能,例如客制化觸發器或額外的時序或控制訊號。使用者也能在以軟體設計的儀器的 FPGA 中,執行自行開發的演算法,並重新定義硬體功能來進行完全不同的工作。例如,示波器可以變成即時頻譜分析儀、暫態記錄器、協定分析器、RF 接收儀或者其他儀器。

在測試系統中,儀器的採購與維護成本所佔的比例相當高,如今所需儀器數量減少,自然有助於降低設備成本。這一點對於需要長時間 (超過 10 年) 使用測試與儀器功能而言特別有幫助,例如軍用或航太測試系統。這類應用領域往往需要重新建立現已淘汰 (產品生命週期結束) 的舊儀器功能。

可重設儀器非常適用於這類應用,因為透過重新程式設計,使用者即可模擬舊儀器的功能。由於測試系統軟體不需大量重新程式設計與重新認證,就能與新儀器配合,因此可協助使用者節省成本。

這類儀器的其中一例就是 NI PXIe-5171R 可重設示波器,該儀器使用 Xilinx Kintex-7 FPGA 即時處理擷取自 8 個輸入通道的樣本。圖 4 說明使用者可程式化的 FPGA 如何整合至資料路徑中,並提供對儀器控制與時序訊號的存取功能。

結論

由於缺乏靈活性與即時分析能力,傳統的示波器觸發方法很難用於擷取極少見或複雜的事件。而新的觸發方式可運用 FPGA 技術來定義客制化觸發功能,進而滿足複雜的觸發條件,並且即時處理與分析訊號。