NI FlexRIO 前端模組開發組合

綜覽

NI FlexRIO 前端模組開發組合 (MDK) 為開發客制化前端模組提供必要工具,並可搭配使用 NI FlexRIO 產品 (如 NI PXI-797xR)。此篇技術文件將詳細說明 NI FlexRIO 前端模組開發組合 (MDK) 的內容物,並概略呈現前端模組開發過程的高階技術。若要進一步了解詳情,請聯絡您的本地 NI 業務代表。

內容

MDK 內容物

NI FlexRIO 前端 MDK 包含所有必要資訊,讓使用者能開發客制化前端模組。 內含完整的說明文件,詳細解說 NI FlexRIO 的軟硬體介面。該組合並提供入門檔案與範例。客戶將收到機殼、PCB 配置檔案,與相關機械繪圖。MDK 使用者亦將享有 NI FlexRIO MDK 的相關支援,並獲得 NI 研發部門的技術支援。 下列為 MDK 內容物的詳細清單:

說明文件

- NI FlexRIO 前端模組開發組合使用者手冊

- MDK 最終使用者授權協議

- MDK 資料表

軟體

- 前端模組範例支援檔案

- I2C 存取範例 VI

硬體

- 3 組空白的前端模組機殼

- 1 組分窗式 (Windowed) 前端模組機殼,適用於針測電路 (Probing circuitry)

設計檔案

- PCB 輪廓機械繪圖

- 介面卡邊緣接頭機械繪圖

- 前端模組人機介面機械繪圖

特殊支援資源

- NI 研發部門提供的 NI FlexRIO MDK 支援資源與技術協助

- NI 研發部門可提供電路簡圖/配置共 1 小時的審閱時間

使用 MDK 建立客制化前端模組

建立客制化前端模組的進階步驟如下:

1.設計並建立前端模組—電路簡圖、配置與組件等

MDK 包含所有必要的繪圖、配置檔案與相關說明,所建立的 PCB 將可透過機械或電子方式,介接 NI FlexRIO FPGA 模組。檔案並提供標準的 .dxf 與 .dwg 格式,可搭配使用客戶自己的 PCB 設計工具。

2.註冊 IO Module ID 並進行 ID EEPROM 的程式設計

進行 EEPROM 程式設計的相關說明,均詳細記載於 NI FlexRIO 前端模組開發組合使用者手冊中。

3.建立前端模組定義檔 (.fam)

定義檔可讓 LabVIEW 開發環境顯示該模組,並可定義模組的特殊電子特性。MDK 亦提供說明與範例檔案。

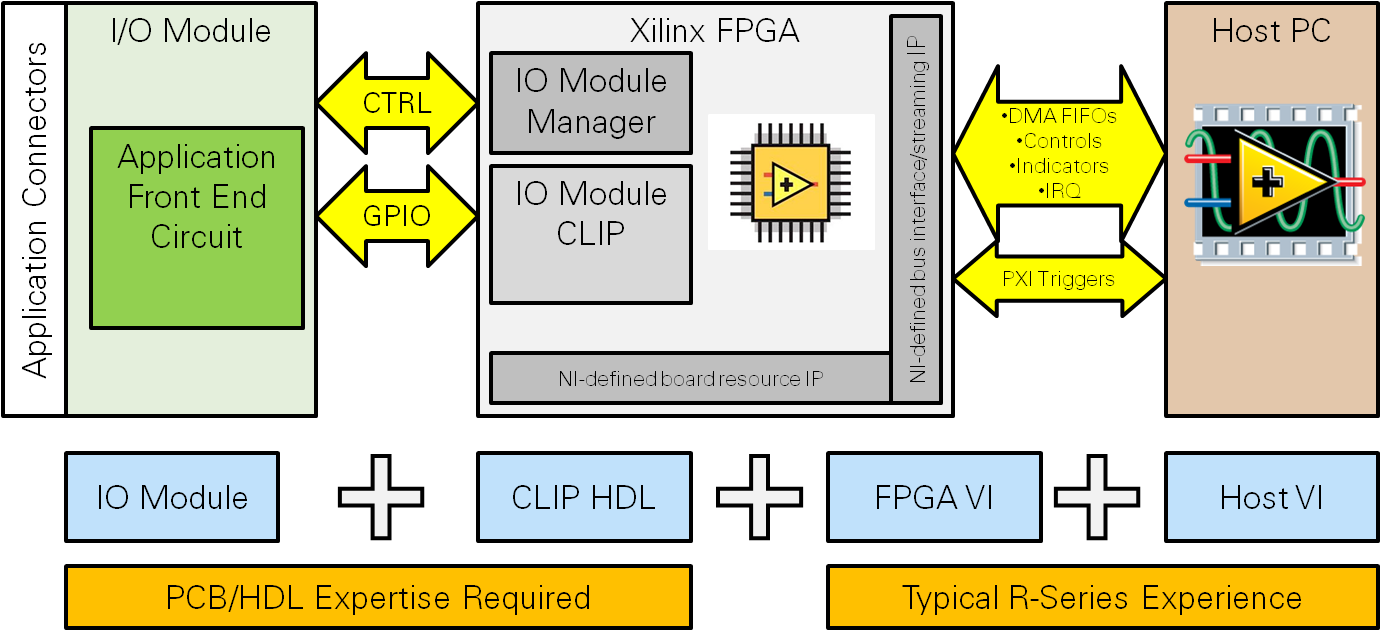

4.建立前端模組 CLIP (HDL 與 XML)

前端模組的 Component-Level IP (CLIP) 與 XML 描述,將可針對硬體到 LabVIEW 的獨立輸出/入埠,建立映射作業。MDK 則包含這些檔案的說明文件與範例。

5.針對前端模組與 CLIP 撰寫 LV FPGA VI

在定義所有的介面之後,則可使用 LabVIEW FPGA 與客制化的前端模組通訊,並接著開發系統的其他部分。MDK 中亦包含 FPGA 設計 VI 的範例與說明文件;相關範例將透過 PXI 匯流排,使用 DMA 與範例主程式進行通訊。

使用者與團隊必須具備下列技術才能順利開發前端模組:

- PCB 設計—電路簡圖與配置

- PCB 製作/組裝

- HDL 開發/整合

- LabVIEW 與 LabVIEW FPGA 開發

前端模組電子介面

1. Virtex-5 架構式 NI FlexRIO

前端模組介面將可凸顯 Virtex-5 FPGA I/O 的完整功能與彈性,並可針對多樣的前端模組應用,提供通用的介面。 此介面包含固定式與可設定的電力軌 (Power rail),還有已定義完畢的控制訊號,適用於前端模組的偵測與識別作業。 以下為 NI FlexRIO FPGA 與前端模組之間的實體介面摘要。

電力軌 (Power rail)

- +3.3V、+12V 導軌

- 可設定的 VccoA 與 VccoB 導軌,適用於 FPGA I/O 組間與前端模組 (設定為 1.2、1.5、1.8、2.5、3.3)

通用 FPGA I/O

- 132 個單端點通道 (可設定為 66 個差動偶合),可連接 Virtex-5 FPGA 至前端模組

- FPGA I/O 組間 (透過 VccoA and VccoB 供電)

- 軌道阻抗:單端點 50 Ohm;差動端點 100 Ohm

時脈

- 從前端模組至 NI FlexRIO FPGA,共有 2 組總體時脈輸入

- 1 組 3.3V LVTTL 輸入

- 1 組 2.5 LVDS 差動偶合輸入

控制

- 共 2 組 IO Module 將說明交握訊號至 NI FlexRIO FPGA (Present 與 Power good) 的狀態

- I2C 匯流排可適用於 IO Module 的 EEPROM 識別

2. 7 系列架構式 NI FlexRIO

前端模組介面將可凸顯 7 系列 FPGA I/O 的完整功能與彈性,並可針對多樣的前端模組應用,提供通用的介面。 此介面包含固定式與可設定的電力軌 (Power rail),還有已定義完畢的控制訊號,適用於前端模組的偵測與識別作業。 以下為 NI FlexRIO FPGA 與前端模組之間的實體介面摘要。

電力軌 (Power rail)

- +3.3V、+12V 導軌

- 可設定的 Vcco 導軌,適用於 FPGA I/O 組間與前端模組 (設定為 1.2、1.5、1.8、2.5、3.3)

通用 FPGA I/O

- 136 個單端點通道 (可設定為 68 個差動偶合),可連接 7 系列 FPGA 至前端模組

- FPGA I/O 組間 (透過 Vcco 供電)

- 軌道阻抗:單端點 50 Ohm;差動端點 100 Ohm

時脈

- 從前端模組至 NI FlexRIO FPGA,共有 6 組總體時脈輸入

- 1 組 3.3V LVTTL 輸入

- 1 組 2.5 LVDS 差動偶合輸入

控制

- 共 2 組 IO Module 將說明交握訊號至 NI FlexRIO FPGA (Present 與 Power good) 的狀態

- I2C 匯流排可適用於 IO Module 的 EEPROM 識別

前端模組機械說明

標準的 NI FlexRIO 前端模組設計,即為 1 組能完整嵌入至金屬機殼的 PCB,並能固定於 NI FlexRIO FPGA 模組的表面。 雖然某些應用可能需要其他尺寸,但 NI 仍建議所有的前端模組均能符合上述機械需求。若超出上述條件之外的作業,則可能需要另外的機殼/固定解決方案。

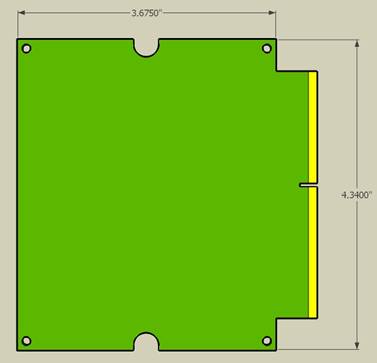

前端模組的 PCB 規格

前端模組的 PCB 若不含邊緣的接頭範圍,則寬度約為 9.1 公分 (3.6 吋),長度約為 10.9 公分 (4.3 吋)。 而兩邊的前端模組電路各可達約 35.56 平方公分 (14 平方吋) 的面積。 推薦使用的 PCB 厚度為 0.157 公分 (0.062 吋)±10%。 而 PCB 另外一面可供小型的被動元件使用,高度限於 0.127 公分 (0.05 吋)。[v1] NI FlexRIO FPGA 模組的介面,則是介面卡邊緣的接頭。 如此可省下所有前端模組各自使用特殊接頭的麻煩;然而,卻必須進行特定的 PCB 製作規格。介面卡邊緣接頭的配置檔案與機械繪圖,均已包含於 MDK 之中。

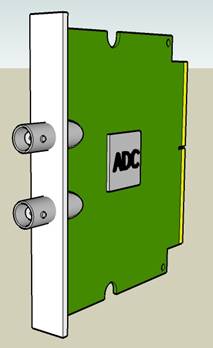

前端模組機殼

前端模組機殼為上下 2 片的貝殼式設計。而 PCB 機板接口處共有 4 組固定螺絲。 其中包含調整針腳 (Alignment pin) 與固定螺絲,可連接 NI FlexRIO FPGA 模組。

前端模組前端接頭分窗

前端模組機殼包含 1 組插槽,可銜接人機介面的接頭介面。 此人機介面為簡單的矩形金屬片,可根據所需的接頭進行客制化。 下圖則為具有 2 組 BNC 接頭的人機介面範例: