PXI 高速序列儀器簡介

綜覽

PXI 高速序列儀器能協助工程師檢驗、介接及測試高速序列協定。特定高速序列裝置 (如 PXIe-7903 和 PXIe-7902) 是專為需要高效能 FPGA 協同處理功能的工程師所設計,有助於移動大量資料與進行行內即時訊號處理。這款硬體搭載 Xilinx Kintex™ UltraScale+™ 或 7 系列 FPGA,您可以使用 LabVIEW FPGA 模組設計這款 FPGA 的程式,充分針對特定用途進行客製化與重複利用。這些儀器運用 FPGA Multi-Gigabit 收發儀 (MGT),最高支援 28.2 Gbps 的線路速率,以及最多 48 個 TX 和 RX 通道。由於這些儀器皆屬於 PXI 平台,因此能運用其時脈、觸發及高速資料移動功能,包括磁碟往返串流,以及速度最高 7 GB/s 的點對點 (P2P) 串流功能。

內容

高速序列介面的興起

高頻寬資料的需求越來越大,有線介面的介接線介面也必須同步提升時脈速率和平行機制也不斷提高。不過,若使用傳統平行資料匯流排,時脈與資料線路之間只要出現一絲偏差,就有可能威脅到介面的位元錯誤率。序列資料連結將時脈嵌入於特定差動軌跡對組的資料串流,讓時脈和資料之間不可能出現偏差,因此解決了這個問題。由於這項功能的緣故,介面的接收端必須額外加裝電子元件,另也必須針對時脈回復進行編碼;不過,這麼做就有機會大幅提高資料速率,順利因應頻寬需求。

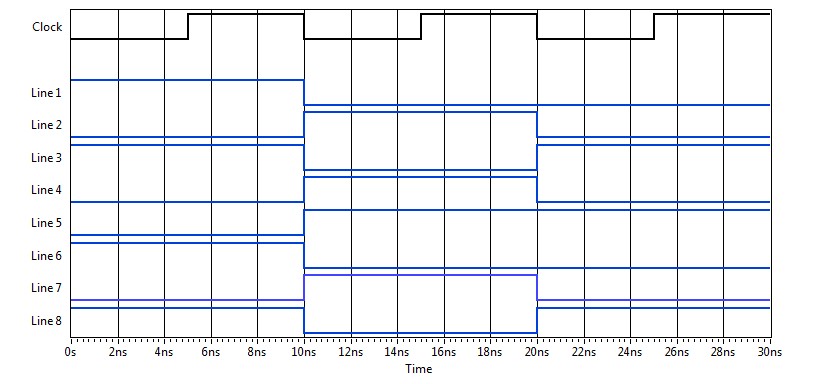

圖 1.平行時脈 (黑) 和資料 (藍) 相較於嵌入於資料中的時脈 (紅),兩者的資料頻寬相同。

現代資料通訊協定已經從平行介面發展成高速序列介面,例如 PCI Express、HDMI 和 DisplayPort 視訊標準、IEEE 1394b、USB 3.0 等等。對設計和測試工程師來說,檢驗這類介面的過程相當棘手,而且必須用到全新的測試硬體。工程師向來使用非常昂貴的示波器或位元錯誤率測試儀 (BERT) 測試實體介面的特性,另也使用特定協定專用的分析儀和產生器檢驗協定堆疊執行正確與否,以及資料傳輸/接收作業有無效率。不過,就自動化 V&V 與製造測試而言,針對序列介面測試進行過最佳化處理的硬體並不存在。示波器或位元錯誤率測試儀通常既昂貴速度又緩慢,無法驗證其適用範圍;特定協定專用的硬體則往往不夠靈活,難以整合於自動化測試系統。另一方面,特定協定專用的硬體不能重複運用於其他測試,也無法再次利用於其他受測裝置 (DUT)。

FPGA 有助於克服上述難題。現代的高效能 FPGA 通常會有數個 MGT,能搭配運用多種高速序列介面。只要結合適當的特定協定專用 IP、LabVIEW FPGA 模組的圖形化程式設計功能,以及 PXI 生態系統的優勢,就能全新打造出以軟體設計的高速儀器。

高速序列模組

|  |  |  |  |  | |

| 規格 | PXIe-6591 | PXIe-6592 | PXIe-6593 | PXIe-6594 | PXIe-7902 | PXIe-79032 |

| 線路速率 | 500 Mbps–12.5 Gbps¹ | 500 Mbps–10.3125 Gbps¹ | 500 Mbps–16.3 Gbps | 500 Mbps–28.2 Gbps | 500 Mbps–12.5 Gbps | 500 Mbps–28.2 Gbps |

| 通道數 | 8 TX/RX | 4 TX/RX | 8 TX/RX | 8 TX/RX | 24 個 TX/RX | 48 個 TX/RX |

| FPGA | Kintex 7 K410T | Kintex 7 K410T | Kintex UltraScale KU040、KU060 | Kintex UltraScale+ KU15P | Virtex™ 7 485T | Virtex UltraScale+ XCVU11P |

| DRAM | 2 GB | 2 GB | 4 GB | 8 GB | 2 GB | 20 GB |

| 主機 串流頻寬 | 3.2 GB/sec | 3.2 GB/sec | 7 GB/sec | 7 GB/sec | 3.2 GB/sec | 7 GB/sec |

| 接頭 | Mini-SAS HD | SFP+ | QSFP28 | QSFP28 | Mini-SAS HD | Mini-SAS HD |

| 佈線 選項 | 銅線或光纖 | 銅線或光纖 | 銅線或光纖 | 銅線或光纖 | 銅線或光纖 | 銅線或光纖 |

| Aux DIO | 20 SE | 4 SE | 8 GPIO | 8 GPIO | 不適用 | 8 GPIO |

表 1.PXI 高速序列儀器。

¹8 Gbps 與 9.8 Gbps 可行線路速率之間的差異。

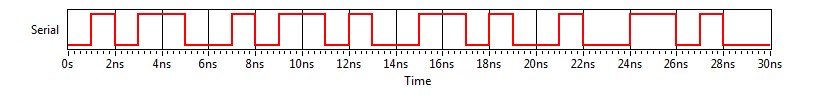

²PXIe-7903 是雙插槽模組。

連接與佈線對高資料速率與類比頻寬超過 20 GHz 的用途特別重要。PXIe-7903、PXIe-7902、PXIe-6594、PXIe-6593、PXIe-6592 與 PXIe-6591 分別提供不同的選項,適用於簡化特定用途的連接方式。這 3 款模組全數以使用者可程式化 Xilinx FPGA 為核心。

Xilinx 7 Series GTX 收發儀是這些儀器背後的關鍵技術。這類收發儀皆採用電流式邏輯 (CML),也就是一種差動介面,小幅度訊號擺動達 800 mVpp (最大額定值是 1000 mVpp),能夠減少耗電量和輻射量,以及 100 ohm 的差動 (單腳為 50 ohm) 阻抗,能夠提高資料速率,盡可能降低反射和訊號像差。此外,為盡可能提高訊號精確度,這些收發儀採用可程式化傳輸振幅,能補償較長的接線,還能夠傳輸預/後加強和自動適應接收儀等化,藉此克服有限的類比通道/接線頻寬。

所有的高速序列介面都必須要有一個按通道速率的整數公約數運作的參考時脈。為發揮最大的彈性,GTX 收發儀有一個鎖相迴路 (PLL),可以讓參考時脈增加高達 100 倍,以利達到序列資料速率。這類收發儀還有串聯轉並聯 (serial-to-parallel) 與並聯轉串聯 (parallel-to-serial) 轉換器,比例高達 80 倍,能限制 FPGA 時脈頻率,同時提高序列資料速率。再者,這款收發儀內建 8b/10b、64b/66b 與 64b/67b 編碼與解碼架構,能確保訊號轉換次數足夠用於時脈回復,避免消耗一般用途的 FPGA 資源。Xilinx 7 系列 FPGA GTX/GTH 收發儀使用者指南提供關於 Xilinx GTX 收發儀的詳細資訊。

除了提供高速序列收發儀之外,儀器上的 Xilinx FPGA 還能用於其他重要用途。這類 FPGA 執行的邏輯適用於使用中的協定,也適用於任何硬體設定以及系統資料產生、接收與移動的任何特定用途使用者邏輯。

圖 2.PXIe-7903 硬體架構與重要介面和資料速率。

| 規格 | FPGA | 查找表 (LUT) | DSP 分割 | 嵌入式區塊 RAM |

| PXIe-6591 | Kintex-7 K410T | 254200 | 1540 | 28 Mb |

| PXIe-6592 | Kintex-7 K410T | 254200 | 1540 | 28 Mb |

| PXIe-6593 | Kintex UltraScale KU040 | 242400 | 1920 | 21.1 Mb |

| Kintex UltraScale KU060 | 331680 | 2760 | 38 Mb | |

| PXIe-6594 | Kintex UltraScale+ KU15P | 523000 | 1968 | 34.6 Mb |

| PXIe-7902 | Virtex-7 485T | 303600 | 2800 | 37 Mb |

| PXIe-7903 | Virtex UltraScale+ XCVU11P | 2835000 | 9216 | 341 Mb |

表 2.PXI 高速序列儀器與其各自的 FPGA 規格。

直接連接至 FPGA,最高內建 20 GB 的 DDR3 DRAM,能按照使用者定義的存取碼型,以最高 25 GB/s (理論最大值) 的速率讀取或寫入。FPGA 另有一個 PCI Express x8 Gen 3 介面,能與 PXI Express 背板介接,除了能用於來回串流主機和磁碟的資料,也能將資料 P2P 串流至系統中其他支援 FPGA 的裝置,單向速率最高 7 GB/s,若是雙向速率,每個方向的最高速率則可達到 2.4 GB/s (彙總速率 4.8 GB/s)。

低抖動、高準確度的參考時脈是任何高速序列通訊系統的重要元件。所有模組均內建一個任意速率合成器,能在全系列 Xilinx GTX 收發儀進行 MGT 操作,其中 PXIe-6591、PXIe-6592 和 PXIe-7902 運作速率可達 500 Mbps 到 8 Gbps,裝置速率最高可達 9.8 Gbps,而 PXIe-6593、PXIe-6594 和 PXIe-7903 運作時的最小及最大線路速率則不會出現如此落差。PXIe-6591、PXIe-6592、PXIe-6593 與 PXIe-6594 均提供人機介面同軸連接功能,能匯出內建參考時脈,且四個模組均可連線匯入外部參考時脈。最後,這些裝置可以按既定路線發送 PXI Express 100 MHz 或 DStarA 背板時脈,做為 MGT 的參考時脈。

軟體

軟體設計儀器的功能就和固定功能儀器一樣,不過,使用者可以透過開放式的使用者可程式化 FPGA 自訂儀器硬體。PXI 高速序列儀器必須能達到這樣的客製化程度,才能支援多種協定與用途。因此,沒有任何高階 API 能用於設定這些裝置。必須直接在 LabVIEW 軟體中設定這些裝置的主機 (CPU) 和 FPGA 程式碼,並以初階 NI-RIO API 在兩者之間進行介接。為協助使用者迅速上手執行,我們提供相當豐富的範例,除了示範不同協定的用途之外,也示範這類儀器的不同使用模式。

開放式 FPGA 提供一定程度的客製化功能,這是其他儀器沒有的功能。首先,開放式 FPGA 會執行設定儀器時所針對的序列協定。光是這項功能,就足以讓 PXIe-7903、PXIe-7902、PXIe-6594、PXIe-6593、PXIe-6592 和 PXIe-6591 支援多種標準甚至客製化的序列協定。除了使用協定之外,使用者定義的硬體功能也支援過去無法達成的測試類型。舉例來說,在 FPGA 產生演算法資料能夠減少儲存波形所必需的記憶體空間,以及下載這些波形必須用到的系統頻寬,自然能夠加快測試輸出產能。響應比較、智慧型觸發、資料縮減與壓縮等運算式資料分析,能大幅減少主機 CPU 必須處理的資料量,進而縮短測試時間。

使用者定義的 DRAM 存取權限支援將 DRAM 彈性劃分為激發區與響應區。此外也支援自訂壓縮與解壓縮演算法,以利充分運用 DRAM 大小和頻寬。要擷取和播放標準波形當然也不成問題,但 I/O 頻寬有可能會超出 DRAM 頻寬,這一點需取決於協定、線路速率以及通道數。最後,使用者可以定義往返於高速序列儀器和主機或其他儀器之間的資料移動,系統層級的整合就能發揮相當大的彈性。舉例來說,可以使用高速示波器將類比資料轉換成數位樣本,使用 NI P2P 串流以最高 7 GB/s 的速率將資料傳輸到高速序列儀器,接著再透過序列協定將這些數位樣本傳輸至外接裝置。或者,也可以透過高速序列儀器擷取序列資料串流,依序傳輸至主機 CPU 和高速頻寬 RAID 陣列,進行數小時甚至數天的連續儲存,最高速率一樣可以達到 7 GB/s。

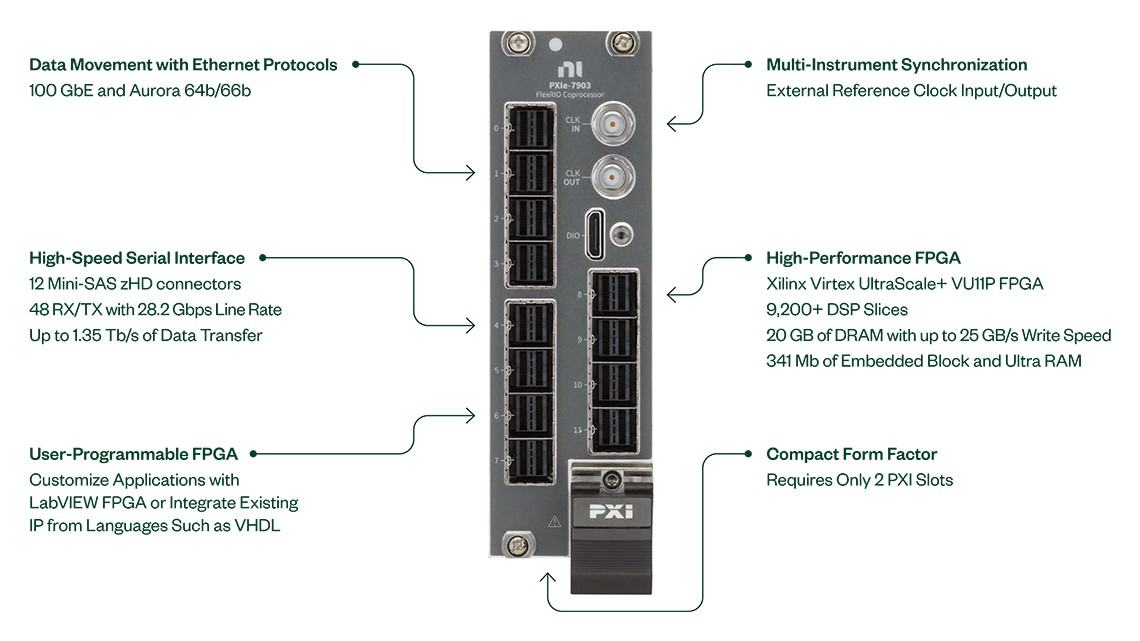

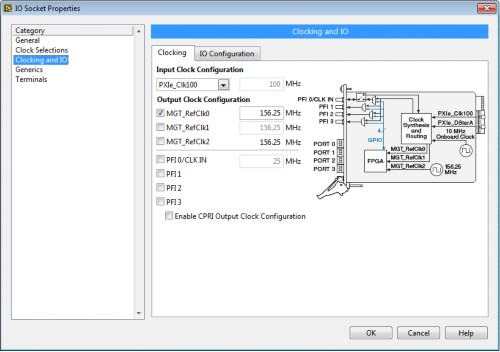

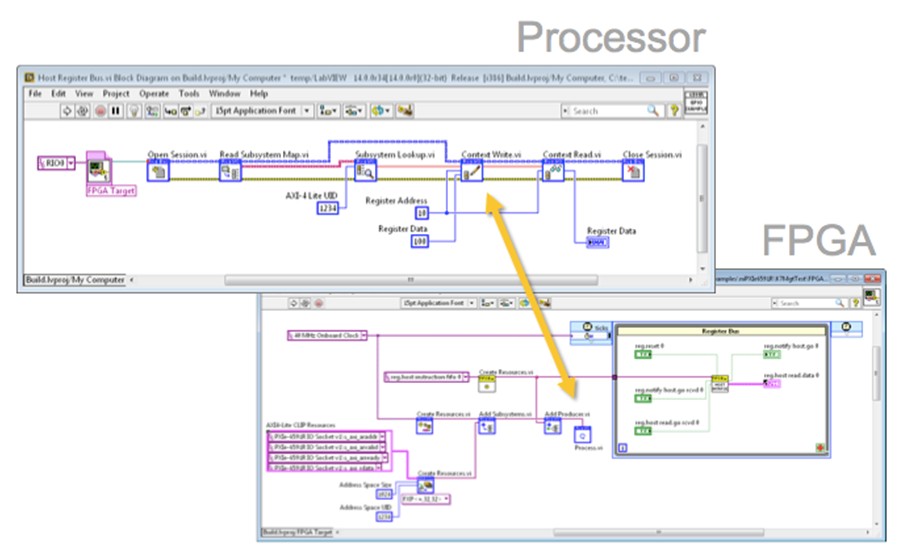

LabVIEW FPGA 有助於簡化這類高速序列儀器的設定與程式設計流程。圖 3 強調能透過 LabVIEW 存取的重要介面,以及代表程式碼。LabVIEW FPGA 和 NI-RIO API 提供有效率的 PCI Express 資料傳輸機制,能在主機 CPU 和 FPGA 之間進行資料傳輸,包括可以進行暫存器讀寫和雙向 DMA 傳輸。DRAM 存取通常是很難以初階硬體描述語言 (HDL) 管理的介面,但只要改用抽象要求讀取及寫入介面,就能簡化管理作業,同時保持高產能並提供基本的讀取/寫入仲裁。GTX 接收儀設定通常因協定而異的,也已經有適用於許多高速序列介面 (HDL 或網路連線表) 且有內建收發儀設定的 IP。這種序列協定介面通常會透過插在插槽中的 Component-Level IP (CLIP) 介面直接顯示在 LabVIEW FPGA。CLIP Node 節點支援非同步操作未在 LabVIEW 中執行的程式碼,但必須要有定義明確的 LabVIEW FPGA 圖介面。常見的情況是使用 Xilinx Vivado IP Catalog 的 Xilinx 特定協定專用 IP (包含收發儀設定) 和 VHDL 薄層定義 LabVIEW FPGA 的介面。執行協定之後,LabVIEW FPGA 就會提供豐富的語言,用於執行任意使用者邏輯,例如決策、狀態機器執行、DUT 控制、訊號處理和資料移動。

圖 3. LabVIEW FPGA 支援使用者透過圖形介面,在 PXI 高速序列儀器上存取使用者可程式化 FPGA 的重要層面。

LabVIEW 不僅能定義在使用者可程式化 FPGA 上執行的邏輯,也能透過其專案階層和相關的設定頁面進一步簡化硬體設定。舉例來說,除了在 FPGA 啟動時必須套用至暫存器的邏輯之外,這些高速序列儀器的參考時脈設定需要複雜的演算法,才能夠判斷數百個、要套用至最多 4 個不同積體電路的暫存器設定。LabVIEW FPGA 會顯示一個對話框,以圖形呈現這些選項,並透過設計規則和指引強制執行有效設定。這種方法將不限速率時脈合成器的設定化繁為簡,並且能將路由電路簡化成一項僅需要幾分鐘就能完成的作業,不需要耗上數小時甚至數天的時間。

圖 4. LabVIEW FPGA 提供簡單好操作的圖形化時脈設定介面,能簡化複雜的流程。

為了重複使用程式碼並簡化一般作業,PXI 高速序列儀器支援特定的儀器設計庫,也就是使用 LabVIEW 介面的主機和 FPGA 程式碼庫,其設計旨在相互搭配運用並發揮通用功能。Instruction Framework 是一種儀器設計庫,適用於在執行階段進行動態硬體設定。這些序列儀器的硬體功能 (例如時脈設定) 大多可透過 LabVIEW 專案完成靜態設定,不過,使用者可以運用 Instruction Framework 控制特定用途的韌體參數。舉例來說,Instruction Framework 能簡化透過 FPGA AXI-4 Lite 介面所顯示的暫存器在主機端的設定作業,通常會出現在 Xilinx 的序列協定 IP 中。

圖 5.處理器和透過 AXI-4 Lite 介面寫入和讀取暫存器的 FPGA 程式碼。

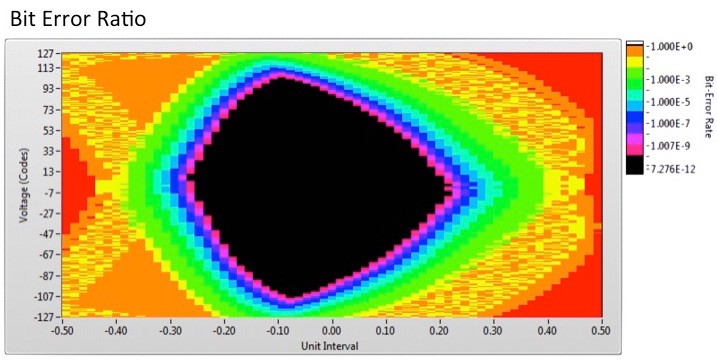

Eye Scan 儀器設計庫以 Instruction Framework 為基礎,能針對高速序列接收通道提供除錯功能。Xilinx GTX 收發儀的每個通道各有兩個接收儀比較器。其中一個比較器會根據已經回復的時脈頻率和相位,自動追蹤序列眼圖中心,而另一個比較器則能夠獨立切換追蹤振幅和相位。只要改變後者的參數並與前者的結果比較,Eye Scan 儀器設計庫即可製作出一個統計眼圖,有助於判斷介面的連結邊緣,準確度可達 Xilinx GTX 收發儀的位元錯誤率下限。此外,因為 Eye Scan 儀器設計庫採用獨立的硬體資源,所以能夠和其他協定 IP 共存,並且和其他應用專屬的功能同步運作。

圖 6. LabVIEW Instrument Design Libraries for PXI High-Speed Serial Instruments 含參考設計,能用於參考如何使用回送設定執行統計 Eye Scan。

除了這些儀器設計庫之外,其他 NI 軟體設計儀器的資料庫也提供豐富的實用功能,例如多重記錄、DRAM 架構的擷取與產生功能。雖然 PXIe-7903、PXIe-7902、PXIe-6594、PXIe-6593、PXIe-6592 及 PXIe-6591 不正式支援也未測試過這些設計庫,但這些設計庫或許也能適用於 PXI 高速序列儀器 (端視這些儀器設計庫是否挑硬體)。

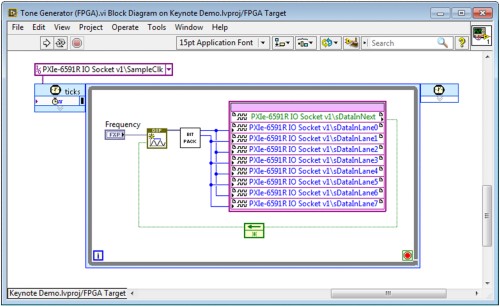

圖 7.工程師可以使用 DSP 儀器設計庫合成正弦波,透過序列 JESD204B 協定傳輸至數位轉類比轉換器。

協定

PXI 高速序列儀器上的 Xilinx GTX 收發儀支援相當多種不同的協定。NI 提供許多軟體範例,用於示範如何整合常用協定,以及適用於數種應用模式的 LabVIEW 架構。每個範例均附預先編譯好的 FPGA 位元檔案,適用於可支援的儀器,同時也附上相關原始碼和協定 IP。如果必須因應最終用途修改程式碼,某些協定還要求必須取得 Xilinx 的 IP 授權才能重新編譯 FPGA。如有需要,可以向 Xilinx 購買這項協定 IP,也可以透過 Avnet 或 DigiKey 等經銷商購買。

Xilinx Aurora

Xilinx Aurora 提供低潛時的小型協定,這是專門為了序列點對點介面所設計的協定。它支援 Xilinx GTX 序列收發儀全速運作,也支援透過通道彙整 (Lane Bonding) 進一步提高的頻寬。Aurora 主要是為了高頻寬資料遷移而設計的,可針對單一或全雙工通道提供流量控制、靈活定框和豐富選項。如需深入了解 Xilinx Aurora,請參考下列連結:

http://www.xilinx.com/products/design_resources/conn_central/grouping/aurora.htm

Instrument Design Libraries for High Speed Serial Instruments 驅動程式會安裝 Aurora 64b66b 專案參考設計範例,NI 也提供 Aurora 8b10b 網頁版範例。

JESD204B 與 JESD204C

類比轉數位轉換器 (ADC) 和數位轉類比轉換器 (DAC) 的取樣率和解析度隨著無線寬頻調變數位傳輸的需求而進步,轉換器之間的資料速率也提高了。如果是傳統的平行時脈和資料介面,就必須用到整合度更高的電路針腳和更嚴格的誤差標準。JESD204B 和 JESD204C 能將這些介面轉換成高速序列,發揮低潛時特性提供高資料頻寬,並且輔助多個轉換器進行同步作業,因此能夠克服這方面的挑戰。JESD204B 最高支援 12.5 Gbps 和 32 個通道,適用於高頻寬、高速的高通道數 ADC 和 DAC。JESD204C 支援最高 32 Gbps 的速率。JESD204B 使用 8B/10B 編碼,而 JESD204C 則支援 8B/10B、64B/66B 與 64B/80B。

10 Gigabit 乙太網路

10 Gigabit 乙太網路 (10 GbE) 的線路速率是 10.3125 Gbps,能提供約 1 GB/s 的實用頻寬。大部分的 10 Gigabit 乙太網路介面均為光學或 SFP+ 直接連接 (銅線),並且採用 8P8C/RJ45 介面。PXIe-6592 適用的 10 Gigabit 乙太網路範例使用 Xilinx 10 Gigabit 乙太網路 PCS/PMA IP 核心與 OpenCores.org 10 Gigabit 乙太網路媒體存取控制器,能支援 10GBASE-SR、-LR 和 -ER 光學介面與 SFP+ 直接連接。除了這個 MAC/PHY 解決方案之外,還有在 LabVIEW FPGA 中執行的 UDP 堆疊。如需深入了解 10 Gigabit 乙太網路 IP 核心,請瀏覽下列連結:

https://www.xilinx.com/products/intellectual-property/10gbase-r.html

Instrument Design Libraries for PXI High-Speed Serial Instruments 驅動程式會安裝 1 GbE 和 10 GbE 的專案參考設計範例。

100 Gigabit 乙太網路

100 Gigabit 乙太網路 (100GbE) 的乙太網路訊框傳輸率可達每秒 100 Gigabit (Gbit/s),速度遠高於 10 Gigabit 乙太網路。100 GbE 提供不同的光學與電氣介面,以及不同數量的光纖束。其中幾個重要介面包括 100GBASE-KR2、100GBASE-CR2 與 QSFP28。

LabVIEW FPGA 隨附一個適用於 100 GbE 的範例。

CPRI

CPRI 定義無線設備控制 (REC) 和無線設備 (RE) 之間的光學介面,通常稱為遠端無線電站 (RRH)。CPRI 能輔助進行無線電站的設定與同步化作業,也有助於串流數位 I/Q (基頻) 資料。如需深入了解 Xilinx CPRI IP 核心,請瀏覽下列連結:

https://www.xilinx.com/products/intellectual-property/do-di-cpri.html

Serial RapidIO

Serial RapidIO 是一種高效能的序列互連協定,針對電信基礎設施、軍事和航太嵌入式運算、高頻寬生命科學裝置和工業控制等具能源效率的嵌入式系統進行過最佳化處理。其速度最高可達 6.25 Gbps,並能發揮四通道彙整、低潛時、流量控制、依序傳遞封包等功能,而且體積相對較小。如需深入了解 Xilinx Serial RapidIO IP 核心,請瀏覽下列連結:

http://www.xilinx.com/products/intellectual-property/ef-di-srio.html

NI 社群提供 PXIe-6592 版 Serial RapidIO 的參考設計。針對 x2 以上的 SRIO 介面,NI 推薦使用 PXIe-6591。

其他協定

上述範例並未完整列出所有相容於 PXI 高速序列儀器的協定。如需深入了解特定協定、上述範例的自訂方式,或者是客製化/專利協定整合,歡迎向當地 NI 業務工程師洽詢。

應用範例

PXI 高速序列儀器的架構十分靈活,能支援多種使用案例,因應不同的資料移動形式、序列協定和軟體功能。

協定功能測試

常見的 PXI 高速序列儀器使用案例,是針對特定的 DUT 執行特定協定專用的功能測試。這些測試是為了確認 DUT 可以透過某個序列協定和「外界」保持穩定通訊,這類測試可能要讀寫 DUT 上的暫存器、執行資料產能和潛時基準測量,或是使用其他的特定協定專用屬性或內建測試模式。此外可能也要測試 DUT 對故障問題的反應,例如回應逾時、輸入錯誤、忽略了流量控制指令等等。相關作業包括連結位元錯誤率量測、實體層壓力測試 (最大和最小線路速率)、預燒測試,甚至是儀器必須在 FPGA 上執行分析、自訂觸發以及資料擷取的匯流排偵伺 (bus snooping)。

DUT 控制、激發和響應

PXI 高速序列儀器的另一個常見使用案例就是 DUT 控制、激發及響應擷取。在此情況下,儀器未必會直接測試高速序列協定,而是會使用高速序列協定收發 DUT 的資料,以利測試該裝置的其他層面。再者,也可以使用輔助數位 I/O 控制 DUT,這個時候就會使用平行或低速序列協定,例如 SPI。

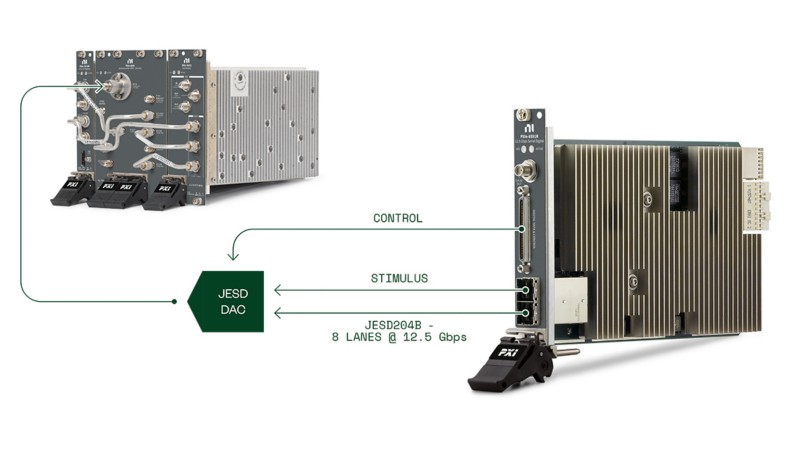

在下列範例中,PXIe-6591 使用 JESD204B 協定模擬 DAC,用於測試 DAC 的類比輸出特性。

圖 8. 許多現代高效能 DAC 和 ADC 都包含使用 JESD204B 高速序列協定進行的通訊功能。

高頻寬資料移動

許多高效能嵌入式用途都能運用 PXI 平台的優勢,不過必須與第三方硬體裝置和 NI PXI 裝置進行高頻寬、低潛時的來回資料移動。就這些用途而言,PXI 高速序列儀器能發揮許多優勢,例如 LabVIEW FPGA 硬體處理、點對點資料串流至 PXI Express 儀器,以及高頻寬的磁碟來回串流,而且還能透過標準的高速序列協定與外接裝置進行高頻寬連線。

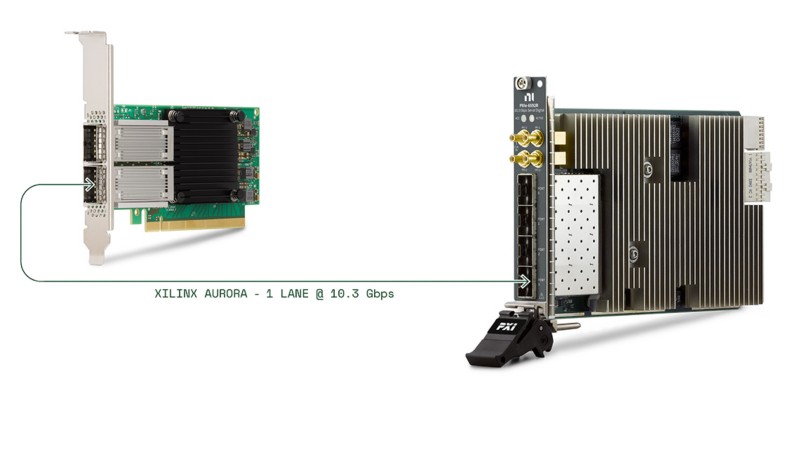

在下列範例中,NI 示波器會擷取一個類比訊號樣本,再使用點對點資料串流將原始的數位化資料傳送至 PXIe-6592 高速序列儀器。接著,儀器就能使用在 LabVIEW FPGA 中執行的演算法即時處理資料。最後,儀器會使用輕量級 Xilinx Aurora 協定將處理過的資料傳送至第三方裝置,這種協定是專為 FPGA 對 FPGA 序列通訊而設計的。

圖 9. PXI 高速序列儀器是與第三方裝置進行高頻寬、低潛時資料移動的一流解決方案。

連結除錯與參數測試

由於高速序列介面採用頻率非常高的訊號,所以不完整的訊號可能會干擾通訊。一旦發生這類問題,就能利用除錯工具清楚掌握連結狀態相關資訊。前述 Eye Scan 儀器設計庫能協助設計人員決定已接收訊號的連結邊緣,並且判斷引發通訊問題的原因是不是訊號完整度不足。這項功能主要是為了在應用程式開發階段進行除錯而設計的,但也能運用於裝置檢驗或製造測試,有助於深入了解特定裝置的效能參數。不過,PXI 高速序列儀器的振幅和時序準確度都有額定值,NI 也不保證使用這些參數能發揮特定效能,或能追溯其使用情形。原位校準或調整可能會是更適合特定用途的選擇。

其他參數測試包括已知偽隨機位元序列 (PRBS) 的位元錯誤率,這個序列以工業級標準碼型 (PRBS-7、PRBS-15、PRBS-23 和 PRBS-31) 取代特定協定。只要更改傳輸器和接收儀的線路速率,即可判斷特定 DUT 可支援的位元速率範圍。最後,要測試收發儀的靈敏度,可以改變傳輸器振福和預/後加強設定,包括自動增益控制和動態等化。

關於 PXIe-6591 和 PXIe-6592 的其他資源,您可以瀏覽下列 NI 社群連結:NI 社群中的 NI MGT 除錯工具,尋找更多能搭配 PXI 高速序列儀器的一起運用的實體層分析工具。針對 PXIe-6593 與 PXIe-6594,請參閱在 PXIe-6593 和 PXIe-6594 高速序列裝置上使用 Eye Scan。

必備技能

雖然 LabVIEW 和 LabVIEW FPGA 能大幅簡化高速序列技術執行方式,但仍必須具備一定程度的專業知識,才能成功設計出 PXI 高速序列儀器的程式。這類儀器都是使用 LabVIEW 設計的,因此必須非常熟悉 LabVIEW 圖形化程式設計概念。ni.com 的 NI LabVIEW 應用程式開發教育訓練課程可以提供相關協助。此外,若要在 LabVIEW FPGA 中自訂非協定 FPGA 邏輯,必須深入了解高產能 LabVIEW FPGA 程式設計。NI LabVIEW 高效能 FPGA 開發指南為您提供豐富的學習資源。 針對已有 IP 或範例的協定,必須具備 VHDL 知識和經驗才能定義協定 IP 和 LabVIEW FPGA 圖之間的介面。最後,要執行全新協定或客製化協定,最好要具備高等的數位設計專業能力。如果組織內部沒有相關專業人才,也有一些 NI 合作夥伴能提供相關服務。當地的 NI 業務代表可以協助您找到適當的合作夥伴。

| 使用模式 | LabVIEW | 高傳輸 LabVIEW FPGA | VHDL | 豐富的數位設計專業知識 |

| 使用現有的特性 | — | — | — | |

| 客製化 FPGA 程式碼而非協定 | — | — | ||

| 整合現有協定 | — | |||

| 執行新的協定或客製化協定 |

表 4. 要設計高速序列儀器的程式,必須具備不同程度的技能和工具,這取決於介面的變化程度。

後續步驟

- 了解如何運用 NI PXI 高速序列儀器模組充分發揮資料移動與訊號處理的效能。

- 深入了解高速序列通訊連結的基本概念。

- 觀看在無線電收發儀功能測試系統中執行高速序列協定的參考設計範例。

- 如需了解硬體驅動程式未附的其他協定參考設計,請至 Examples and IP for Software-Designed Instruments 與 NI FlexRIO 社群。

- 購買 PXI 高速序列儀器。

- 建構自己的 PXI 系統。