每次测量均始于触发

概览

内容

对于像示波器这样的仪器,一项重要要求是能够快速、可靠地检测和触发已知信号流中的感兴趣事件。对特定事件的检测越迅速,就会越及时地纠正电子设计过程中产生的问题,从而节省开发和生产测试时间。

示波器供应商并未忽视这一要点。许多供应商提供了多达100种预定义的触发方法,帮助用户快速将较为常见和不常见的信号条件区分开来。这样可以提高灵活性,但选择正确的触发方法本身要比实际捕获信号更加困难,因为触发的类型多种多样,速度、带宽、延时和使用的软件等各不相同,每种触发都需要在灵活性与时滞之间进行权衡。了解不同类型的触发以及相应的权衡有助于找到理想的触发方法来提高成功触发事件的几率。

示波器的触发性能由两方面决定:

- 触发灵活性描述了定义触发阈值或条件来适应各种待测信号条件以提高效率的简单程度。大多数示波器提供了供应商定义的各种触发功能,其中设定了参数的最低值,比如电平或宽度等,但是没有提供这些参数的自定义方法。

- 触发时滞是指示波器在两次采集之间无法检测到触发的时长。这意味着如果感兴趣事件发生在时滞内,那么将错过触发条件。触发时滞是所有触发架构的固有特性,但是可以采用一些方法和技术来尽可能地缩短时滞。许多示波器供应商提供了基于软件的触发来增强灵活性,但是由于需要进行后处理,这类触发需要较长的时滞,因此不适合检测小概率和低频率事件。

传统触发

边沿触发(信号从低电平变成高电平或从高电平变成低电平时开始采集)是目前最常见的示波器触发模式。大部分简单的调试和测试功能都通过边沿触发进行处理,但有时需要借助更为复杂的触发方法来隔离特定的信号形状或多个连续的形状。示波器也包含了一些更高级的触发选项,能够更灵活地捕获I2C或SPI等串行协议以及高级事件和信号特性,比如毛刺、矮电平、宽度、边沿斜率和超时等。

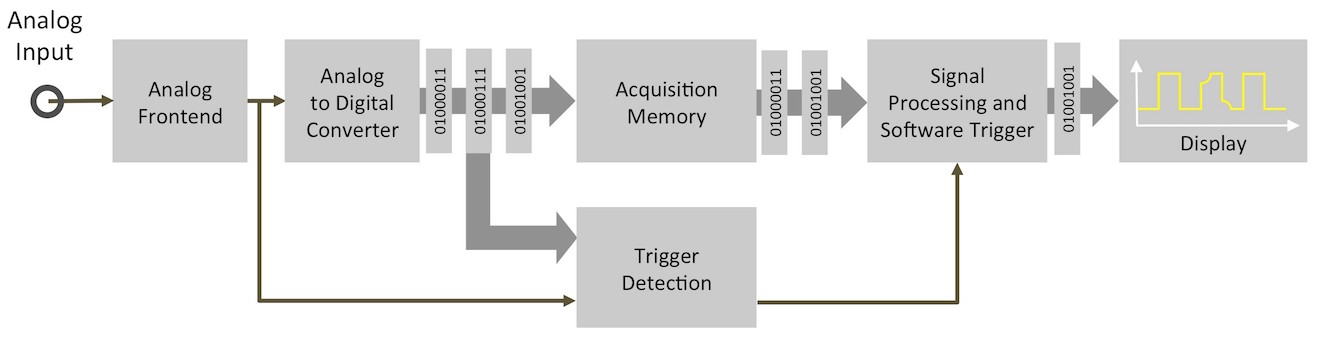

图1.这是一个基于数字信号处理的示波器程序框图。采集存储器和信号处理单元决定了示波器的采集更新速率和时滞。

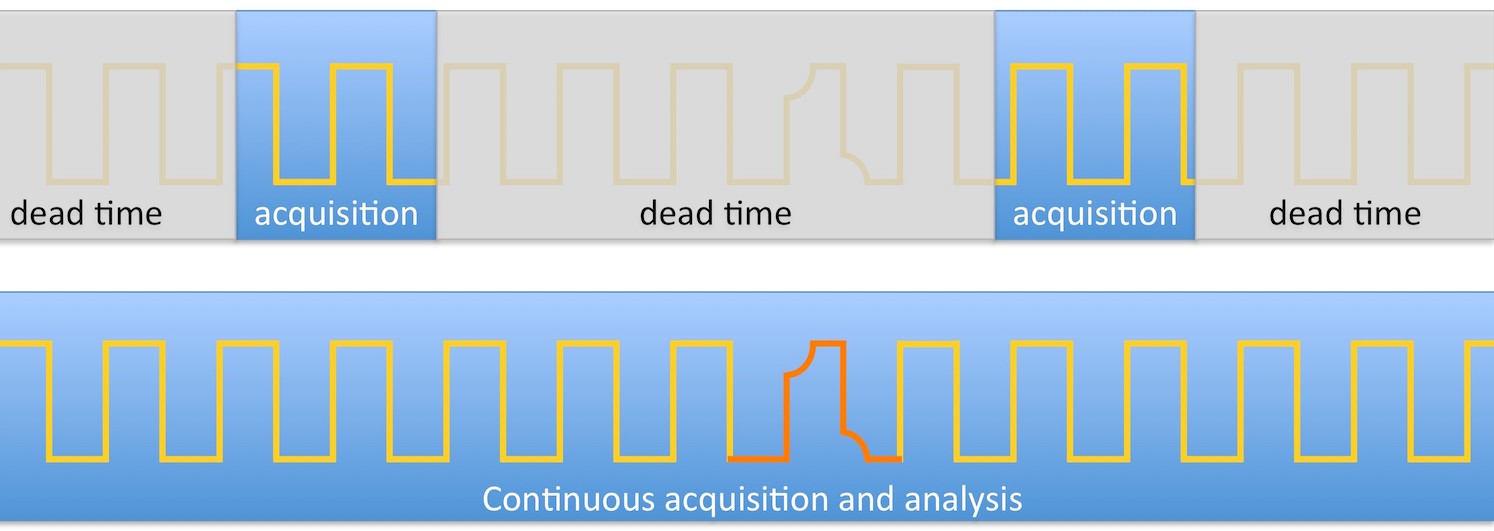

许多触发条件在硬件中实现,但较为复杂的触发选项和信号确认通常在软件中执行,如图1所示。软件触发提供了最大的灵活性,但增加了必要的数据传输和处理时间,而在此期间示波器无法检测到新的触发,如图2所示。触发系统“失明”的这段时间称为时滞,通常比实际采集的数据记录长一个数量级。换句话说,示波器触发系统在95%的时间里可能处于“失明”状态。这使得检测小概率或低频率事件变得更为困难,而且导致测试时间更长。更糟糕的是,用户可能错误地假设预期事件没有发生,因为预期事件发生的概率太低,以致在测量过程中没有检测到。

图2.该图显示了传统示波器的波形采集和分析过程,其中波形快照(上)和连续处理(下)之间存在时滞。

如果示波器的可用触发或信号分析功能无法满足任务的需求,那么用户仅有的选择就是采集较长的波形片段,并将获取的原始数据下载到PC上,用于进行后处理以找到特定事件。但是这增加了整个系统的设计复杂度,同时由于数据传输延时和必要的处理时间,使得测试时间变长。

创建触发,无需权衡

虽然大部分基于软件的或智能的触发选项可以满足电子电路的设计和测试需求,但是如果不能迅速隔离或纠正小概率事件,这些事件往往会大幅减缓产品开发过程。由于大部分示波器触发功能存在局限性,用户只能使用供应商所提供的功能。

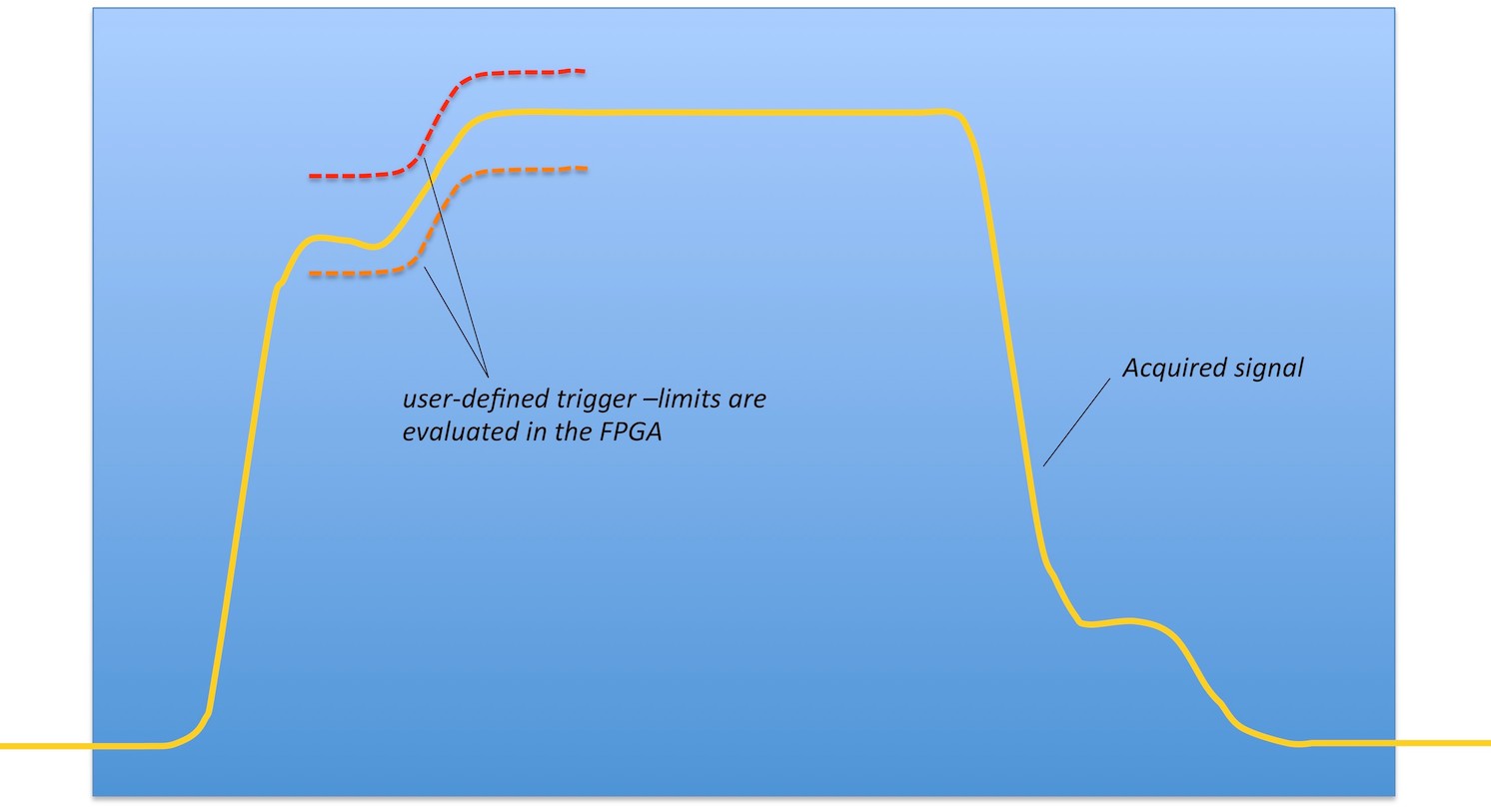

如果用户可以在示波器内部署自行开发的算法,那么就可以针对特定任务自定义仪器的功能,而不会受限于仪器供应商提供的功能。比如,用户可以针对特定应用自行定义触发条件来专门捕获某个信号条件,这样就无需在PC上进行后处理,从而大大减少了测试时间,如图3所示。

既能实现示波器在线数据处理,又能灵活地重新编程算法的关键使能技术是FPGA,FPGA从本质上来说是可编程芯片,它可以通过真正的并行机制以高吞吐率执行自定义信号处理和控制算法。得益于FPGA的灵活性,可以修改或增加用户特定的触发算法,同时高吞吐量的数据处理可在采集过程中实时分析数据样本,而不是在后处理中进行。这样可避免时滞、防止错过触发并有助于更快地检测小概率事件。

一个用户定义的触发范例是检测不符合标准触发定义的信号形状或转换,如图3的信号所示。该数字信号具有非单调边沿,这可能是由信号反射或被测电路的电源故障引起的。标准边沿或宽度触发无法检测这种干扰信号,而且基本不可能使用常规手段进行检测。我们需要研究一种新的触发方法来精确、连续地捕获这个事件。为了解决这一问题,需要开发软件触发。然而这种方法存在较长的触发时滞,无法快速检测小概率事件。或者,我们可以采用用户可编程的FPGA来提供多个窗口触发,当所有窗口触发同时检测到有效触发条件时,就会将采集的样本点与掩模进行对比,从而产生一个组合触发并采集信号。

由于FPGA可连续、实时地评估信号,因此示波器既可以捕获单个事件,也可以捕获连续事件,而且在两次采集之间不会存在时滞。

图3.使用用户定义的触发捕获特定信号转换;该功能在可重配置示波器的FPGA内实现。

可重配置示波器

多年来,测试工程师一直使用LabVIEW等软件,而不是传统台式仪器内的固定软件,实现了测试系统自动化、分析和显示测量结果并节省了测试成本。这种方法具有一定灵活性且利用了全新的PC和CPU技术。然而,用户的需求往往不限于此,他们通常需要更改仪器的测量方式来更好地满足应用需求。

传统的现成即用仪器由供应商定义并仅提供固定的功能;而NI率先采用FPGA技术来提供更加开放、灵活的仪器。因此,现成即用的硬件具备多方面优势:功能固定的高质量测量技术、全新的数字总线集成和用户可自定义的逻辑。用户可自定义的逻辑具有高度并行性,延迟较低,并直接与I/O连接,可实现在线处理。

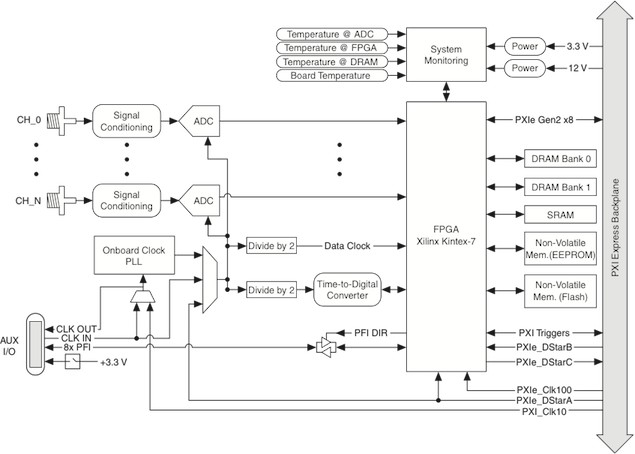

图4.可重配置示波器NI PXIe-5171R的程序框图。

过去,只有精通使用Verilog或VHDL等工具进行数字硬件设计的工程师才能使用FPGA技术。各种高级系统设计工具(如LabVIEW)的出现改变了FPGA编程的规则,将图形化程序框图转换为数字硬件电路的新技术应运而生。所有NI FPGA硬件产品(包括NI PXIe-5171R)均基于LabVIEW可重配置I/O (RIO)架构构建,该架构具有强劲的浮点处理器、可重配置FPGA和模块化I/O。对于设计高级控制、监测和测试应用,使用LabVIEW RIO架构将有助于简化开发并缩短产品上市时间。借助LabVIEW,用户可以扩展仪器的功能,实现自定义触发、额外定时或信号控制等。用户也可以在软件设计仪器的FPGA中部署自行开发的算法,重新定义硬件的用途来执行完全不同的任务。比如,示波器可以变成实时频谱分析仪、瞬态记录仪、协议分析仪和RF接收器等。

由于只需要购买和维护更少的仪器,因此有助于节约设备成本,而这是测试系统的一项主要成本。如果需要长期(超过10年)提供测试和仪器功能,这点尤其实用,比如军用或航空航天测试系统。此类应用常常需要再现已淘汰(生命周期终止)的旧仪器行为。

可重配置仪器非常适用于这一应用,因为它们可以通过重新编程来模拟旧仪器的行为。这有助于节省成本,因为测试系统软件只需较少的返工和重新认证即可与新仪器配合工作。

NI PXIe-5171R可重配置示波器便属于此类仪器,它通过Xilinx Kintex-7 FPGA来实时处理来自8个输入的采样。图4展示了用户可编程的FPGA如何集成到数据路径中,并提供对仪器控制和定时信号的访问。

结语

由于示波器的传统触发方法缺乏灵活性和实时分析能力,因此无法捕获小概率和复杂事件。全新的方法可利用FPGA技术来定义自定义触发功能,从而满足较为复杂的触发条件以及实时进行信号处理和分析。