PXI高速串行仪器简介

概览

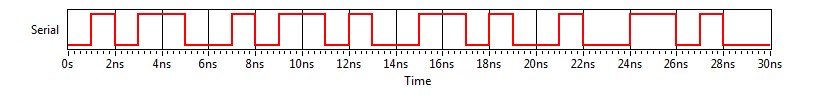

PXI高速串行仪器可帮助工程师验证、连接和测试高速串行协议。一些高速串行设备(如PXIe-7903和PXIe-7902)专为需要高性能FPGA协同处理能力的工程师而设计,以实现大容量数据移动和在线实时信号处理。该硬件配有Xilinx Kintex™ UltraScale+™或7系列FPGA,可使用LabVIEW FPGA模块进行编程,以最大程度实现应用专用的自定义和复用。这些仪器利用了FPGA多千兆位收发仪(Multigigabit Transceiver, MGT),可支持高达28.2 Gbps的线速率和多达48个TX和RX通道。作为PXI平台的一部分,它们同样受益于PXI时钟、触发、高速数据移动功能,包括高达7 GB/s的数据流盘和点对点(P2P)数据流。

内容

高速串行接口崭露头角

对于更高数据带宽的需求日益增加,有线接口的时钟速率和并行度也在随之增长。然而,对于传统并行数据总线,时钟线和数据线之间极小的偏斜都会对接口的误码率造成不利影响。串行数据链路则解决了这一问题,通过在给定差分对走线的数据流中嵌入时钟,避免了时钟和数据之间出现偏斜。该功能虽需要在接口接收端使用额外电子设备并额外进行用于时钟恢复的编码;不过,这样可显著提高数据传输速率,从而满足带宽需求。

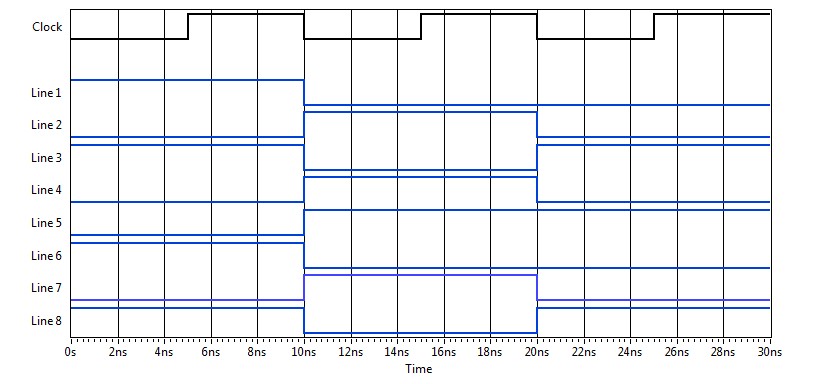

图1.并行时钟(黑色)和数据(蓝色)与数据中的嵌入式时钟(红色)对比,其中数据带宽相同。

现代数据通信协议已从这些并行接口过渡到高速串行接口,例如PCI Express、HDMI与DisplayPort视频标准、IEEE 1394b、USB 3.0等。验证这些接口需要使用新的测试硬件,这为设计和测试工程师带来了新的挑战。传统上,工程师使用昂贵的示波器或误码率测试仪(Bit Error Rate Tester, BERT)对物理接口进行特性分析,并使用协议专用分析仪和发生器验证协议栈是否正确实现以及数据传输和接收是否有效。但在自动化确认与验证以及制造测试中,目前并没有可用于测试这些串行接口的优化硬件。示波器和误码率测试仪通常成本十分昂贵且速度缓慢,无法证明其所提供覆盖范围的合理性,而协议专用硬件通常缺乏灵活性,无法集成至自动化测试系统中。另一方面,协议专用硬件无法重复用于其他测试,也无法重新用于其他被测设备(Devices Under Test, DUT)。

FPGA为这些挑战提供了解决方案。现代高性能FPGA通常包含多个MGT,可与各种高速串行接口配合使用。通过将适合的协议专用IP、LabVIEW FPGA模块的图形化编程功能以及PXI生态系统的优势相结合,一款全新高速串行软件设计仪器应运而生。

高速串行模块

|  |  |  |  |  | |

| 规格 | PXIe-6591 | PXIe-6592 | PXIe-6593 | PXIe-6594 | PXIe-7902 | PXIe-79032 |

| 线速率 | 500 Mbps-12.5 Gbps¹ | 500 Mbps-10.3125 Gbps¹ | 500 Mbps-16.3 Gbps | 500 Mbps-28.2 Gbps | 500 Mbps-12.5 Gbps | 500 Mbps-28.2 Gbps |

| 通道 | 8 TX/RX | 4 TX/RX | 8 TX/RX | 8 TX/RX | 24 TX/RX | 48 TX/RX |

| FPGA | Kintex 7 K410T | Kintex 7 K410T | Kintex UltraScale KU040、KU060 | Kintex UltraScale+ KU15P | Virtex™ 7 485T | Virtex UltraScale+ XCVU11P |

| DRAM | 2 GB | 2 GB | 4 GB | 8 GB | 2 GB | 20 GB |

| 主机数据流带宽 | 3.2 GB/sec | 3.2 GB/sec | 7 GB/sec | 7 GB/sec | 3.2 GB/sec | 7 GB/sec |

| 连接器 | Mini-SAS HD | SFP+ | QSFP28 | QSFP28 | Mini-SAS HD | Mini-SAS HD |

| 布线选项 | 铜缆或光纤 | 铜缆或光纤 | 铜缆或光纤 | 铜缆或光纤 | 铜缆或光纤 | 铜缆或光纤 |

| Aux DIO | 20 SE | 4 SE | 8 GPIO | 8 GPIO | 不适用 | 8 GPIO |

表1.PXI高速串行仪器。

¹线速率在8 Gbps和9.8 Gbps之间并不连续。

²PXIe-7903是双插槽模块。

连接和布线对于具有高数据传输速率和超过20 GHz模拟带宽的应用至关重要。PXIe-7903、PXIe-7902、PXIe-6594、PXIe-6593、PXIe-6592和PXIe-6591均提供了不同选项,用于简化特定用例的连接。所有3个模块均以用户可编程的Xilinx FPGA为核心。

这些仪器的基础关键技术均源自Xilinx 7系列GTX收发仪。它们使用电流型逻辑(Current Mode Logic, CML),这是一种具有800 mVpp小信号摆幅(最大标称值为1,000 mVpp)的差分接口,可降低功耗、辐射以及100 Ω差分阻抗(每个信号端50 Ω),从而在高数据传输速率下最大限度地减少反射和由此产生的信号畸变。此外,为了获得最佳信号保真度,这些收发仪还包括一个可编程发射振幅,用于补偿长电缆以及发射预加重与后加重和自动适应接收器均衡,以应对有限的模拟通道/电缆带宽。

所有高速串行接口都需要一个以线速率整数约数运行的参考时钟。为尽可能实现灵活工作,GTX收发仪包含一个锁相环(Phase-Locked Loop, PLL),可将参考时钟乘以100倍以生成串行数据传输速率。该收发仪还包括比率高达80倍的串行至并行和并行至串行转换器,可在限制FPGA时钟频率的同时实现高串行数据传输速率。此外,收发仪还内置有8b/10b、64b/66b和64b/67b编解码结构,以确保足够数量的信号转换可用于时钟恢复,并可避免占用通用FPGA资源。请参阅Xilinx 7系列FPGA GTX/GTH收发仪用户指南(Xilinx 7 Series FPGAs GTX/GTH Transceivers User Guide),获取更多Xilinx GTX收发仪相关信息。

除了提供高速串行收发仪外,仪器中的Xilinx FPGA还有其他几个重要用途。不仅可以实现在用协议的逻辑,还能实现用于硬件配置以及整个系统的数据生成、接收和移动的所有应用专用用户逻辑。

图2.PXIe-7903硬件架构(包含关键接口和数据传输速率)。

| 规格 | FPGA | LUT | DSP切片 | 嵌入式块RAM |

| PXIe-6591 | Kintex-7 K410T | 254,200 | 1,540 | 28 Mb |

| PXIe-6592 | Kintex-7 K410T | 254,200 | 1,540 | 28 Mb |

| PXIe-6593 | Kintex UltraScale KU040 | 242,400 | 1,920 | 21.1 Mb |

| Kintex UltraScale KU060 | 331,680 | 2,760 | 38 Mb | |

| PXIe-6594 | Kintex UltraScale+ KU15P | 523,000 | 1,968 | 34.6 Mb |

| PXIe-7902 | Virtex-7 485T | 303,600 | 2,800 | 37 Mb |

| PXIe-7903 | Virtex UltraScale+ XCVU11P | 2,835,000 | 9,216 | 341 Mb |

表2.PXI高速串行仪器及相应的FPGA规范。

高达20 GB的板载DDR3 DRAM直接连接至FPGA,其在用户定义访问模式中的读写速度高达25 GB/s(理论最大值)。FPGA还包括一个可连接至PXI Express背板的PCI Express ×8 Gen 3接口,对于数据流主机和数据流盘或P2P至系统中其他启用FPGA的设备,该接口能以高达7 GB/s单向速率或2.4 GB/s的双向速率(总计4.8 GB/s)传输数据。

低抖动、高保真参考时钟是每个高速串行通信系统的关键组件。所有模块都具有板载任意速率合成器,可在Xilinx GTX收发仪的全范围内实现MGT操作,其中,PXIe-6591、PXIe-6592和PXIe-7902的线速率为从500 Mbps至8 Gbps和从9.8 Gbps至最大设备速率,而PXIe-6593、PXIe-6594和PXIe-7903在其最小和最大线速率之间并无这种不连续情况。PXIe-6591、PXIe-6592、PXIe-6593和PXIe-6594具有用于导出内置参考时钟的前面板同轴连接,并且所有4个模块都具有用于导入外部参考时钟的连接。最后,这些设备还可连接PXI Express 100 MHz或DStarA背板时钟,以作为MGT的参考。

软件

软件设计仪器提供与固定功能仪器相同的功能,但用户可通过用户可编程的开放式FPGA对仪器硬件进行自定义。PXI高速串行仪器需要通过这种自定义级别来支持各种协议和应用。因此,并没有用于对这些设备进行编程的单一高级API。而是直接在LabVIEW软件中针对主机(CPU)和FPGA代码进行编程,并通过低层NI-RIO API连接二者。为帮助用户快速入门和运行,我们通过大量范例演示了不同协议的用法,以及这些仪器的不同使用模型。

开放式FPGA提供了其他仪器所不具备的定制化程度。首先,它实现了仪器配置的串行协议。仅此一项就使PXIe-7903、PXIe-7902、PXIe-6594、PXIe-6593、PXIe-6592和PXIe-6591能够支持多种标准甚至自定义串行协议。除协议之外,用户定义的硬件功能还可支持进行以前无法实现的测试。例如,FPGA中的算法数据生成功能可减少下载这些波形所需的波形内存和系统带宽,从而提高测试吞吐量。响应比较、智能触发以及数据缩减和压缩等算法数据分析大大减少了主机CPU需处理的数据量,从而缩短了测试时间。

用户定义的DRAM访问可灵活地将DRAM划分为激励区域和响应区域。还支持自定义压缩和解压缩算法,从而优化DRAM空间和带宽的使用。捕捉和回放标准波形虽然是基础功能,但考虑到协议、线速率和通道数量这3个因素,I/O带宽可能会超过DRAM带宽。最后,高速串行仪器与主机或其他仪器之间的用户定义数据移动使系统级集成更为灵活。例如,可以使用高速数字化仪将模拟数据转换为数字采样、使用NI P2P数据流将该数据以高达7 GB/s的速率传输至高速串行仪器,然后通过串行协议将此数字采样传输至外部设备。或者,高速串行仪器也可以捕获串行数据流,并将其传输至主机CPU,最终传输至高带宽RAID阵列,进行数小时甚至数天的连续存储,传输速率同样高达7 GB/s。

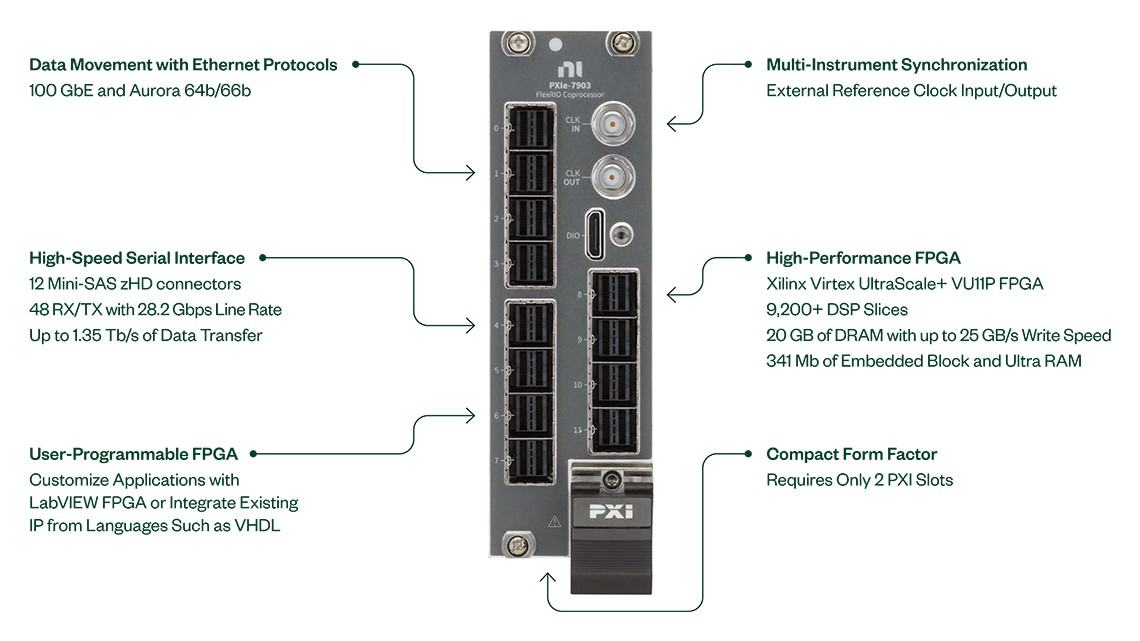

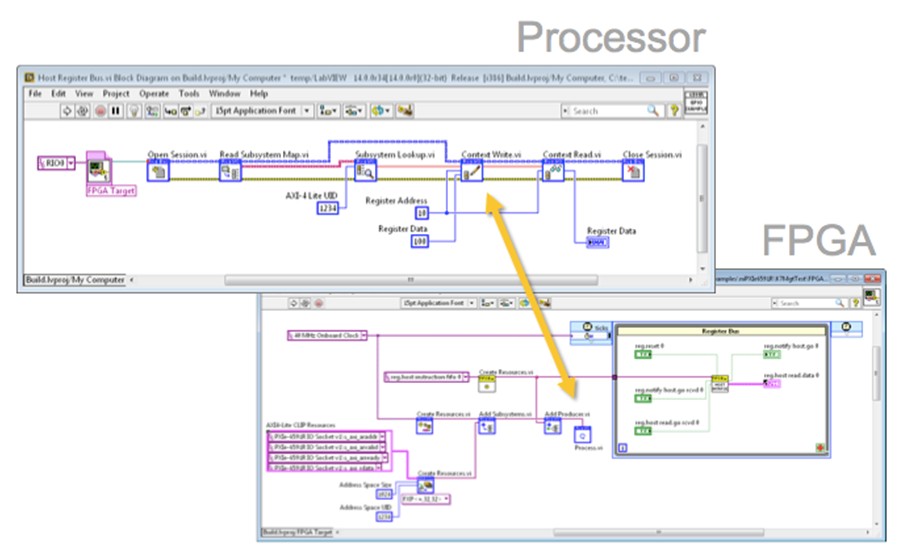

LabVIEW FPGA可简化这些高速串行仪器的配置和编程过程。图3重点介绍了LabVIEW可访问的关键接口以及典型代码。LabVIEW FPGA和NI-RIO API为主机CPU和FPGA之间基于PCI Express的数据传输提供了高效的机制,其中包括了寄存器读写以及双向DMA传输。DRAM访问(由底层硬件描述语言(Hardware Description Language, HDL)管理的接口,此类接口通常难以访问)通过抽象的请求、读取和写入接口得以简化,同时保持高吞吐量并提供基本的读取/写入仲裁。GTX收发仪通常采用协议专用配置,同时IP已经用于内置了收发仪配置的众多高速串行接口(HDL或网表)。该串行协议接口在LabVIEW FPGA中的形式为插槽式组件级IP (Component-Level IP, CLIP)接口。CLIP节点支持对未在LabVIEW中实现的代码进行异步操作,但在与LabVIEW FPGA程序框图之间具有明确定义的接口。常见的例子是使用Xilinx Vivado IP目录中的Xilinx协议专用IP(包括收发仪配置)和VHDL薄层定义LabVIEW FPGA接口。协议实现后,LabVIEW FPGA提供丰富的语言以实现任意用户逻辑,如决策、状态机实现、DUT控制、信号处理和数据移动。

图3. LabVIEW FPGA可对PXI高速串行仪器中的用户可编程FPGA关键部分进行图形化访问。

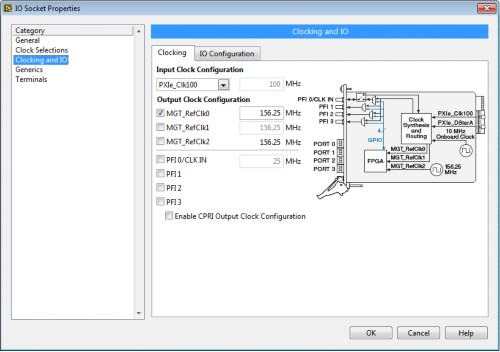

除了定义需在用户可编程FPGA上实现的逻辑外,LabVIEW还通过其项目层次结构和相关的配置页面简化了硬件配置。例如,这些高速串行仪器上的参考时钟配置需要复杂的算法来确定数百个寄存器设置,这些寄存器设置将应用于多达4个独立集成电路中,此外还需要在FPGA上电时应用这些寄存器所需的逻辑。LabVIEW FPGA将其展示为一个对话框,其中包含选项的图形表示,以及实施有效配置的设计规则和指南。该方法简化了任意速率时钟合成器和布线电路的配置,无需花费数小时或数天时间,只需几分钟即可完成任务。

图4. LabVIEW FPGA为时钟配置提供了直观的图形界面,简化了复杂的流程。

为了实现代码复用并简化常见任务,PXI高速串行仪器提供了特定的仪器设计库,这些库是具有LabVIEW接口的主机和FPGA代码库,可相互协作并提供通用功能。指令框架是一个仪器设计库,用于在运行时进行动态硬件配置。虽然这些串行仪器的大部分硬件功能(例如,时钟配置)都可在LabVIEW项目中进行静态配置,但用户也可以利用指令框架来控制应用专用的固件参数。例如,指令框架简化了通过FPGA AXI-4 Lite接口显示的寄存器设置的主机配置,这在Xilinx串行协议IP中很常见。

图5.处理器和FPGA代码,通过AXI-4 Lite接口写入和读取寄存器。

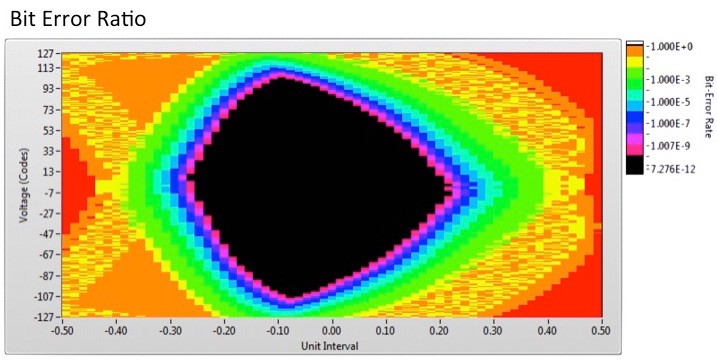

眼图扫描仪器设计库基于指令框架构建,为高速串行接收通道提供调试功能。Xilinx GTX收发仪的每个通道都有2个接收器比较器。一个比较器根据恢复的时钟频率和相位自动跟踪串行眼图的中心,而另一个比较器可独立改变幅值和相位。通过改变后一比较器的参数并将结果与前一比较器进行比较,眼图扫描仪器设计库可创建一个用于确定接口的链路余量的统计眼图,精确到Xilinx GTX收发仪的误码率下限。此外,由于眼图扫描仪器设计库使用一组独立的硬件资源,因此其可与其他协议IP共存,并与其他应用专用功能同时运行。

图6. 用于PXI高速串行仪器的LabVIEW仪器设计库包含一个使用环回配置执行统计眼图扫描的参考设计。

除这些仪器设计库外,其他NI软件设计的仪器提供了多种有用的功能库,例如多记录以及基于DRAM的采集和生成。虽然PXIe-7903、PXIe-7902、PXIe-6594、PXIe-6593、PXIe-6592和PXIe-6591未得到正式支持或测试,但根据仪器设计库的硬件中立性,它们也可与PXI高速串行仪器搭配使用。

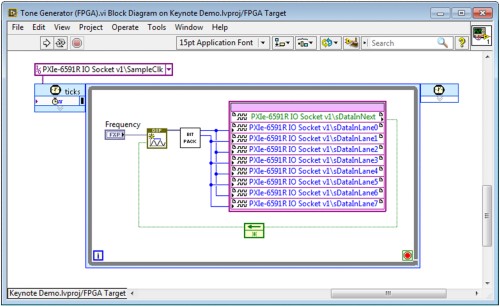

图7.工程师可使用DSP仪器设计库合成正弦信号,以便通过串行JESD204B协议传输至数模转换器。

协议

PXI高速串行仪器中的Xilinx GTX收发仪支持多种协议。NI提供了大量软件范例,演示了如何集成常见协议以及LabVIEW架构以实现多种应用模式。每个范例都附带一个用于受支持仪器的预编译FPGA比特文件,以及相关的源代码和协议IP。如果最终应用需要修改该代码,某些协议需要Xilinx的IP许可证才能重新编译FPGA。该协议IP可通过Xilinx或转售商(如Avnet或DigiKey)购买。

Xilinx Aurora

Xilinx Aurora是专为串行点对点接口设计的一款轻量级、低延迟、小尺寸的协议。它支持全速率Xilinx GTX串行收发仪以及更高带宽的通道绑定。Aurora旨在用于高带宽数据移动,可提供流量控制、灵活成帧以及单工或全双工通道选项。关于Xilinx Aurora的详细信息,请访问以下链接:

http://www.xilinx.com/products/design_resources/conn_central/grouping/aurora.htm

Instrument Design Libraries for High Speed Serial Instruments驱动程序安装了Aurora 64b66b的范例项目参考设计,NI还提供了Aurora 8b10b的Web范例。

JESD204B和JESD204C

模数转换器(Analog-to-Digital Converter, ADC)和数模转换器(Digital-to-Analog Converter, DAC)的采样率和分辨率为满足无线宽带调制数字传输的需求而不断提高,这些转换器之间的数据传输速率也在随之增加。对于传统的并行时钟和数据接口,这需要更多具有更严格公差的集成电路引脚。JESD204B和JESD204C为应对这一挑战,将这些接口转换为高速串行接口,旨在提供高数据带宽和低延迟,并促进多转换器同步。JESD204B支持高达12.5 Gbps的线速率和32个通道,适用于最新的高带宽、高速和高通道数的ADC和DAC。JESD204C支持高达32 Gbps的线速率。JESD204B使用8B/10B编码,JESD204C支持8B/10B、64B/66B和64B/80B编码。

10千兆以太网

10千兆以太网(10 GbE)凭借10.3125 Gbps的线速率,可提供大约1 GB/s的实际带宽。大多数10千兆以太网接口均为光纤或SFP+直连(铜缆),并采用基于8P8C/RJ45的接口。PXIe-6592的10千兆以太网范例支持10GBASE-SR、10GBASE-LR和10GBASE-ER光纤接口以及SFP+直连,并使用Xilinx 10 Gigabit Ethernet PCS/PMA IP核和OpenCores.org 10千兆以太网媒介访问控制器。LabVIEW FPGA中实现的轻量级UDP堆栈就是以MAC/PHY解决方案为基础。有关10千兆以太网IP核的详细信息,请访问以下链接:

https://www.xilinx.com/products/intellectual-property/10gbase-r.html

Instrument Design Libraries for PXI High-Speed Serial Instruments驱动程序安装了1 GbE和10 GbE的范例项目参考设计。

100千兆以太网

100千兆以太网(100 GbE)能以每秒100千兆(Gbit/s)的速率传输以太网帧,速度远高于10千兆以太网。100 GbE提供了不同的光电接口以及不同数量的光纤束。部分关键接口包括100GBASE-KR2、100GBASE-CR2和QSFP28。

LabVIEW FPGA附带一个100 GbE范例。

CPRI

CPRI定义了无线设备控制中心(Radio Equipment Control, REC)和无线设备(Radio Equipment, RE)之间的光纤接口,通常将该接口称为射频拉远头(Remote Radio Head, RRH)。CPRI有助于配置和同步射频头,以及流传输数字I/Q(基带)数据。关于Xilinx CPRI IP核的详细信息,请访问以下链接:

https://www.xilinx.com/products/intellectual-property/do-di-cpri.html

串行RapidIO

串行RapidIO是一种高性能串行互连协议,并针对电信基础设施、军事和航空航天嵌入式计算、高带宽生命科学设备和工业控制等嵌入式系统进行了优化。该协议具有高达6.25 Gbps的线速率、4通道绑定、低延迟、流量控制、有序数据包传输和相对较小的占用空间。关于Xilinx串行RapidIO IP核的详细信息,请访问以下链接:

http://www.xilinx.com/products/intellectual-property/ef-di-srio.html

NI社区提供了用于PXIe-6592的串行RapidIO参考设计。NI推荐高于x2的SRIO接口使用PXIe-6591。

附加协议

上述示例并未完全列出所有与PXI高速串行仪器兼容的协议。NI本地销售工程师可为您解答有关特定协议、自定义上述示例、其他自定义协议或专有协议集成的问题。

应用范例

PXI高速串行仪器的灵活架构使其能够支持各种具有不同的数据移动模式、串行协议和软件功能的用例。

协议功能测试

PXI高速串行仪器的一个常见用例就是对给定的DUT执行协议专用的功能测试。该测试旨在确认DUT可通过串行协议与“外界”进行可靠的通信。此类测试可能会写入和回读DUT中的寄存器、执行数据吞吐量和延迟基准测试,或测试其他协议专用的属性或内置测试模式。还可以用于测试DUT对故障场景的响应方式,例如响应超时、注入错误或忽略流控制命令等。相关任务包括链路误码率测量、最大和最小线速率等物理层应力测试、老化测试甚至总线窥探,其中仪器在FPGA上执行分析、自定义触发和数据采集。

DUT控制、激励和响应

PXI高速串行仪器的另一个常见用例是DUT控制、激励和响应捕捉。在这种情况下,仪器无需直接测试高速串行协议,而是使用高速串行协议从DUT发送或接收数据,以便对设备的其他方面进行测试。此外,辅助数字I/O可用于使用并行或低速串行协议(如SPI)控制DUT。

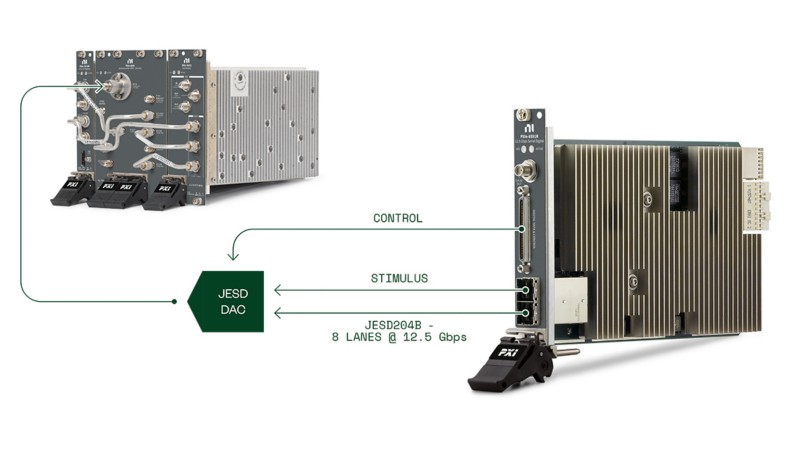

在以下范例中,PXIe-6591使用JESD204B协议激励DAC,以测试DAC的模拟输出特性。

图8. 许多现代高性能DAC和ADC都包含使用JESD204B高速串行协议的通信。

高带宽数据移动

许多高性能嵌入式应用都可从PXI平台中受益,并满足其在第三方硬件和NI PXI设备之间实现高带宽、低延迟的数据移动需求。对于这些应用而言,PXI高速串行仪器提供了诸如LabVIEW FPGA硬件处理、P2P数据流传输至PXI Express仪器以及高带宽流盘等优势,同时通过标准高速串行协议向外部设备提供高带宽连接。

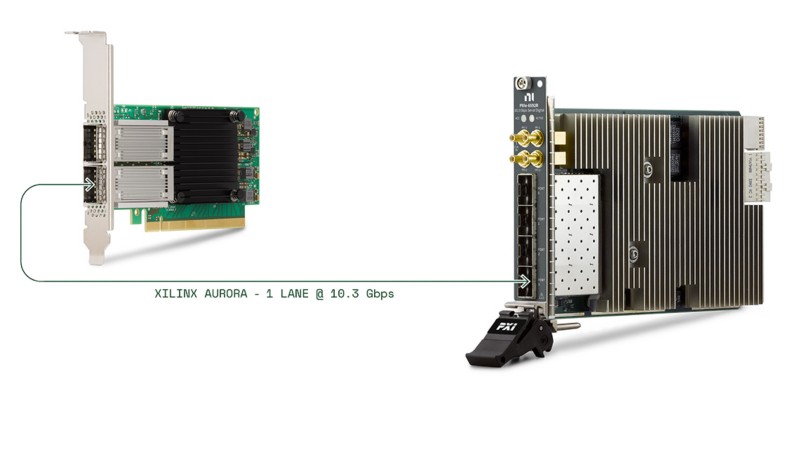

以下范例中,NI示波器对模拟信号进行采样,然后使用P2P数据流将原始数字化数据发送至PXIe-6592高速串行仪器。随后,仪器使用LabVIEW FPGA中实现的算法实时处理数据。最后,仪器使用专为FPGA至FPGA串行通信而设计的轻量级Xilinx Aurora协议将处理后的数据传输至第三方设备。

图9. PXI高速串行仪器是通过第三方设备实现高带宽、低延迟数据移动的出色解决方案。

链路调试和参数测试

由于高速串行接口使用的信号频率极高,因此如果信号完整性太差会使通信中断。出现此类问题时,可使用调试工具深入了解链路状态。设计人员可通过上文所述的眼图扫描仪器设计库确定接收信号的链路余量,并确定通信问题是否由信号完整性低所致。尽管该功能主要用于应用程序开发期间的调试,但其也可用于设备验证或制造测试,以深入了解设备专用的性能参数。但由于PXI高速串行仪器的幅值和定时精度均为标称值,因此NI不保证这些参数的性能或可追溯性。对于某些应用,用户可选择现场校准或调整。

其他参数测试包括使用行业标准模式(PRBS-7、PRBS-15、PRBS-23和PRBS-31)代替特定协议来测试已知伪随机位序列(Pseudo-Random Bit Sequence, PRBS)的误码率。可改变发射器和接收器的线速率,以确定特定DUT支持的比特率范围。最后,可通过改变发射器幅值以及预加重和后加重,测试接收器的灵敏度,包括自动增益控制和动态均衡。

对于PXIe-6591和PXIe-6592,可以通过以下链接在NI社区中获取详细资源:借助NI社区中的NI MGT调试工具,获取更多与PXI高速串行仪器配合使用的物理层分析工具。对于PXIe-6593和PXIe-6594,请参阅对PXIe-6593和PXIe-6594高速串行设备使用眼图扫描。

技能要求

尽管LabVIEW和LabVIEW FPGA极大地简化了高速串行技术的实现工作,但某些专业知识对于确保成功编程PXI高速串行仪器至关重要。由于需要使用LabVIEW完成相关设计,因此用户必须熟悉LabVIEW图形化编程。ni.com中的NI LabVIEW应用程序开发培训课程页面会为您提供相关帮助。此外,如需自定义LabVIEW FPGA中的非协议FPGA逻辑,还需要详细了解高吞吐量LabVIEW FPGA编程知识。NI LabVIEW高性能FPGA开发者指南资源有助于了解详细信息。 对于已有IP或范例的协议,定义协议IP和LabVIEW FPGA程序框图之间的接口需要具备VHDL知识和经验。最后,建议利用高级数字化设计专业知识实现新协议或自定义协议。部分NI合作伙伴可为内部缺少这些功能的用户提供帮助。NI当地销售代表可助您寻找合适的合作伙伴。

| 使用模型 | LabVIEW | 高吞吐量LabVIEW FPGA | VHDL | 丰富的数字化设计专业知识 |

| 使用现有属性 | — | — | — | |

| 可自定义FPGA代码,但不可自定义协议 | — | — | ||

| 集成现有协议 | — | |||

| 实现新协议或自定义协议 |

表4. 编程高速串行仪器需要不同级别的技能和工具,具体取决于接口所需的更改级别。

下一步

- 详细了解使用NI PXI高速串行模块最大程度实现数据移动和信号处理。

- 详细了解高速串行通信链路的基本概念。

- 请参阅在无线电收发仪功能测试系统中实现高速串行协议的参考设计范例。

- 请访问软件设计仪器与NI FlexRIO社区的范例和IP,获取硬件驱动程序中未包含的其他协议参考设计。

- 购买PXI高速串行仪器。

- 构建PXI系统。