数字状态、电压电平和逻辑系列

概览

了解数字状态、逻辑电压电平和数字信号的逻辑电平系列。本教程是仪器基础教程系列的一部分。

内容

数字状态

数字设备仅有2种状态:开和关。仅使用这2种状态,设备就可以传输大量数据并控制其他各种设备。这2种状态在二进制中表示为1或0。通常将二进制1视为逻辑高电平,而0是逻辑低电平。

电压电平

然而,数字设备通常由具备无限多状态的模拟设备驱动。如何将无数个状态变为仅2种状态?答案是创建电压逻辑电平,通过定义电压来表示逻辑高电平或逻辑低电平。

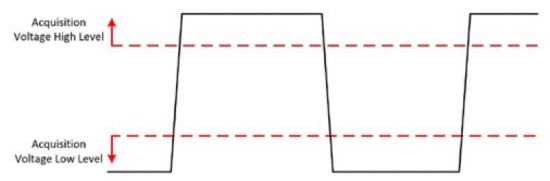

图1: 电压电平定义了表示逻辑高电平或逻辑低电平的模拟电压。

系统可将电压逻辑电平定义为任意值,但许多电路将逻辑高电平表示为+5 V或+3.3 V接地,逻辑低电平表示为接地或0 V。此类系统称为正电平系统或高电平有效系统。它阐述了引脚的激活方式,即对于高电平有效引脚,将其连接至高电压。

而负电平系统或低电平有效系统则相反。较高的电压表示逻辑低电平,较低的电压表示逻辑高电平。对于低电平有效引脚,则必须通过将其接地来拉低电压。数据表通常在引脚名称上加一条线来表示引脚是否为低电平有效,例如EN。

虽然明确了高电平和低电平,但在大多数系统中,为了更加实用,实际上都会设置一个范围。例如,逻辑高电平可能是2 V至5 V之间的任意值,逻辑低电平可能是0 V至1 V之间的任意值。超出这些范围的电压均可视为无效,且仅在故障条件下或逻辑电平转换过程中出现。

Z和X状态

虽然数字信号只能有2种状态(开和关),但您可使用其他状态来帮助采集和生成数字信号。在三态逻辑下还有第3种可能情况:即输出与线路断开连接的高阻抗状态。该状态既非高电平也非低电平,而是一种浮动状态或高阻抗状态。可用符号Z表示,通常用作起动信号线。

Z状态最常见的用途是测试一条或多条可由多个发射器驱动的数字线路。存储芯片上的数据端口就是很好的示例。计算机向存储设备写入数据时,需要通过存储设备的数据引脚(0或1)驱动待写入存储芯片的数据。之后,当计算机处理器需要读取存储器的内容时,存储设备需要将之前存储的数据值驱动回计算机处理器(通常为数据引脚上的Z状态)。

第4种状态是用X表示的保持状态。在生成数字信号时,无论通道处于何种状态,设备都可将其保持在当前状态。该状态在设置初始或空闲状态时非常有用。

采集数据时,X状态也可以称为“忽略”。将采集的数字信号与预期信号进行比较时,该状态很有用。例如,对于某个信号,您可能只关心10个值信号中的前4个值。您可将X状态用于最后6个值,仅用比较前4个值。

| 状态 | 名称 |

|---|---|

| 0 | 逻辑低电平 |

| 1 | 逻辑高电平 |

| Z | 高阻抗 |

| X | 保持状态或忽略 |

表1: 数字信号只能处于高电平或低电平状态;但是,Z和X状态有助于生成或采集数字信号的应用。

逻辑系列

标准化逻辑系列可以简化电路和组件的使用。它们提供了用于构成逻辑高电平或逻辑低电平的标准化电压电平。因为具有相同的特性,逻辑系列中的所有电路都与同一系列中的其他电路兼容。

单端逻辑系列

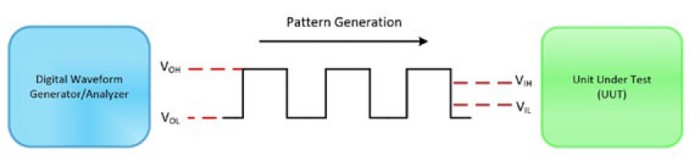

单端逻辑系列指定相对于地的电压电平。4个电平的定义如下:

- VOH(输出高电平电压)-也称为生成高电平电压。在配置有源驱动生成时,该电压为设备在生成逻辑高电平时产生的电压。在配置集电极开路生成时,相当于将数据通道设置为高阻抗状态。

- VOL(输出低电平电压)-也称为生成低电平电压。该电压为设备在生成逻辑低电平时产生的电压。

- VIH(输入高电平电压)-也称为采集高电平电压。该电压为发送至设备以读取逻辑高电平所需的电压电平。

- VIL(输入低电平电压)-也称为采集低电平电压。该电压为发送至设备以读取逻辑低电平所需的电压电平。

图2: 为输出和输入指定单端逻辑电平。

为实现与设备的准确通信,请务必配置数字设备,使其满足以下条件:

- VOH ≥ DUT VIH

- VOL ≤ DUT VIL

- VIH ≤ DUT VOH

- VIL ≥ DUT VOL

- VIH > VIL

一台设备的输出电压和另一台设备的输入电压区间通常存在缓冲。这称为噪声容限或噪声抗扰度(NIM)。如您身处嘈杂的环境且难以处理不正确的数据位,请考虑增加该值。

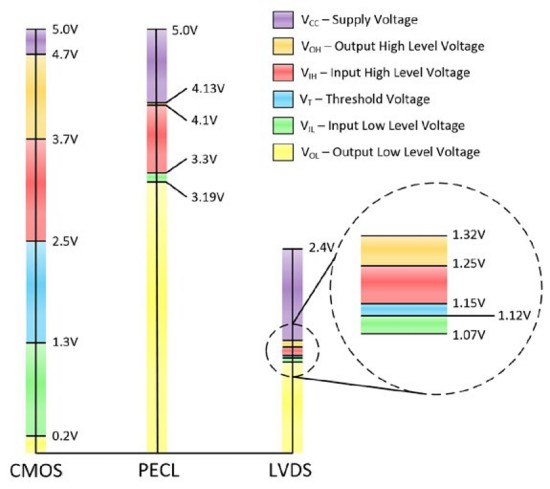

单端逻辑系列有多种。晶体管-晶体管逻辑(TTL)在集成电路中非常常见,用于计算机、消费类电子设备和测试设备等多种应用。由双极晶体管构建的电路可实现逻辑状态的切换和保持。TTL还必须满足特定的电流规范和上升/下降时间,请参阅TTL兼容信号的定义是什么?一文以了解详细信息。

图3: 标准5 V TTL电压电平

另一个常见的IC系列是CMOS。这些设备具有较高的抗噪性,功耗较低,并且具备较低的基极电压。大多数电压电平与TTL设备相似,具有更高的兼容性。因此,可以轻松将TTL设备切换至CMOS设备,但反向切换会比较棘手。CMOS的电压过高可能会损坏芯片。这种情况下,可以使用分压器来降低电压。

图4: 标准CMOS电压电平

差分逻辑系列

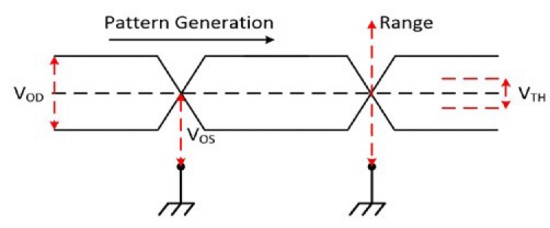

单端逻辑系列使用相对地的设定电压电平;而差分逻辑系列使用的是两个值之间的差值,而非参考接地。对于被视作逻辑低电平的差分信号,该信号必须小于其互补信号并超过某特定阈值(VTH)。由于信号可共同参考并传输,因此与使用单端逻辑系列相比,信号的抗噪性更高。差分逻辑系列的电压电平通常是由差分电压而非绝对电压指定。4个电平的定义如下:

- VOD(输出差分电压)-信号之间的电压差。

- VOS(偏移电压)-差分信号的常见模式。可将其视为2个信号的平均值。并参考接地。

- VTH(阈值电压)-设备注册有效逻辑状态所需的电压差。

- VRANGE(输入电压量程)-设备允许的以接地为参考的绝对电压。

总结

- 电压逻辑电平定义了表示逻辑高电平或逻辑低电平的电压。

- 许多电路将逻辑高电平表示为+5 V或+3.3 V接地,逻辑低电平表示为接地或0 V。此类系统称为正电平系统或高电平有效系统。

- 在三态逻辑中,Z状态为高阻抗状态,通常用作起动信号线。

- 在数字生成中,X状态可保持当前逻辑电平。在数字采集中,其表示忽略状态。

- 逻辑系列提供了用于构成逻辑高电平或逻辑低电平的标准化电压电平。

- TTL基于VCC=5 V

- CMOS基于VCC=3.3 V

- 差分逻辑系列使用2个值之间的差分,而非参考接地。

- LVDS是一种低噪声、低功耗、低幅值的差分方法,VCC=3.3 V。

- LVPECL电路是ECL电路的一种,它的每条通道都需要一对信号线(VCC=3或3.3 V)。