基于NI Vision Development模块的FPGA视觉产品简介

概览

借助FPGA技术和NI Vision Development模块,您可以对采集的相机图像进行高速现场可编程门阵列(FPGA)处理。FPGA处理尤其适用于要求图像采集和处理之间具有低延迟的应用。本文概述了如何在FPGA上进行图像处理及其典型的应用场景。

内容

FPGA编程简介

NI LabVIEW FPGA模块是LabVIEW图形化编程环境的扩展模块。您可以使用VHDL等底层语言进行复杂的FPGA编程。但是如果您熟悉LabVIEW,则可快速学会使用LabVIEW FPGA。这可大幅缩短FPGA编程应用的开发时间,避免需要定制硬件设计。与使用HDL进行编程不同,您可以在LabVIEW程序框图界面上创建应用程序,LabVIEW FPGA会合成图形化代码并将其部署到FPGA硬件上。

在FPGA上处理图像

许多图形处理算法具有内在并行性,因此适用于在FPGA上实现。这些算法包含对感兴趣的像素、行和区域进行运算,不需要图案(pattern)等高级图像信息。这些函数可以在多个小区域的位上或图像的多个区域上同时执行。图像数据也可以并行传输到FPGA并同步进行处理,这是因为数据的处理不需要使用中央处理器。NI Vision Development模块包含50多个图像处理函数,可结合NI LabVIEW FPGA模块使用,在FPGA上处理图像。 以下列出了Vision Development模块中可在FPGA上使用的几个图像处理函数示例:

预处理

| 特征抽取

测量

|

Vision Development模块FPGA函数概述

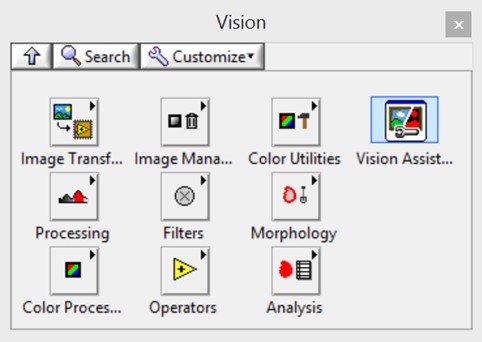

Vision Development模块与NI LabVIEW FPGA模块一起安装后,“视觉”(Vision)选板就会包含用于FPGA图像处理应用的函数。

图1. “视觉”(Vision)选板包含了多个用于FPGA图像处理应用的函数。

“视觉”(Vision)选板包含了图像变换VI,用于在FPGA和CPU之间传输图像。第二部分“FPGA视觉的应用场景”探讨了不同的应用场景以及为什么图像在传入或传出CPU时有时需要进行图像转换。

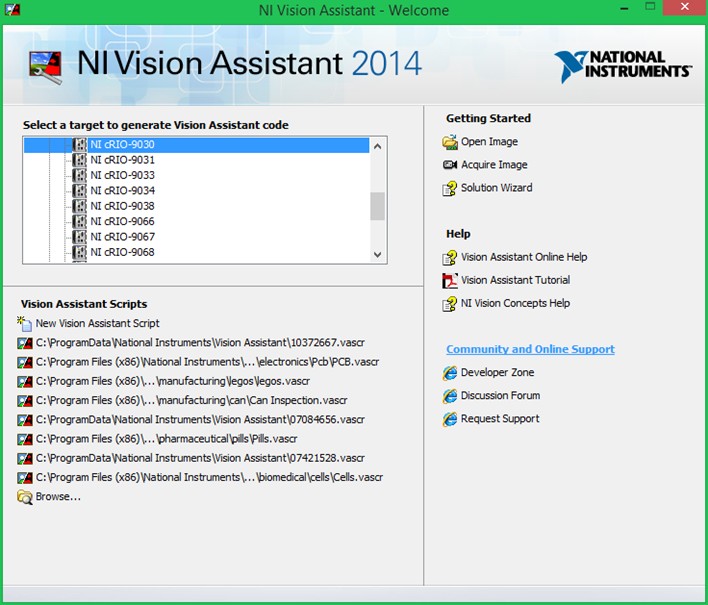

NI Vision Development模块包含Vision Assistant Express VI,该VI可通过握手和同步自动生成LabVIEW FPGA图像处理代码,无需编写底层同步代码。您可以在LabVIEW程序框图中打开Vision Assistant,也可以将其作为一个独立的程序打开来创建针对特定NI硬件的LabVIEW项目。

图2. Vision Assistant可作为一个独立的程序打开,以生成针对特定硬件的代码。

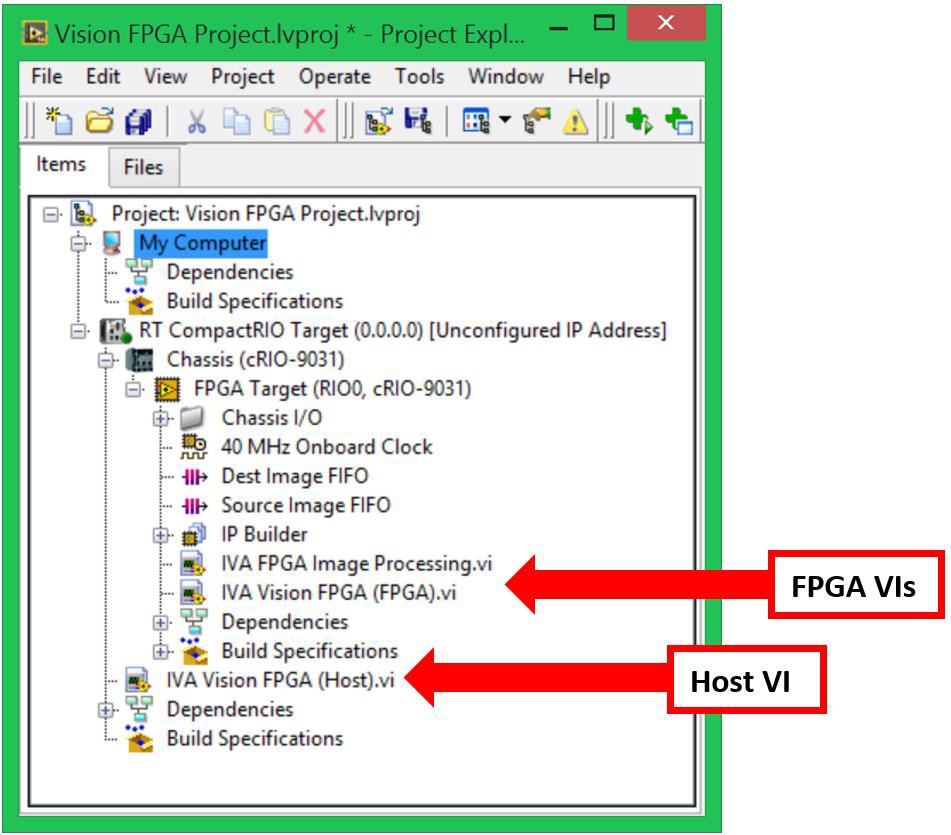

选择好硬件之后,Vision Assistant会估算出图像处理脚本所需的FPGA资源,然后生成一个包含一个主机VI和FPGA VI的LabVIEW项目来进行图像处理和转换。

图3. 创建图像处理脚本之后,Vision Assistant将自动生成一个包含硬件终端、主机VI(如果指定的话)和FPGA VI的LabVIEW项目来进行图像处理和转换。

FPGA视觉的应用场景

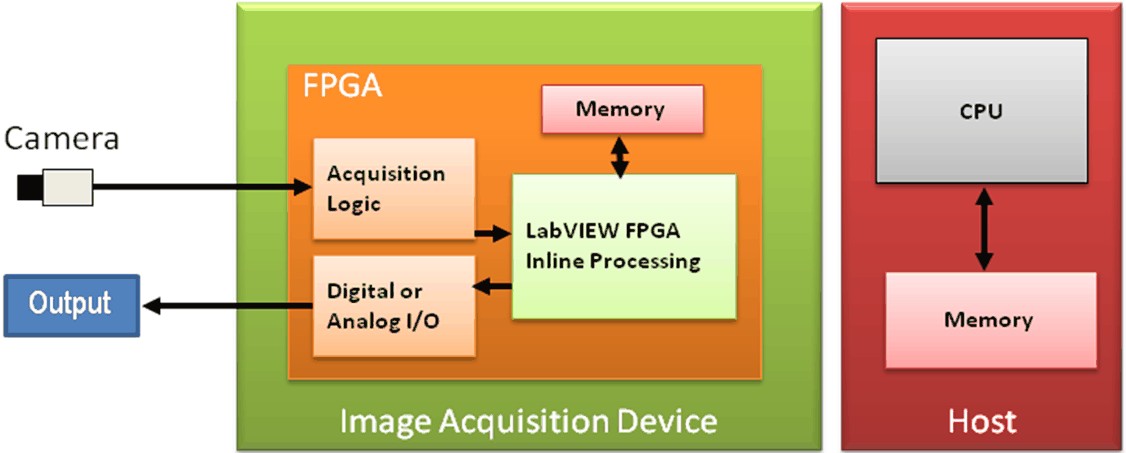

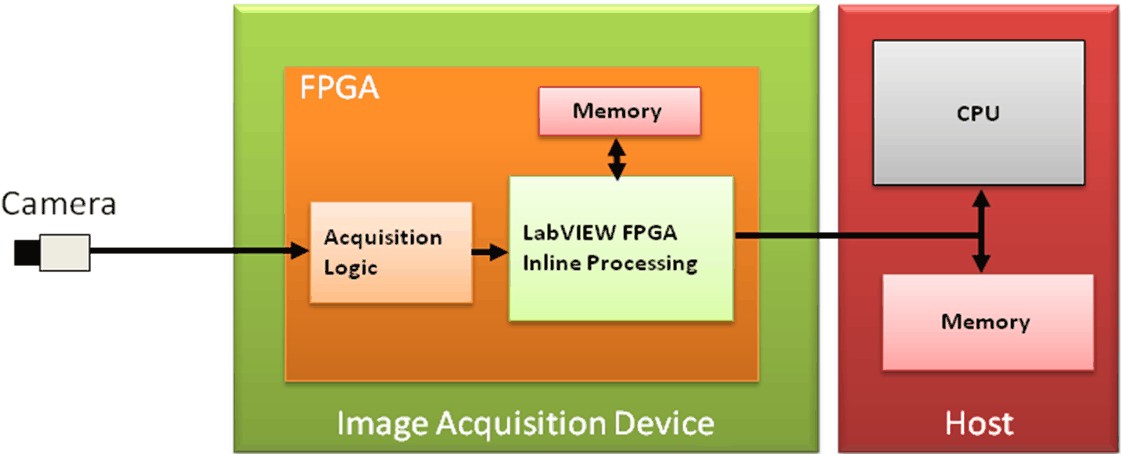

应用场景1:仅使用FPGA进行处理,以实现高速控制

FPGA图像处理可降低图像分析所需的运算处理资源。由于FPGA是一个硬件资源,因而可将CPU资源释放出来,用于执行其他运算。执行分析时不需要CPU的干预,因此大大降低了从图像处理到控制信号输出之间的延迟。图4显示的例子可帮助您了解如何使用FPGA来释放CPU资源。在本例中,FPGA执行所有的图像处理并生成输出信号。这使得系统延迟降到最低,从而能够快速生成控制信号。

图4.所有处理任务均在终端的FPGA上执行。这使得CPU能够执行其他任务,从而最大程度降低系统延迟。

应用场景案例包括高速分类、眼球追踪、激光对准。 仅FPGA的处理可在帧接收器上实现,只需在图像数据输入路径上直接放置一个FPGA即可。两个典型的产品是Camera Link帧接收器和Camera Link适配器模块。

图5. Camera Link帧接收器和Camera Link适配器模块将FPGA放置在图像路径中,适用于板载预处理和高速控制应用。

应用场景2:FPGA预处理

基于FPGA的视觉系统处理器还可用于执行更多处理任务。图6介绍了如何使用FPGA来进行预处理,同时在CPU上执行更高级的处理算法。在此应用场景中,FPGA执行的是位处理,比如滤波或边沿检测。经预处理的图像发送至CPU进行图像级处理,比如图案识别。在本例中系统延迟依然非常低,因为CPU执行的函数数量要比传统视觉系统少得多。

图6.图像采集和预处理在FPGA上执行后,图像数据传输至CPU。CPU执行更复杂的图像分析,例如图案匹配和分类。

FPGA图像处理尤其适用于需要高速位级处理的应用。FPGA接收图像数据后使用高速板载时钟(时钟速率高达100 MHz)处理每个位。您可在单个时钟周期内同时使用硬件进行数据传输和数据处理。多个视觉算法可以分为多个迭代任务,然后在FPGA上并行执行。

此类架构适用于表面和幅材检测和光学相干断层扫描(OCT)等应用。 图5显示了两个能够实现FPGA预处理的帧接收器。

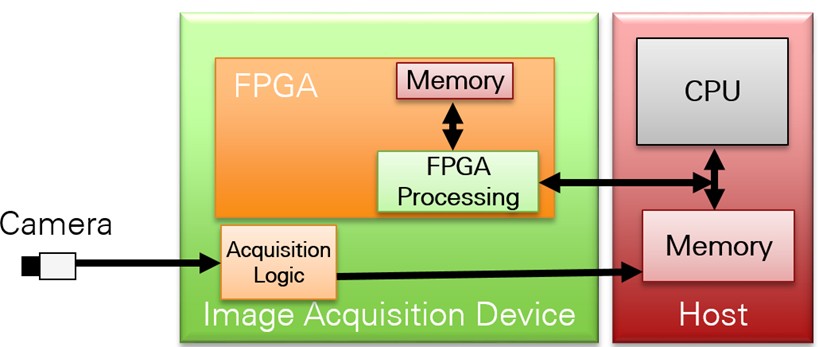

应用场景3:FPGA协处理

在某些情况下,图像处理算法可能包含多个步骤。一部分步骤,如阈值处理,可以在FPGA中实现。其它步骤,如图案匹配,可能更适合在CPU上执行。在这种情况下,您可以将任务从处理器转移到FPGA。 如图7所示,所采集的图像发送到CPU后,便逐个像素传输到FPGA进行位级运算。像素在FPGA上处理后可发送回CPU进行其他处理。

如果算法可以完全在FPGA上执行,则像素不需要发送回CPU。在这种情况下,您可以使用FPGA来生成基于图像处理算法结果的输出,或将处理结果发回CPU以便系统的其他部分使用。结果数据可以是距离测量值、颗粒计数或图像处理步骤的任何其他结果。FPGA协处理通过尽可能减少CPU执行的函数数量来降低系统延迟。

图7. 图像采集和预处理在FPGA上进行后,图像数据传输至CPU。CPU执行更复杂的图像分析,例如图案匹配和分类。

FPGA协处理可在CompactRIO控制器以及在Camera Link帧接收器和Camera Link适配器模块上实现。

FPGA协处理的一个应用是质量检验时的颗粒计数。在该应用中,颗粒计数任务可以在FPGA上运行以确定颗粒的数目及大小。然后这个信息可以与处理器共享,以便显示给操作员或用作其他进程的输入。

总结

总之,FPGA的高速运算和并行特性可缩短图像处理时间,从而降低系统延迟和提高吞吐量。此外,FPGA图像处理可以允许高速分拣机等系统的控制器更快速地基于所采集的图像作出决策。另外,得益于嵌入式处理领域的最新发展,3D视觉现已广泛应用于各种机器自动化领域。