NI USRP 하드웨어는 어떻게 작동합니까?

개요

NI Ettus USRP (범용 소프트웨어 라디오 주변 장치) 디바이스는 무선 RF 어플리케이션에 사용되는 소프트웨어 정의 라디오 (SDR)입니다. NI Ettus USRP 트랜시버는 여러 대역에서 RF 신호를 송수신할 수 있으며, 통신 교육 및 연구 어플리케이션에 사용할 수 있습니다. USRP는 LabVIEW 개발 환경과 결합되어 OTA (over-the-air) 신호를 사용하여 무선 알고리즘을 검증할 수 있는 저렴한 솔루션을 제공합니다.

내용

소프트웨어 정의 라디오

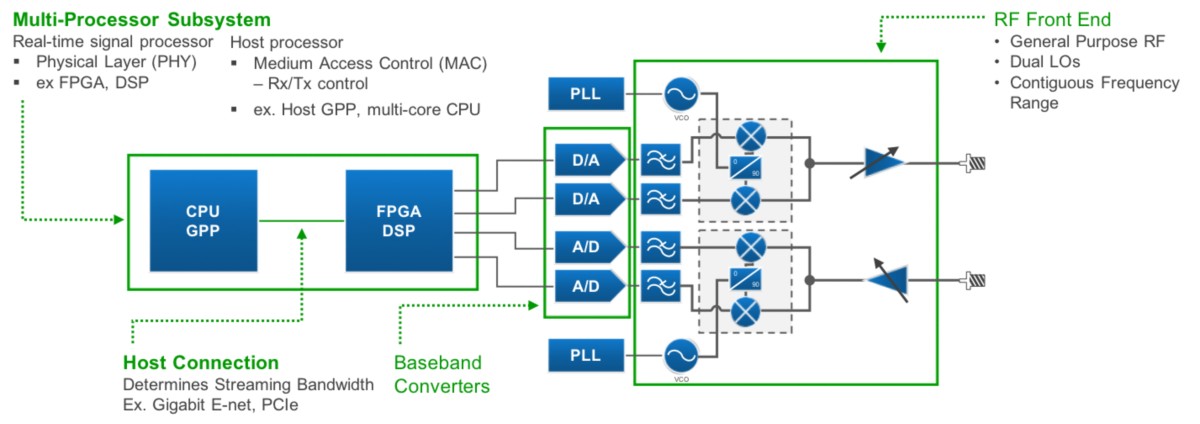

SDR 아키텍처에는 일반적으로 프로세서가 내장되어 있든 컴퓨터에 있든 상관없이 FPGA와 튜닝 가능 RF 프런트엔드가 포함되어 있습니다. USRP 및 LabVIEW는 교육 실험실 및 통신 연구를 위해 이상적인 SDR 프로토타이핑 솔루션을 제공하는 유연성, 기능 및 저렴한 제품을 제공합니다.

그림 1: 소프트웨어 정의 라디오의 일반적인 아키텍처

LabVIEW는 USRP 하드웨어와 스트리밍되는 신호의 변조 및 복조를 위한 신호 처리 엔진을 제공합니다. LabVIEW Real-Time 및 LabVIEW FPGA Module을 추가하여 같은 개발 환경에서 NI Linux Real-Time OS 및 FPGA를 모두 타겟으로 할 수 있습니다. 또한 LabVIEW는 실제 무선 신호에 최적화된 많은 일반적인 아날로그 및 디지털 변조 기술과 신호 처리 알고리즘을 위한 기능 블록을 제공합니다.

일반적인 어플리케이션

USRP 하드웨어는 다양한 어플리케이션에서 작동합니다. 하드웨어의 유연성과 경제성 덕분에 이 제품은 교육에서부터 다이나믹 스펙트럼 액세스, 화이트스페이스, PHY 및 MAC 계층 연구를 포함한 고급 무선 연구에 이르기까지 사용할 수 있습니다. 이 제품은 사용자 정의 프로토콜을 만들거나 스펙트럼을 디스크에 로깅하기 위한 간단한 전송 또는 수신 어플리케이션에도 유용합니다.

하드웨어 개요

3a. 호스트 전용 USRP

그림 2: NI USRP-2921

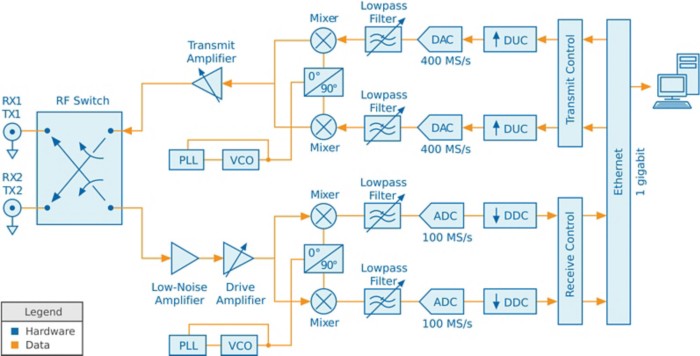

일반적인 SDR 아키텍처에 따라 USRP 하드웨어는 고속 아날로그-디지털 변환기 (ADC)와 디지털-아날로그 변환기 (DAC)로 직접 변환 아날로그 프런트 엔드를 구현하며, 디지털 다운 변환 (DDC)과 디지털 업 변환 (DUC) 단계를 위한 고정된 특성의 FPGA를 갖추고 있습니다. 리시버 체인은 아주 작은 신호도 수신할 수 있으며 직접 다운 변환을 사용하여 이러한 신호를 동위상(I) 및 직교위상(Q) 기저대역으로 디지타이징 할 수 있는 높은 민감도의 아날로그 프런트 엔드로 시작합니다. 다운 변환 후, 고속 아날로그-디지털 변환 및 DDC를 사용하여 샘플링 속도를 줄이고 I 및 Q를 패킷으로 묶은 다음 추가적인 처리를 위해 기가비트 이더넷을 통해 호스트 컴퓨터로 전송합니다. 트랜스미터 체인은 I와 Q가 생성되어 이더넷 케이블을 통해 USRP 하드웨어로 전달되는 호스트 컴퓨터에서 시작됩니다. DUC는 신호가 DAC를 통과할 수 있도록 준비하며, 그 이후에는 I-Q 믹싱이 일어나 신호를 직접 업 변환하여 RF 주파수 신호를 생성합니다. 이 주파수 신호는 다시 증폭되어 전송됩니다.

그림 3: USRP-2921 시스템 레벨 다이어그램

3b. 프로그래밍 가능한 FPGA가 탑재된 USRP 디바이스

그림 4: NI USRP-2944

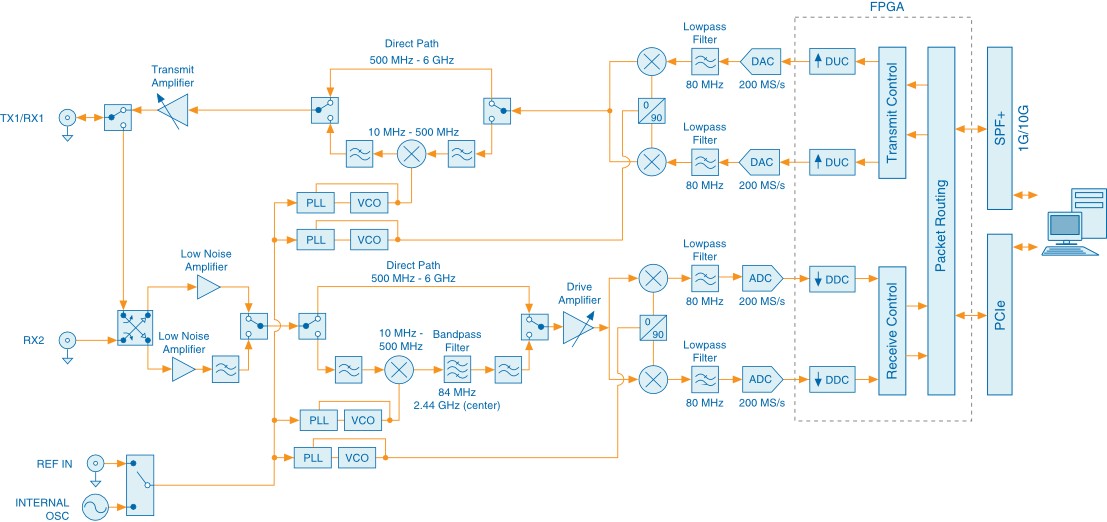

NI USRP-294x/295x 디바이스는 채널당 160 MHz까지 리얼타임 대역폭을 갖춘 2개의 전이중 송수신 채널과 대형 DSP 기반 Kintex 7 FPGA를 1U 반폭의 랙에 마운트할 수 있는 폼 팩터에 결합한 제품입니다. 아날로그 RF 프런트엔드는 120 MS/s로 클럭 설정된 듀얼 ADC와 DAC를 통해 대형 Kintex 7 410T FPGA와 인터페이스합니다.

각 RF 채널에는 TX1 RX1 포트를 사용하여 하나의 안테나에서 시분할 이중통신 (TDD) 작업을 하거나 TX1과 RX2의 두 포트를 사용하여 주파수분할 이중통신 (FDD) 작업을 할 수 있는 스위치가 포함되어 있습니다.

NI USRP-294x/295x 디바이스는 외부 디바이스를 제어할 수 있도록 사용자가 프로그래밍 가능한 디지털 IO 라인과 함께 10 MHz에서부터 6 GHz까지 이르는 주파수 범위를 지원합니다. Kintex-7 FPGA는 속도가 높고 지연이 짧은 어플리케이션을 위해 DSP48 코프로세서가 통합된 재구성 가능한 LabVIEW FPGA 타겟입니다. 시스템 컨트롤러의 뒷면에 있는 PCI Express x4 연결부는 데스크탑이나 PXI 새시로 최고 800 MB/s, 노트북으로 최고 200 MB/s 속도의 스트리밍 데이터 전송을 지원합니다. 이 연결부는 케이블을 통해 최대 17개의 USRP 디바이스까지 하나의 PXI Express 섀시에 연결할 수 있도록 해주며, 이러한 디바이스들을 다시 데이지 체인 연결하여 대역폭이 넓은 다채널 어플리케이션을 구현할 수 있습니다.

그림 5: USRP-2944 시스템 레벨 다이어그램

3c. NI USRP-2974 독립형 디바이스

그림 6: NI USRP-2974

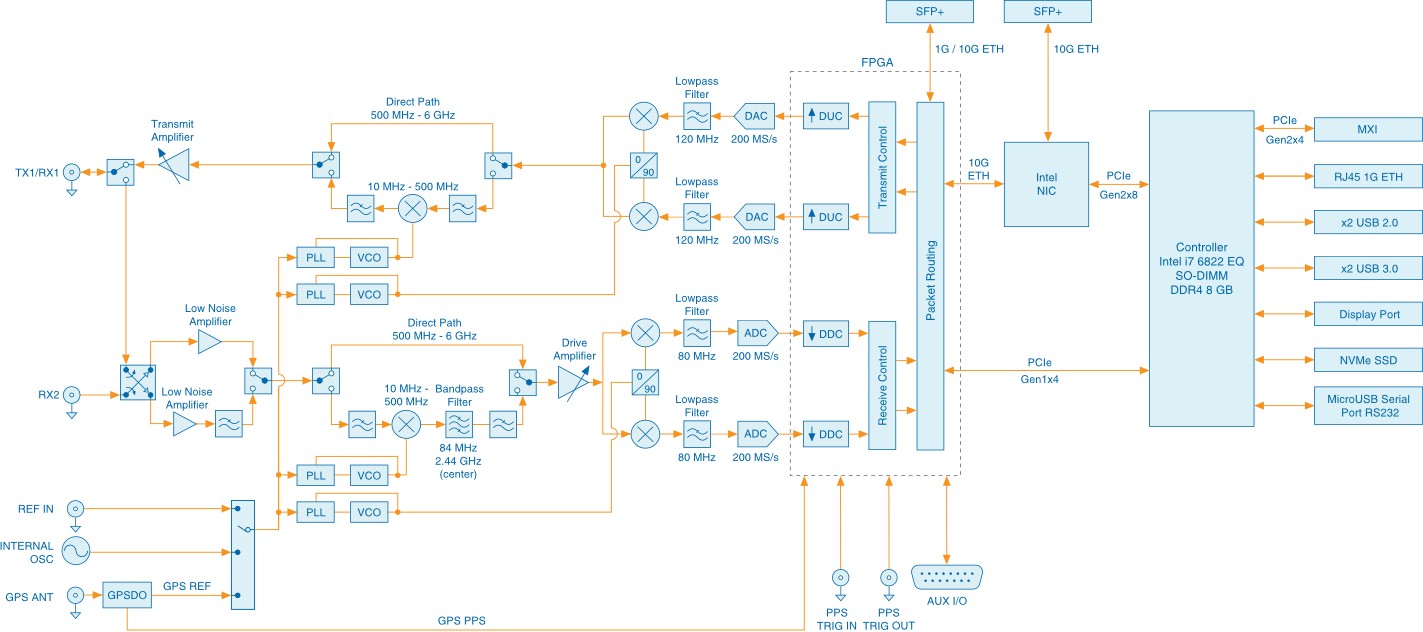

독립형 NI USRP-2974에는 온보드 프로세서, FPGA 및 RF가 모두 하나의 폼 팩터에 포함되어 있습니다. USRP-2974는 NI Linux Real-Time OS를 실행하는 온보드 Intel Core i7 프로세서가 있는 이기종 처리 아키텍처를 기반으로 구축되었습니다. 이는 160 MHz 대역폭으로 10 MHz ~ 6 GHz 사이의 주파수를 지원하고 x86 프로세서를 추가하여 독립 시스템 작동을 형성하는 2x2 라디오입니다. 이를 타겟으로 하여 모두 하나의 설계 환경에서 Xilinx Kintex 470 FPGA를 결정적으로 수행하고 프로그래밍할 수 있습니다. USRP-2974에는 또한 GPS 기반 10 MHz 오븐 제어형 수정 오실레이터 (OCXO: Oven-controlled crystal oscillator) 참조 클럭이 탑재되어 있습니다.

그림 7: USRP-2974 시스템 레벨 다이어그램

소프트웨어 개요

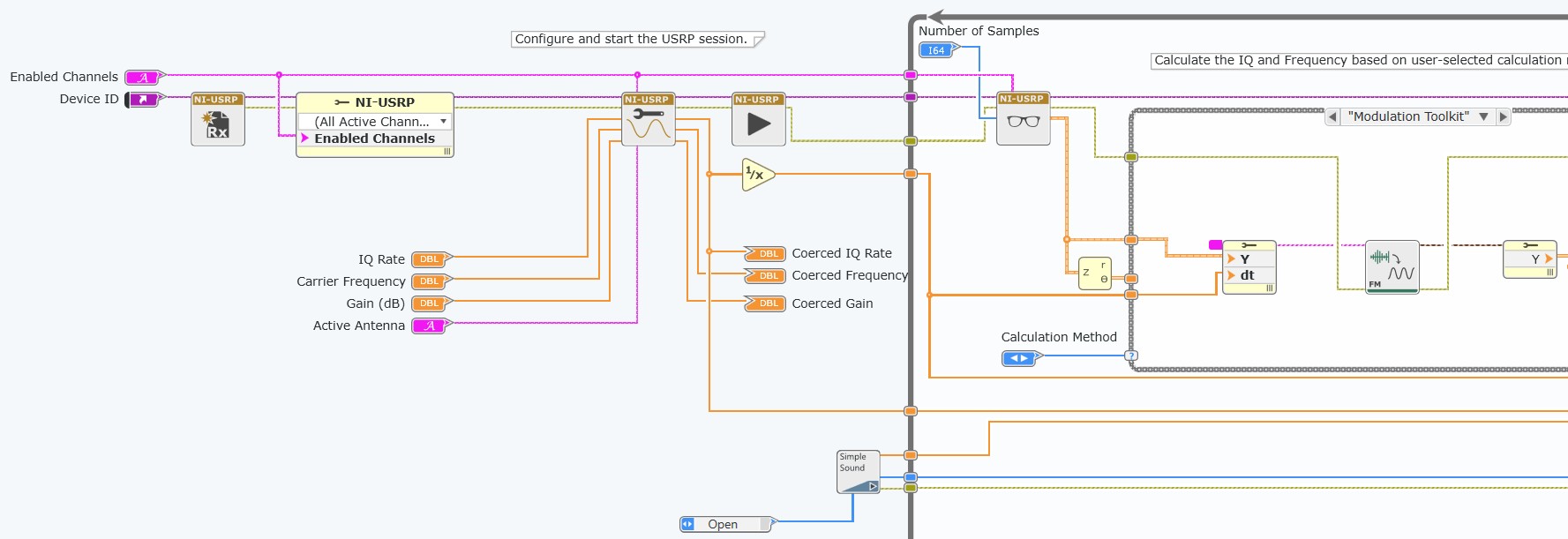

LabVIEW는 통신 알고리즘을 설계하고 구현하는 데 적합한 그래픽 데이터 흐름 프로그래밍 환경입니다. 가장 기본적인 레벨에서 LabVIEW는 NI-USRP 드라이버를 사용하여 USRP 하드웨어 설정을 지정하고 적절하게 포맷된 기저대역 I/Q 데이터를 송수신합니다.

그림 8: USRP 드라이버 API가 있는 LabVIEW 블록다이어그램의 스크린샷

다음 단계

Linux® 등록 상표는 전 세계에 상표권을 보유하고 있는 Linus Torvalds와 독점 라이센스 계약을 맺고 있는 LMI의 2차 라이센스에 따라 사용되었습니다. MATLAB®은 The MathWorks, Inc.의 등록 상표입니다.