NI USRP RIO 소프트웨어 정의 라디오 개요

개요

NI USRP RIO는 차세대 5G 무선 통신 시스템을 개발하는 무선 통신 개발자에게 저럼한 가격에 유래없는 성능을 갖춘 SDR을 제공하여 SDR 시장에 혁신을 일으킨 제품입니다. “USRP RIO"는 USRP-294x 및 USRP-295x와 같은 FPGA를 포함한 USRP 소프트웨어 정의 라디오 디바이스를 설명하는 데 사용하는 용어입니다. 이 디바이스는 최신 2x2 MIMO RF 트랜시버와 LabVIEW로 프로그래밍 가능한 DSP 기반 Kintex 7 FPGA를 갖추고 있습니다. LabVIEW는 무선 통신 개발자들이 프로토타입을 더욱 신속하게 제작하고 결과를 도출하는 시간을 크게 단축할 수 있도록 일관된 설계 흐름을 제공해 줍니다. NI USRP RIO는 USRP 플랫폼을 더욱 확장하여 사용자가 SDR 프로토타이핑을 더욱 손쉽게 수행할 수 있도록 한 것으로, 성능과 능률적인 소프트웨어 툴 흐름이라는 두 가지 장점을 골고루 갖추고 있습니다. 5G 무선 통신, Massive MIMO, 스펙트럼 모니터링을 비롯한 여러 가지 영역의 다양한 어플리케이션에 이상적인 제품입니다.

내용

- USRP RIO 아키텍처

- 최적화된 RF 성능

- 타이밍 및 클럭 분포

- 연결 옵션

- NI-USRP 소프트웨어 드라이버

- 코드 공유 커뮤니티

- USRP RIO 소프트웨어 정의 라디오 데모 보기

USRP RIO 아키텍처

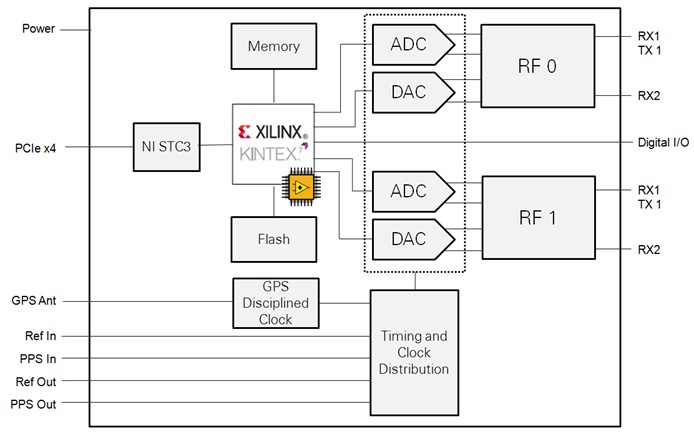

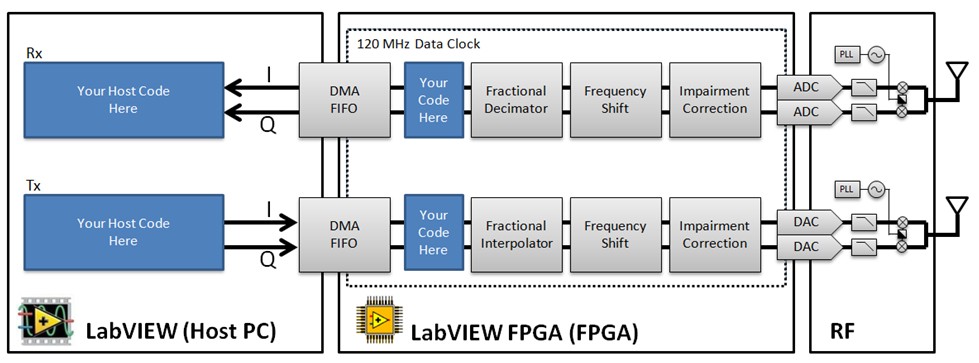

NI USRP RIO SDR 플랫폼은 채널당 40MHz의 리얼타임 대역폭을 갖춘 2개의 전이중 송수신 채널과 대형 DSP 기반 Kintex 7 FPGA를 1U 반폭의 랙에 마운트할 수 있는 폼 팩터에 결합한 제품입니다. 아날로그 RF 프런트 엔드는 120MS/s로 클럭 설정된 듀얼 ADC와 DAC를 통해 대형 Kintex 7 410T FPGA와 연결됩니다.

각 RF 채널에는 TX1 RX1 포트를 사용하여 하나의 안테나에서 시분할 이중통신(TDD) 작업을 하거나 TX1과 RX2의 두 포트를 사용하여 주파수분할 이중통신(FDD) 작업을 할 수 있는 스위치가 포함되어 있습니다.

USRP RIO 디바이스는 외부 디바이스를 제어할 수 있도록 사용자가 프로그래밍 가능한 디지털 IO 라인과 함께 50MHz에서 6GHz에 이르는 주파수 옵션을 가지고 있습니다. Kintex 7 FPGA는 속도가 높고 지연이 짧은 어플리케이션을 위해 DSP48 코프로세서가 통합된 재구성 가능한 LabVIEW FPGA 타겟입니다. 시스템 컨트롤러의 뒷면에 있는 PCIe Express x4 연결부는 데스크탑이나 PXI 새시로 최고 800MB/s, 노트북으로 최고 200MB/s 속도의 스트리밍 데이터 전송을 지원합니다. 이 연결부는 케이블을 통해 최대 17개의 USRP RIO 디바이스까지 하나의 PXI Express 섀시에 연결할 수 있도록 해주며, 이러한 디바이스들을 다시 데이지 체인 연결하여 대역폭이 넓은 다채널 어플리케이션을 구현할 수 있습니다.

그림 1. USRP RIO 시스템 블록 다이어그램

최적화된 RF 성능

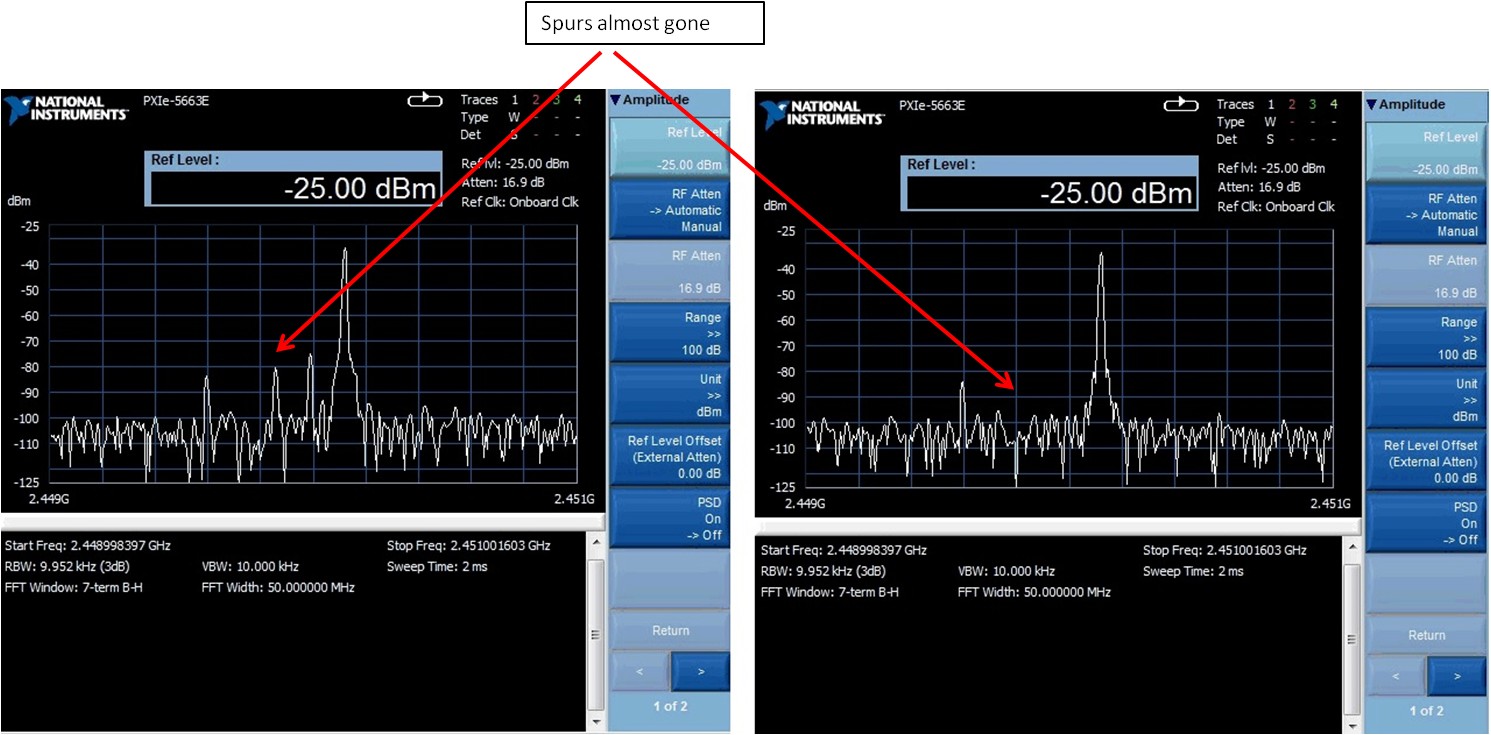

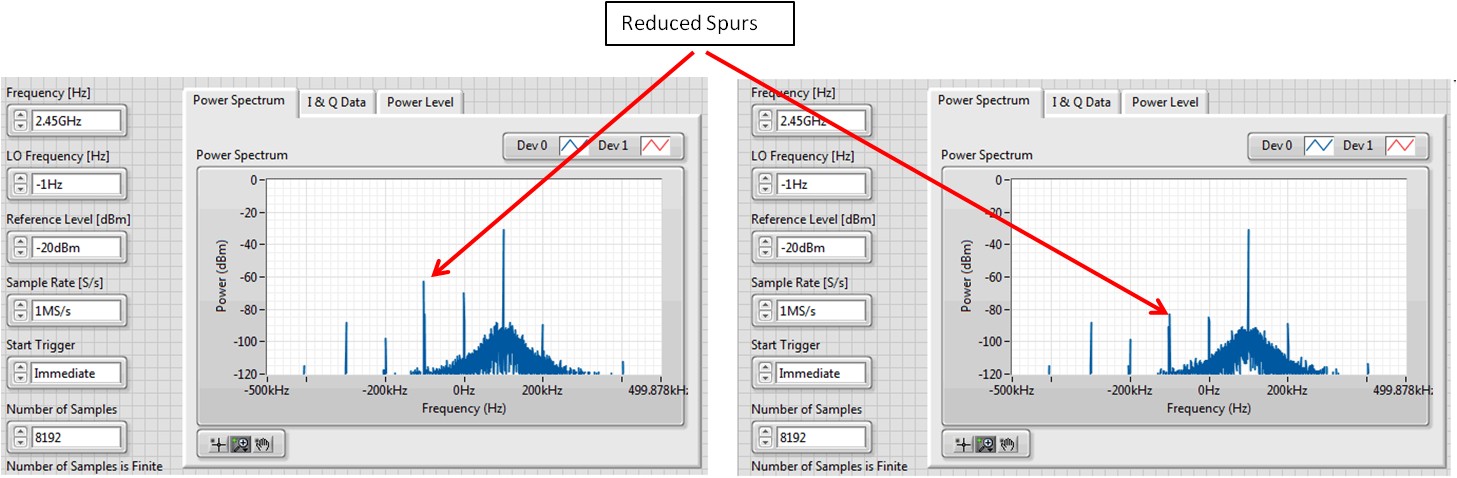

USRP RIO의 RF 성능은 제조 시에 결정되며, I/Q 불균형, DC 오프셋, 절대 정확도를 보상하기 위해 디바이스의 EEPROM에 교정 상수가 명시되어 있습니다. 이러한 보정 인자는 LabVIEW FPGA 샘플 스트리밍 프로젝트 및 파생 프로젝트를 사용할 때만 FPGA에 의해 기저대역 I/Q 데이터에 로드되고 디지털로 적용됩니다.

이러한 보정을 적용하면 디바이스가 신호를 송신하는지 수신하는지에 관계 없이 LO와 이미지 스퍼가 크게 개선되며 디바이스의 전체 작동 주파수 범위에 걸쳐 +/- 3dB의 절대 전력 레벨 정확도가 향상됩니다.

그림 2는 2.45GHz에서 USRP-2953 송신기의 보정되지 않은 성능과 보정된 성능을 나타냅니다. 보정 결과, LO 및 이미지 스퍼가 거의 사라졌습니다.

그림 3은 USRP-2953에서 수신된 신호에 대한 LO 및 이미지 스퍼가 최대 17dB 개선되었다는 것을 보여줍니다.

그림 2. 2.45GHz에서 보정되지 않은 TX 성능 대 보정된 TX 성능

그림 3. 2.45GHz에서 보정되지 않은 RX 성능 대 보정된 RX 성능

타이밍 및 클럭 분포

USRP-294xR 디바이스에는 범용 오실레이터로도 잘 작동하는 TCXO(온도 제어 오실레이터)가 기본 주파수 참조로 포함되어 있습니다. USRP-295x 디바이스에는 GPS를 사용하지 않고도 정확한 주파수를 제공하는 정밀 GPS 기반 OCXO(GPSDO)가 내장되어 있으므로 GPS 위성 네트워크에 연동시키면 주파수 정확도가 크게 향상됩니다.

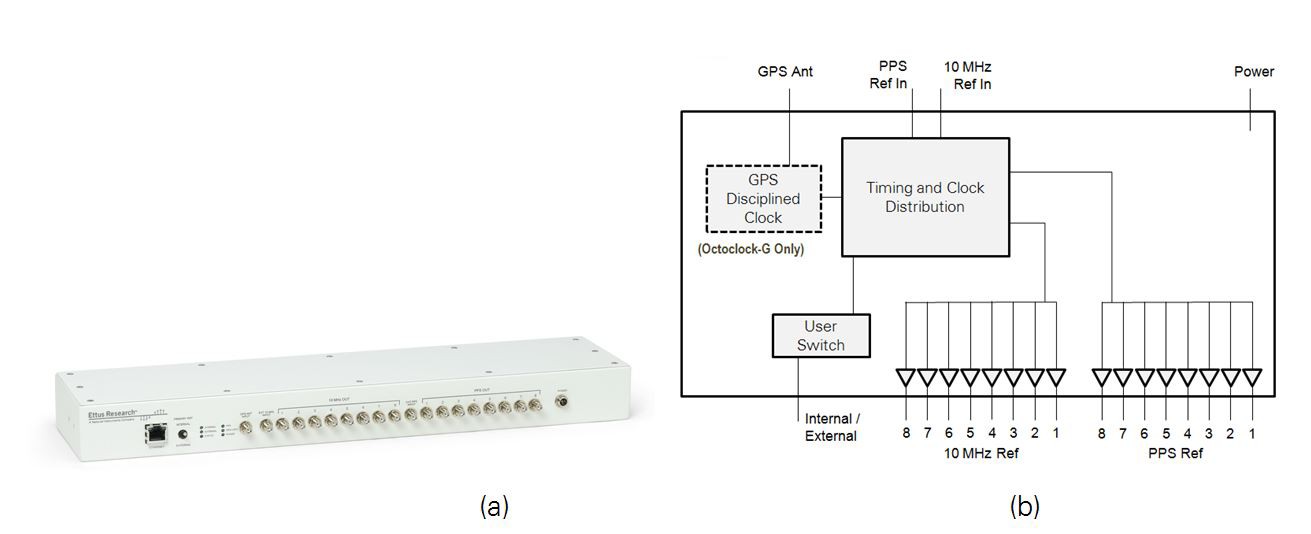

모든 USRP RIO 모델에는 내부 또는 외부 클럭 참조를 사용하는 옵션이 포함되어 있으며 클럭 참조와 타임 베이스를 반출할 수 있는 추가 기능도 제공됩니다. 참조 입력 포트는 ADC/DAC 클럭과 로컬 오실레이터가 파생되는 10MHz 참조를 수락합니다. PPS 입력은 표준 초당 펄스 포트 또는 범용 디지털 트리거 입력 라인으로 사용할 수 있습니다. 참조 출력 및 PPS 출력을 사용하면 더 높은 채널 카운트 시스템을 구축하기 위해 이러한 신호 중 하나를 내보낼 수 있습니다. 사용자는 8채널 OctoClock 및 NI PXIe-6674T를 사용하는 증폭된 클록 분포를 이용하여 참조 입력 및 PPS에 연결하여 대규모의 동기화된 시스템을 구축할 수 있습니다. 여러 Octoclock을 사용하여 동기화된 채널이 100개 이상인 시스템을 구축할 수 있습니다.

그림 4. OctoClock-G 모듈(a) 및 시스템 다이어그램(b)

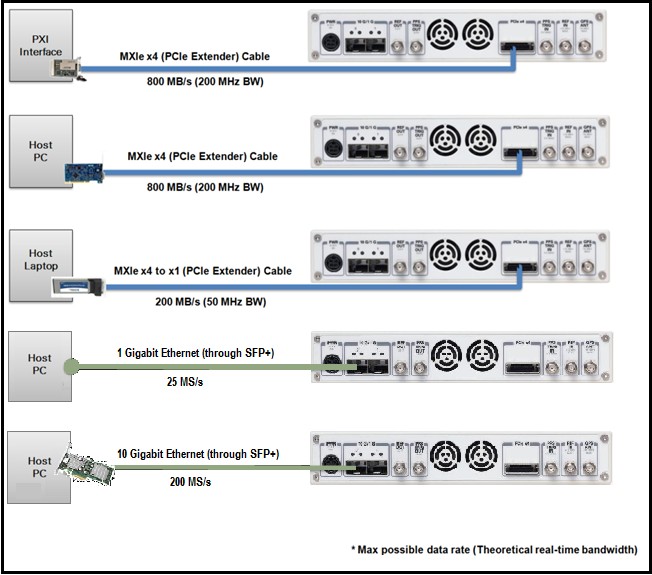

연결 옵션

USRP RIO의 주요 버스 인터페이스는 PHY/MAC 연구와 같은 고 대역폭 저 지연 시간 어플리케이션을 효과적으로 연결해주는 PCIe x4입니다. 이 버스를 통해 800MB/s의 속도로 데이터를 스트리밍하고 LabVIEW FPGA에서 FPGA를 맞춤 설정할 수 있습니다. 인터페이스는 USRP-292x 및 USRP-293x 디바이스용으로 작성된 프로그램과 역호환됩니다. LabVIEW의 NI-USRP 드라이버를 갖춘 USRP-294x/295x 디바이스도 디바이스 후면의 SFP+ 포트를 사용하여 1G 및 10G 이더넷을 통한 연결을 지원합니다. 하지만 이더넷을 통해 연결된 경우에는 FPGA를 수정할 수 없습니다.

그림 5. USRP RIO 인터페이스 옵션

그림 5는 USRP RIO를 노트북, 데스크톱 PC 또는 견고한 PXI 섀시에 연결할 수 있는 인터페이스 옵션을 보여줍니다. PXI 섀시에 연결하면 여러 개의 USRP RIO 디바이스가 P2P(Peer-to-Peer) 스트리밍을 사용하여 호스트를 거치지 않고도 PXI 섀시의 백플레인을 통해 데이터를 공유할 수 있습니다.

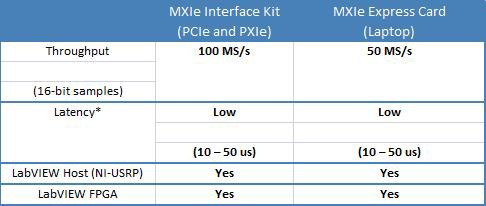

테이블 1. 다양한 연결 키트의 성능

NI-USRP 소프트웨어 드라이버

NI USRP RIO는 호스트 기반 드라이버(NI-USRP)와 오픈 기반의 맞춤 설정 가능한 LabVIEW FPGA(NI-USRP RIO)라는 서로 보완되는 두 개의 LabVIEW 기반 소트트웨어 드라이버 옵션을 제공합니다. 두 가지 드라이버 인터페이스 모두 PCI Express를 통한 연결을 지원하며 드라이버 작동 방법도 비슷하므로 사용자들은 효과적으로 설계를 호스트 컴퓨터에서 FPGA로 옮길 수 있습니다. 또한 NI-USRP는 USRP-294x/295x 디바이스에 대해 1G 또는 10G 이더넷을 통한 연결을 지원하지만, 이 설정에서는 LabVIEW FPGA를 사용할 수 없습니다.

NI-USRP 드라이버

NI-USRP 14.0 드라이버를 지원하는 NI USRP RIO 릴리스는 나중에 USRP-292x 및 USRP-293x 디바이스와 완전히 역호환되는 원활한 호스트 기반 인터페이스를 제공합니다. 호스트 API에서 설정할 수 있는 고정 FPGA 이미지를 사용하면 사용자가 LabVIEW에서 알고리즘을 개발하고 NI USRP와 NI USRP RIO 디바이스 사이를 원활하게 이동할 수 있습니다.

그림 6. NI-USRP 드라이버를 사용한 전형적인 스트리밍 어플리케이션(호스트만)

NI-USRP RIO 드라이버

어플리케이션의 성능을 향상해야 함에 따라 사용자는 NI USRP-RIO 드라이버를 통해 설계를 마이그레이션하여 대형 Kintex 7 FPGA를 공동 처리에 활용할 수 있습니다. NI USRP RIO 드라이버는 각각 LabVIEW와 LabVIEW FPGA에 작성된 개방형 호스트 프로세서와 FPGA 설계 코드를 포함하는 스트리밍 샘플 프로젝트를 제공합니다. 샘플 프로젝트의 설정을 조절하여 코드가 호스트에서만 실행되도록 하거나 FPGA 특성을 변경하여 맞춤형 프로세싱이 포함되도록 할 수도 있습니다. 전체 FPGA 참조 설계를 맞춤 구성할 수 있지만, 대부분의 경우 해당 코드를 DMA FIFO 근처의 신호 체인에 삽입합니다. 스트리밍 샘플 프로젝트는 NI FlexRIO SDR 및 NI 벡터 신호 트랜스시버(VST)에 공통적인 "인스트루먼트 설계 라이브러리" 참조 설계를 기반으로 합니다.

그림 7. NI-USRP RIO 드라이버를 사용한 전형적인 스트리밍 어플리케이션(호스트 및 FPGA)

코드 공유 커뮤니티

또한 NI-USRP 드라이버를 지원하면 USRP 코드 공유 커뮤니티에 포함된 코드를 재사용할 수 있습니다. 재사용 가능한 코드의 예로는 FM 라디오, ADS-B 수동형 레이더 신호 디코딩, 802.11b SSID 감지 등 여러 가지가 있습니다.

USRP RIO 소프트웨어 정의 라디오 데모 보기