Xilinx Kintex UltraScale을 탑재한 새로운 FlexRIO 모듈 소개

개요

내용

- 새로운 FlexRIO 아키텍처

- 통합, 메자닌 I/O

- Xilinx Kintex UltraScale FPGA 백엔드

- NI-TClk로 동기화

- 손쉬운 FPGA 프로그래밍

- 숙련된 디지털 엔지니어를 위한 Xilinx Vivado 지원

- 다음 단계

그림 1: 새로운 FlexRIO 모듈은 고속 직렬 컨버터를 사용하며, 하나의 디바이스에 통합 I/O와 Xilinx Kintex UltraScale FPGA 기술이 결합되어 있습니다.

새로운 FlexRIO 아키텍처

FlexRIO 제품군의 주요 장점은 기존 COTS 계측기에 아직 널리 도입되지 않은 최신 고속 데이터 컨버터 기술을 사용해 볼 수 있다는 것입니다. 이는 샘플링 속도, 대역폭, 해상도 및 채널 수에 대한 요구 사항이 갈수록 높아지는 어플리케이션에서 특히 유용합니다.

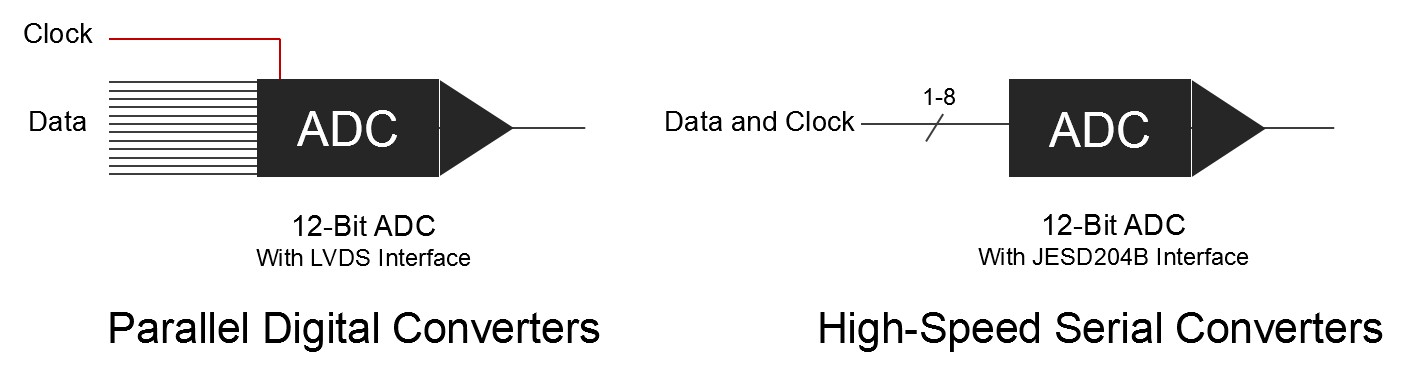

데이터 컨버터 제조사들은 RF 분야의 어플리케이션에 대한 성능 요구에 부응하여 고속, 고해상도 부품으로 계속적인 혁신을 일구고 있습니다. 이제 4GS/s에서 12비트 해상도로, 또는 500MS/s에서 16비트 해상도로 작동하는 아날로그-디지털 컨버터(ADC)나 디지털-아날로그 컨버터(DAC)를 흔히 볼 수 있게 되었습니다. 이러한 고속 부품은 다양한 어플리케이션에 유용하게 사용할 수 있긴 하지만, 최신 컨버터와 통신하기 위한 기반 기술은 저전압 차동 신호(LVDS) 인터페이스에서 JESD204B와 같은 프로토콜을 지원하는 고속 시리얼 인터페이스로 변화하고 있는 추세입니다.

그림 2: 기존 FlexRIO 아키텍처는 데이터 통신에 단일 종단 또는 LVDS 인터페이스를 사용하는 기존의 컨버터에는 매우 적합했습니다. 새로운 FlexRIO 아키텍처는 JESD204B와 같은 프로토콜을 지원하는 고속 시리얼 인터페이스 기반 최신 고속 컨버터와 연결되도록 설계되었습니다.

이러한 업계 트렌드에 뒤처지지 않고 계속해서 최신 상용 기술을 제공하기 위해 NI는 새로운 FlexRIO 아키텍처를 개발했습니다. 새로운 FlexRIO 제품은 기존 아키텍처의 병렬 디지털 인터페이스가 아닌 메자닌 I/O 모듈과 Xilinx Kintex UltraScale FPGA 백엔드 간의 고속 시리얼 통신을 기반으로 작동합니다.

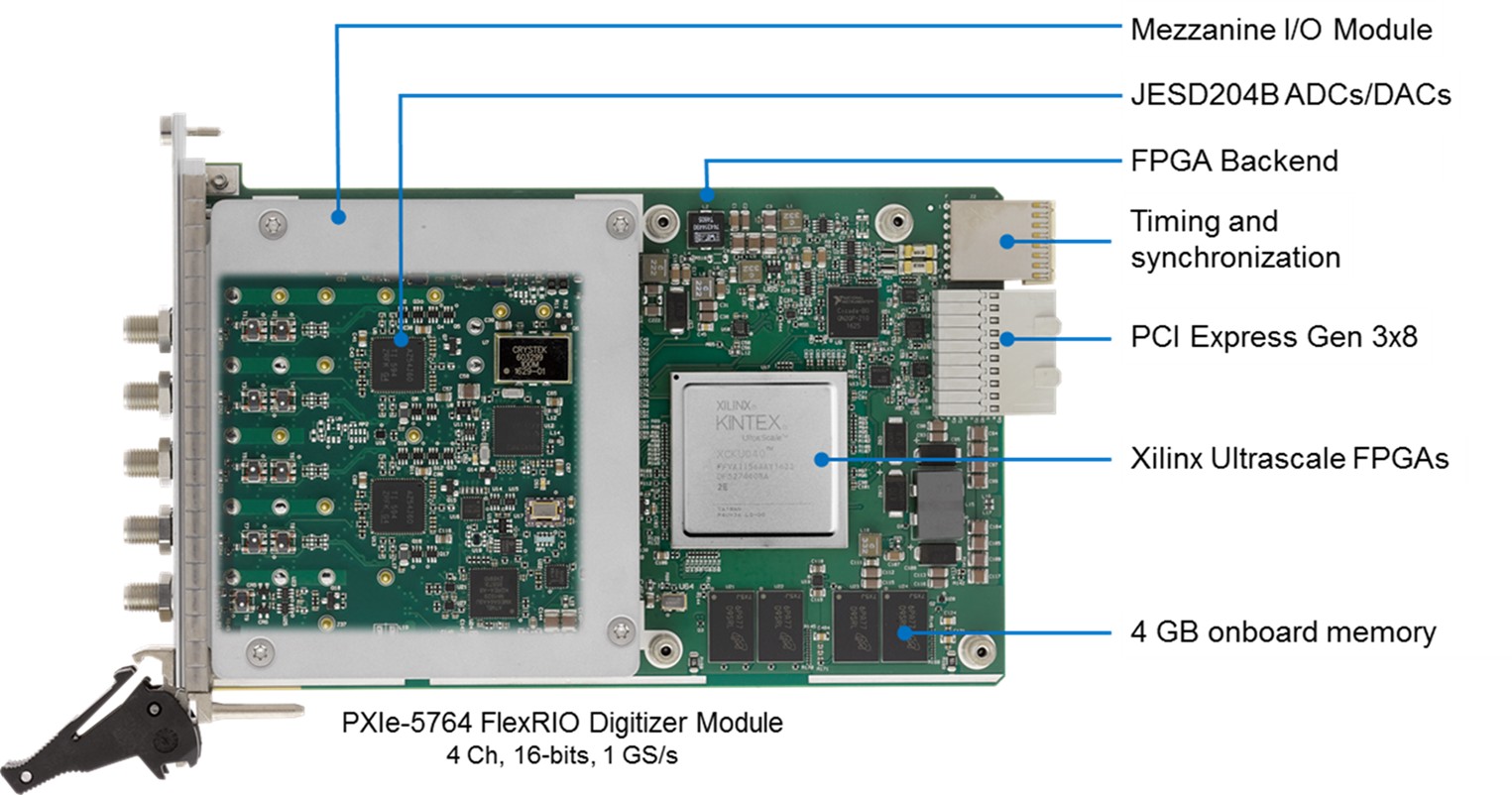

그림 3: 새로운 고속 시리얼 FlexRIO 제품은 Xilinx Kintex UltraScale FPGA 백엔드에 연결된 메자닌 I/O 모듈로 구성됩니다.

통합, 메자닌 I/O

고속 시리얼 통신이 FPGA의 멀티기가비트 트랜시버를 바탕으로 작동하기 때문에 FlexRIO FPGA와 I/O 모듈 간의 전기적 인터페이스를 처음부터 다시 설계해야 했습니다. 인터페이스에 메자닌 커넥터를 도입한다는 것은 I/O 모듈을 FPGA 백엔드에 직접 연결하여 하나의 통합된 PXI 모듈로 만들 수 있다는 뜻이었습니다. 그렇습니다. 새 FlexRIO 제품은 섀시 밖으로 튀어나오지 않습니다.

새로운 아키텍처에서는 FlexRIO 모듈이 메자닌 I/O 모듈의 기능에 상응하는 모델 번호로 식별됩니다. 따라서 각각의 요구 사항에 맞는 FPGA 백엔드를 선택할 수 있습니다. 일례로 PXIe-5764는 1GS/s에서 4개의 채널을 동시에 샘플링하는 16비트 FlexRIO 디지타이저입니다. PXIe-5764는 테이블 1에 명시된 3개의 FPGA 백엔드 옵션 중 하나와 연결할 수 있습니다.

테이블 1: 처음 두 개의 FlexRIO 디지타이저는 동적 범위, 샘플 속도, 채널 수의 강력한 조합을 제공합니다.

모델 | 채널 | 샘플 속도 | 해상도 | 커플링 | 대역폭 | FPGA 옵션 |

PXIe-5763 | 4 | 500MS/s | 16비트 | AC 또는 DC | 227 MHz | KU035, KU040, KU060 |

PXIe-5764 | 4 | 1GS/s | 16비트 | AC 또는 DC | 1.15GHz* | KU035, KU040, KU060 |

*전체 범위 입력 신호의 최대 대역폭은 400MHz입니다.

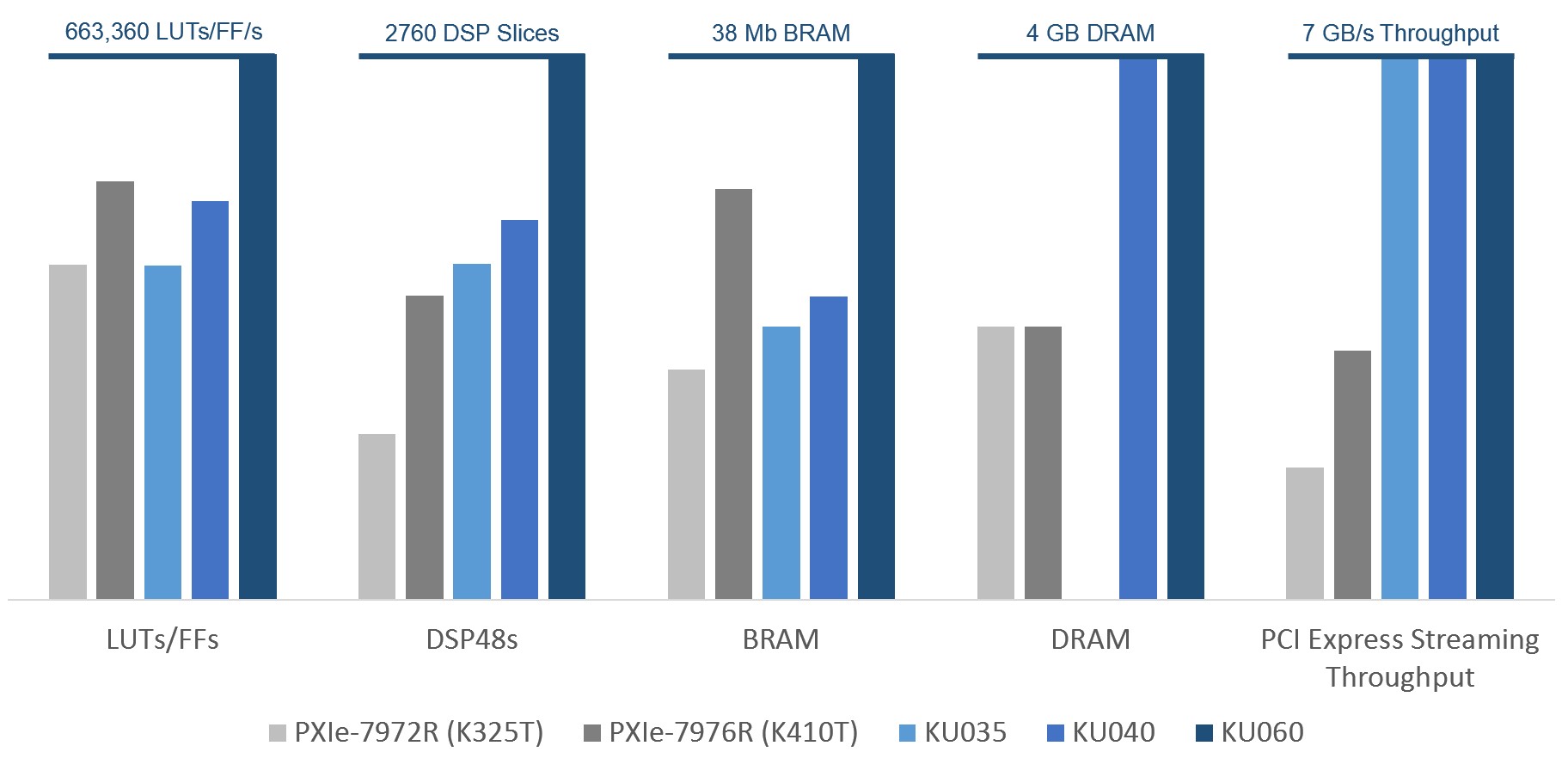

Xilinx Kintex UltraScale FPGA 백엔드

새로운 FlexRIO 제품은 Xilinx Kintex UltraScale FPGA를 사용하여 신호 처리 성능이 크게 높아졌습니다. Kintex UltraScale이 탑재된 FlexRIO는 80퍼센트 늘어난 디지털 신호 프로세서(DSP) 슬라이스, 30퍼센트 늘어난 BRAM, 데이터 스트리밍을 위한 PCI Express Gen 3 x8 연결로 PXI 분야의 FPGA 기반 신호 처리를 위한 새로운 기준을 정립합니다. 다양한 FPGA 백엔드 옵션 중에서 어플리케이션 요구 사항에 맞는 옵션을 선택할 수 있습니다. 단, 새로운 어플리케이션의 경우 가장 큰 FPGA로 시작하고 나중에 줄이는 것이 좋습니다.

테이블 2: 어떤 크기의 FPGA가 필요하십니까? 새로운 FlexRIO 제품은 세 가지 FPGA 백엔드 옵션을 제공합니다.

FPGA | LUT/FF | DSP48s | BRAM (Mb) | DRAM (GB) | PCI Express | 보조 I/O |

Xilinx Kintex UltraScale KU035 | 406,245 | 1,700 | 19 | 0 | Gen 3 x8 | 8 GPIO |

Xilinx Kintex UltraScale KU040 | 484,800 | 1,920 | 21.1 | 4 | Gen 3 x8 | 8 GPIO 4 GTH |

Xilinx Kintex UltraScale KU060 | 663,360 | 2,760 | 38 | 4 | Gen 3 x8 | 8 GPIO 4 GTH |

그림 4: 새롭게 선보이는 세 가지 UltraScale FPGA 옵션(파란색)은 FlexRIO용 Kintex-7 FPGA 모듈(회색)에 비해 더욱 다양한 가격대로 뛰어난 성능을 제공합니다.

새로운 FlexRIO 모듈은 PCI Express Gen 3 x8 연결을 지원하여 DMA를 통해 CPU 메모리로 최대 7GB/s의 왕복 스트리밍 속도가 실현됩니다. NI 피어 투 피어 스트리밍 기술을 사용하면 호스트 메모리에 데이터를 통과시키지 않고도 두 모듈 간에 데이터를 스트리밍할 수 있습니다. 피어 투 피어 스트리밍 기술에 대해 자세히 알아보십시오.

보조 I/O

모든 FPGA 백엔드 옵션에서는 트리거링이나 디지털 연결을 위한 전면 패널 보조 디지털 I/O가 Molex Nano-Pitch I/O 커넥터를 통해 지원됩니다. 크기가 큰 FPGA 백엔드에서는 각각 최대 16Gb/s의 데이터 스트리밍을 지원하는 4개의 추가적인 GTH 멀티기가비트 트랜시버가 Nano-Pitch I/O 커넥터로 라우팅됩니다. 이 트랜시버는 Xilinx Aurora, 10기가비트 이더넷 UDP, 40기가비트 이더넷 UDP 또는 SFPDP(Serial Front Panel Data Port)와 같은 고속 시리얼 프로토콜을 통해 다른 디바이스와 고대역폭으로 통신하는 데 사용할 수 있습니다.

전용 FlexRIO 코프로세서 모듈

기존 시스템의 신호 처리 역량을 높일 수 있는 코프로세서 모듈도 준비되어 있습니다. FlexRIO 코프로세서 모듈에는 최적의 열 성능을 위한 전용 부품이 탑재되어 있으며, PCI Express Gen 3 x8을 통한 백플레인 통신이나 프런트패널의 Nano-Pitch I/O 커넥터를 통한 고속 시리얼 통신을 지원합니다.

테이블 3: FlexRIO 코프로세서 모듈은 기존 시스템의 신호 처리 역량을 높여 줍니다.

모델 | FPGA | PCI Express | 보조 I/O |

PXIe-7911 | Kintex UltraScale KU035 | Gen 3 x8 | 없음 |

PXIe-7912 | Kintex UltraScale KU040 | Gen 3 x8 | 8 GPIO, 4 GTH |

PXIe-7915 | Kintex UltraScale KU060 | Gen 3 x8 | 8 GPIO, 4 GTH |

NI-TClk로 동기화

시스템에서 여러 모듈 사이의 동기화를 구현하는 작업은 아마도 채널이 많이 사용되는 솔루션 설계 시 겪게 되는 가장 어려운 일일 것입니다. 여러 COTS 벤더들의 동기화 솔루션이 존재하긴 하지만 확장이 불가능하며, 맞춤형 설계의 경우 여러 채널 간 위상 정렬을 하는 데도 고도의 전문 기술이 필요합니다. FlexRIO 모듈은 PXI 플랫폼에 내재된 타이밍 및 동기화 기능을 바탕으로 다른 계측기와 공유되는 클럭 및 트리거 경로에 직접 접근합니다. 새로운 FlexRIO 제품은 모든 모듈이 동일한 시작 트리거에 정렬되도록 동기화를 조정하는 NI-TClk를 지원합니다. NI-TClk 기술에 대해 자세히 알아보십시오.

그림 5: 새로운 FlexRIO 디지타이저 모듈은 NI-TClk를 지원하여 모듈 간 서브샘플 동기화를 수행합니다.

손쉬운 FPGA 프로그래밍

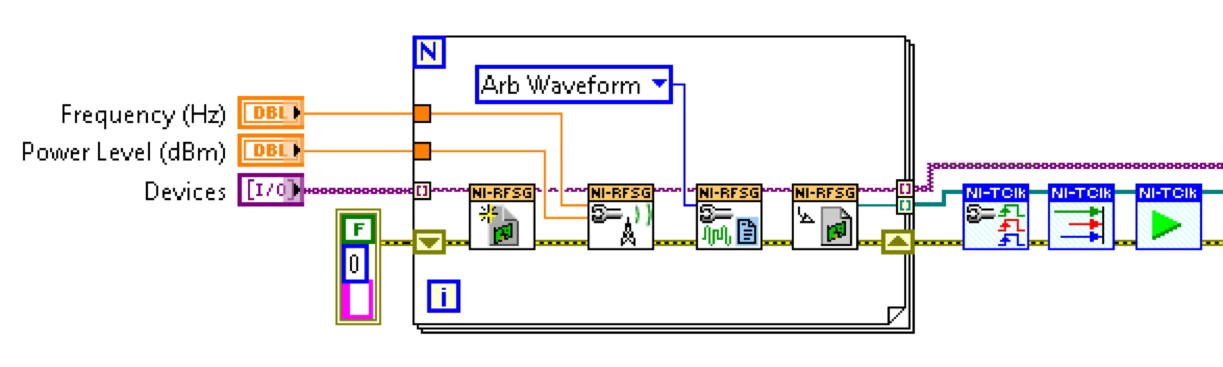

FPGA를 사용하는 계측기의 장점을 손쉽게 활용하십시오. 새로운 FlexRIO 제품에 적용된 소프트웨어는 맞춤형 FPGA 설계를 처음부터 구현하는 경우와 호스트 기반 스트리밍 드라이버에서 설계를 시작하는 경우를 모두 유연하게 지원합니다. 새로운 FlexRIO 스트리밍 드라이버는 FPGA 프로그래밍 없이도 기본적인 디지타이저 및 임의 웨이브폼 생성기 기능을 사용할 수 있도록 설계되었습니다. 이 드라이버는 아날로그 I/O를 지원하는 고속 시리얼 FlexRIO 제품에서 유한 또는 연속 수집/생성을 지원하며, FPGA를 보다 깊이 있게 사용자 정의하기 전에 개략적인 시작점으로 기능하도록 설계되었습니다. 기본적인 스트리밍 기능 외에도 이 드라이버를 이용하면 I/O 모듈의 아날로그 프런트 엔드, 클럭킹과 심지어 ADC나 DAC 대상 직접 레지스터 읽기/쓰기의 설정이 가능합니다.

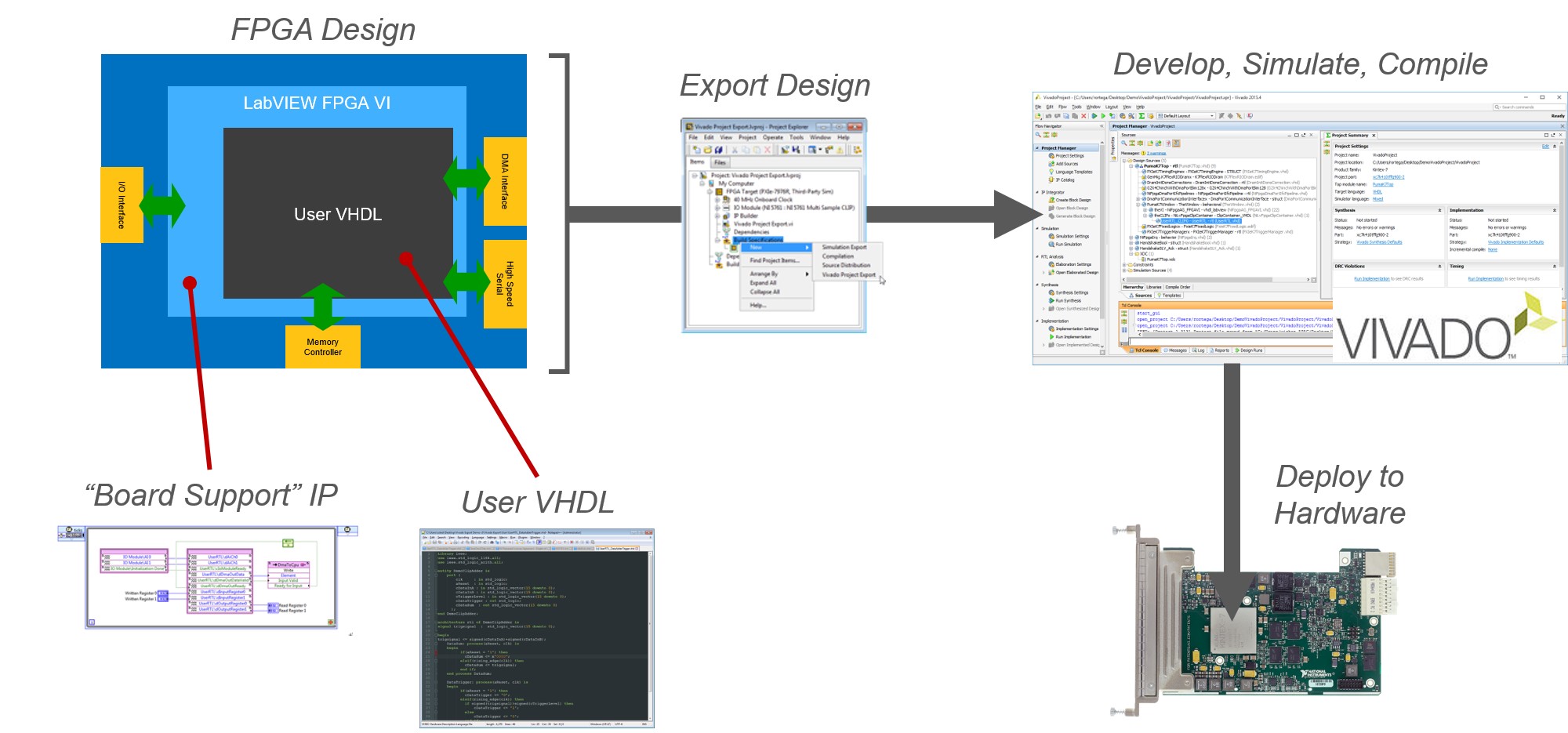

숙련된 디지털 엔지니어를 위한 Xilinx Vivado 지원

숙련된 디지털 엔지니어는 LabVIEW FPGA 2017에 포함된 Xilinx Vivado 프로젝트 내보내기 기능을 사용하여 Xilinx Vivado를 사용하는 FlexRIO 하드웨어를 대상으로 개발, 시뮬레이션 및 컴파일할 수 있습니다. 배포 타겟에 맞게 사전 구성된 Vivado 프로젝트로 필수 하드웨어 파일을 모두 내보낼 수 있습니다. 내보내기에는 LabVIEW 설계에 사용된 LabVIEW 신호 처리 IP가 모두 포함됩니다. 단, NI IP는 암호화된 상태로 포함됩니다. Xilinx Vivado 프로젝트 내보내기 기능은 Kintex-7이나 최신 FPGA가 적용된 모든 고속 시리얼 디바이스 및 FlexRIO에서 사용 가능합니다.

그림 6: 숙련된 디지털 엔지니어를 위해 제공되는 Vivado 프로젝트 내보내기 기능을 사용하면 개발, 시뮬레이션 및 컴파일을 위해 Vivado 프로젝트로 필수 하드웨어 설계 파일을 모두 내보낼 수 있습니다.