Xilinx CORE Generator IP 팔레트를 사용한 IP 재사용 증가

개요

소프트웨어 개발 생산성을 높이려면 효율적인 코드 재사용이 중요합니다. FPGA 하드웨어를 사용할 때, 재사용 가능한 코드 블록을 IP 블록이라고 부릅니다. NI LabVIEW FPGA Module은 제품의 IP 블록에 접근할 수 있는 다양한 방법을 제공합니다. LabVIEW FPGA Module이 수학 및 신호 처리를 위한 여러가지 내장된 함수를 제공하지만, 다른 소스의 상용 IP 라이브러리를 사용하는 것도 일반적입니다. LabVIEW 2011 FPGA Module과 이후 버전에는 Xilinx에서 개발하였고 Xilinx FPGA 하드웨어용으로 정밀 조정된 고성능 라이브러리 세트가 포함됩니다. FPGA 프로젝트 생산성을 증대하기 위해 Xilinx CORE Generator IP 팔레트의 기능과 사용 방법에 대해 자세히 살펴보십시오.

내용

- Xilinx CORE Generator 팔레트 요약

- Xilinx CORE Generator IP 블록 라이센스

- CORE Generator IP를 사용하여 개발할 때 고려사항

- CORE Generator IP 블록을 LabVIEW에 통합

- 타사 IP를 가져오는 다른 방법

- FPGA를 위해 최적화된 고급 기능

- 다음 단계

Xilinx CORE Generator 팔레트 요약

기본 기능

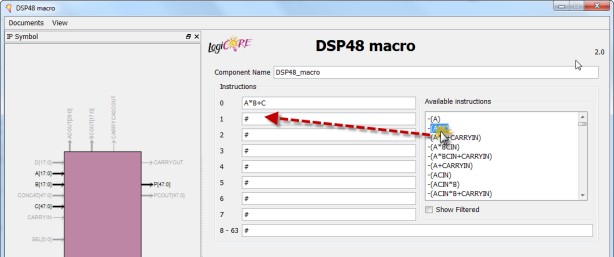

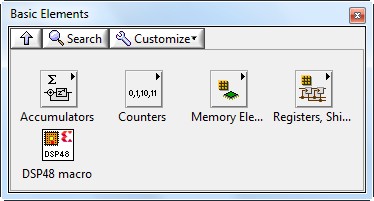

기본 IP 팔레트에는 고도로 최적화된 누적기, 카운터, 메모리 생성기 기능이 포함됩니다. 또한 DSP48 매크로 함수를 사용하면 설정 마법사를 통해 맞춤 IP를 생성할 수도 있습니다. 이 매크로 마법사는 지시, 파이프라인 설정, 포트 설정을 통해 DSP48를 맞춤화하는 방법을 단계별로 설명하여 수작업으로 복잡한 설정을 할 필요 없이 DSP48 성능을 활용할 수 있습니다.

그림 1: DSP48 매크로 함수를 사용하면 LabVIEW FPGA용 맞춤 IP 블록을 신속하게 설정하고 생성할 수 있습니다.

| IP 제품 페이지 IP | |

그림 2: BaseIP LabVIEW FPGA 팔레트 |

|

그림 3: 기본 요소 LabVIEW FPGA 팔레트 |

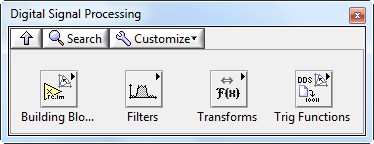

디지털 신호 처리 (DSP)

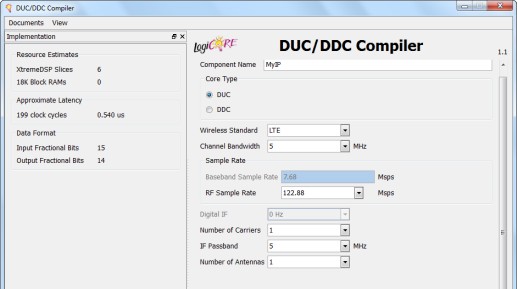

DSP CORE Generator 팔레트에는 신호 프로세싱 어플리케이션 개발을 가속화하기 위한 필터 및 변환 라이브러리가 포함됩니다. CORE Generator 마법사는 설정 기반이지만, 리소스 사용 추정, IP 심볼과 같은 다양한 파라미터를 제공함으로써 현재 포트 활용 상태를 명확하게 보여줍니다. 이같은 고도로 파라미터화된 방식 덕분에 맞춤 IP를 생성할 때 유연성과 효율성을 구현할 수 있습니다.

그림 4: Xilinx CORE Generator 대화창은 특정 어플리케이션의 요구사항에 맞게 코드를 맞춤 구성할 수 있도록 여러 IP 파라미터와 스펙을 제공합니다.

그림 5: 디지털 신호 처리 팔레트 | IP 제품 페이지 |

1CORE Generator IP 코어를 사용하려면 Xilinx 라이센스가 필요합니다. 더욱 자세한 정보는 IP 제품 페이지를 참조하십시오.

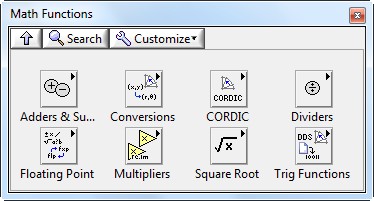

수학 함수

CORE Generator 팔레트 수학 함수는 기본 함수에서 고급 함수까지 다양합니다. 예를 들어, 팔레트에는 부동소수의 변환, 기본 연산을 위한 FPGA용 IP를 생성하는 블록이 있습니다. 그림 6과 같이 IP 설정 마법사를 사용하면 코드를 생성하고자 하는 부동소수 연산을 편리하게 선택할 수 있습니다.

그림 6: Xilinx CORE Generator Floating-point Operator IP 코어는 LabVIEW FPGA를 위한 부동소수 함수 라이브러리를 제공합니다.

그림 7: 수학 함수 팔레트 | IP 제품 페이지 |

|

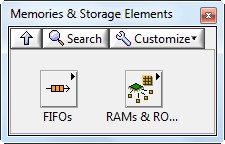

메모리 및 데이터 스토리지 요소

그림 8: 메모리 및 저장 요소 팔레트 | IP 제품 페이지 |

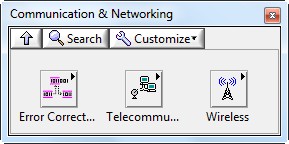

고급 산업별 팔레트

CORE Generator IP 팔레트에는 FPGA 설계 시간을 단축하기 위해 재사용할 수 있는 두 가지 통신 및 이미지 프로세싱 팔레트가 포함됩니다.

통신 및 네트워킹

그림 9: 통신 및 네트워킹 팔레트 | IP 제품 페이지 |

에러 수정 IP 비터비 디코더1 LTE FFT 1 무선 IP DPD1

|

1CORE Generator IP 코어를 사용하려면 Xilinx 라이센스가 필요합니다. 더욱 자세한 정보는 IP 제품 페이지를 참조하십시오.

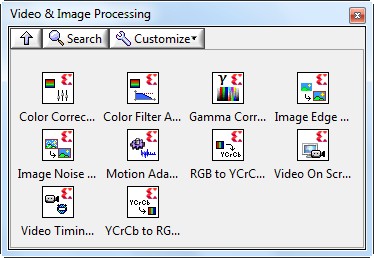

비전 및 이미지 프로세싱

그림 10: 비디오 및 이미지 프로세싱 팔레트 | IP 제품 페이지 |

|

감마 보정1

|

1CORE Generator IP 코어를 사용하려면 Xilinx 라이센스가 필요합니다. 더욱 자세한 정보는 IP 제품 페이지를 참조하십시오.

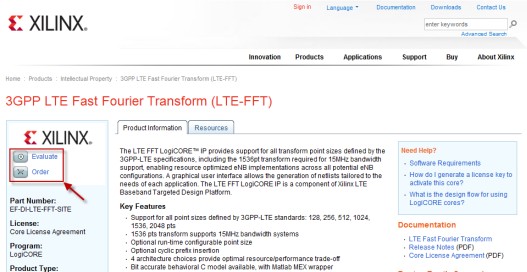

Xilinx CORE Generator IP 블록 라이센스

앞서 설명한 것처럼 일부 Xilinx IP 블록을 사용하려면 라이센스가 필요합니다. 라이센스 비용과 절차에 대한 자세한 내용은 위의 IP 블록 링크를 클릭하십시오.

그림 11: Xilinx IP 제품 페이지에는 라이센스가 필요한 CORE Generator 블록을 평가하고 주문하기 위한 정보가 제공됩니다.

CORE Generator IP를 사용하여 개발할 때 고려사항

LabVIEW FPGA의 다른 고성능 IP 블록처럼 어플리케이션에서 CORE Generator 라이브러리를 사용할 때도 고려해야 할 몇 가지 사항이 있습니다. CORE Generator IP는 단일 주기 Timed 루프에서만 실행됩니다. CORE Generator IP는 내부에서 고성능 수학 함수처럼 파이프라인된 경우가 많으므로 출력 데이터는 각 클럭에서 유효하지 않으며 IP 제어 신호 출력으로 데이터가 유효한 때를 알려야 합니다.

또한, Xilinx CORE Generator 라이브러리 지원은 Xilinx Virtex-5와 Spartan-6 FPGA로 제한되어 있으므로 이 FPGA 타겟 중 하나를 포함하는 NI 재구성 가능한 I/O 하드웨어를 사용해야 합니다.

더욱 자세한 내용은 제품 페이지에 있는 IP 블록 데이터 시트를 참조하십시오.

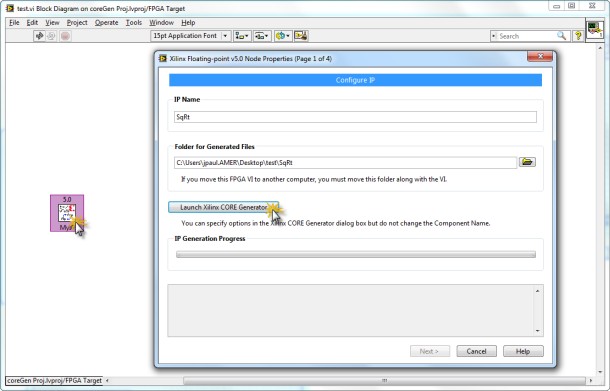

CORE Generator IP 블록을 LabVIEW에 통합

CORE Generator 팔레트에서 Floating-point Operator IP 코어를 사용하여 부동소수 제곱근 계산 수행

- 새로운 LabVIEW FPGA 프로젝트를 생성 (이 예제는 NI cRIO-9113 섀시에서 Virtex-5 FPGA 대상)합니다.

- 새로운 FPGA VI를 생성합니다. Programming»Xilinx Coregen IP»Math Functions»Floating-point를 선택한 후 부동소수 IP 코어를 FPGA 블록다이어그램으로 끌어갑니다.

VI를 저장하고 IP 블록을 더블클릭하여 Xilinx Floating-point v5.0 Node Properties 윈도우를 엽니다. CORE Generator IP 설정 마법사를 시작하기 위해 Launch Xilinx CORE Generator를 클릭합니다.

그림 12: Xilinx CORE Generator를 시작합니다.

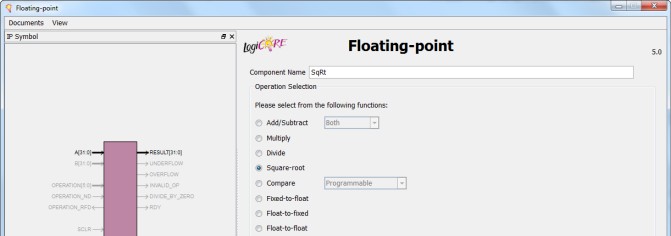

대화창에서, 실행할 부동소수 함수 (여기에서는 제곱근)를 선택합니다. 남은 단계를 클릭하여 다른 마법사 셋팅을 기본으로 남겨두고 Generate 버튼을 클릭합니다. IP 코어를 생성하는 데 몇 분이 소요될 수 있습니다.

그림 13: IP 코어를 생성합니다.

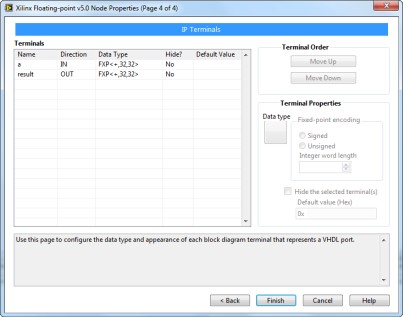

IP 생성이 완료되면 Xilinx Floating-point v5.0 Node Properties 윈도우의 다음 두 가지 프로퍼티는 기본 셋팅으로 남겨둡니다. 클럭 신호를 선택하고 리셋 동작을 설정하여 블록을 맞춤 설정할 수 있습니다. Finish를 클릭하여 생성 과정을 마칩니다.

그림 14: 생성 프로세스를 완료합니다.

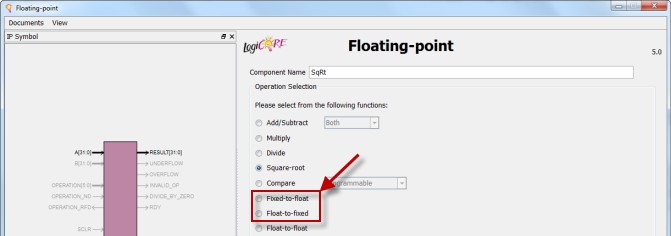

단계 2에서 단계 5까지 단계를 두 번 반복하여 두 개의 IP 블록을 더 생성합니다. 하나는 고정소수-부동소수 데이터 타입이고 다른 하나는 부동소수-고정 데이터 타입입니다. 그림 15와 같이 Floating-point Operator CORE Generator 설정 마법사의 첫 번째 단계에서 이 기능을 선택합니다.

그림 15: Floating-Point Operator CORE Generator 마법사

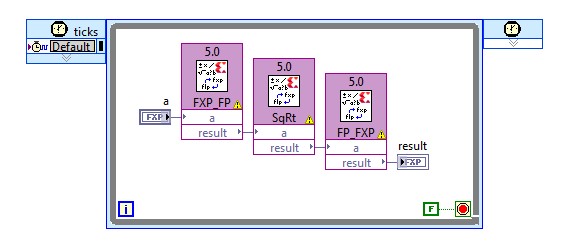

- 마지막으로, 그림 16과 같이 IP 블록을 연결하고 단일 주기 Timed 루프 내에 로직을 배치합니다.

그림 16: IP 블록을 연결하고 단일 주기 Timed 루프 내에 배치합니다.

이제 부동소수 제곱근 연산이 구현되었습니다. 이를 새로운 LabVIEW FPGA 어플리케이션 또는 기존 어플리케이션에 통합할 수 있습니다.

타사 IP를 가져오는 다른 방법

다른 VHDL 또는 Verilog IP를 얻거나 생성한 경우, Component-Level IP (CLIP) Node 또는 IP Integration Node를 사용하여 반입할 수 있습니다.

자세히 알아보려면 외부 IP를 LabVIEW FPGA에 반입하기를 참조하십시오.

FPGA를 위해 최적화된 고급 기능

더 많은 IP가 있으면 LabVIEW FPGA 어플리케이션을 더욱 효율적으로 완성할 수 있습니다. Xilinx CORE Generator IP 팔레트에서 사용 가능한 50개 이상의 IP 코어는 Xilinx FPGA에 최적화된 보다 고급 기능을 제공합니다. 포함된 설정 기반 마법사를 사용하면 특정 어플리케이션을 위한 IP 블록을 편리하게 구성하고 사용자 정의할 수 있습니다.