トリガを使用したデータ集録のテクニックとヒント - NI-DAQmx

概要

データ収集 (DAQ) プロセスを外部イベントに対して同期することは、多くのDAQアプリケーションで活用されています。たとえば、エンコーダからパルス信号を受信した後や、チャンバーの温度が臨界値を超えたときに、データ収集が必要になる場合があります。このような場合、DAQシステムでは、外部イベントやトリガが発生した直後に、アナログからデジタル (A/D) への)変換を開始するように設定する必要があります。

トリガ収集には2つの重要なメリットがありますトリガ収集ではトリガイベントに対する入力信号のタイミングが調整されるため、ユーザは必要な領域の信号のみを収集でき、これによりハードウェアの帯域幅とメモリを節約することもできます。

内容

トリガタイプ: アナログ vs. デジタル

NI-DAQmxはアナログトリガとデジタルトリガの両方をサポートします。ただしハードウェアによってはアナログトリガに対応していないデバイスもあります。

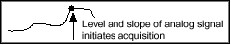

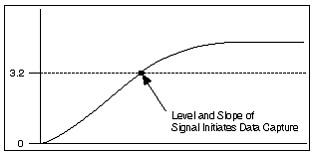

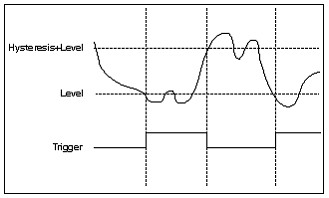

「アナログトリガ」 ― アナログ信号のレベルとスロープにより集録をトリガします(図1)。このシステムでは、DAQハードウェアのアナログトリガ回路(ATC)で連続的にアナログ信号を監視し、トリガ状態が条件に合っているかどうかを判断します。トリガ条件が合うと、ATCは集録を開始する内部トリガ信号を生成します。

図1: レベルとスロープのアナログトリガ条件

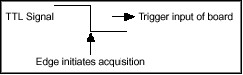

「デジタルトリガ」 ― TTL信号の立ち上がりまたは立ち下がりエッジでデータ集録を開始します(図2)。

図2: デジタルトリガ

集録タイプ: ポストトリガ vs. プレトリガ

トリガデータ集録アプリケーションはポストトリガとプレトリガの2つの方法で分類されます。

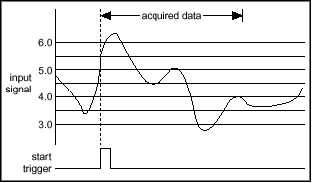

「ポストトリガ集録」 ― ポストトリガ集録では、トリガの受信後にハードウェアでA/D変換が開始されます(図3)。この場合のトリガ信号は開始トリガとも呼ばれます。

図3: ポストトリガ集録

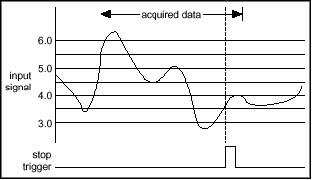

「プレトリガ集録」 ― プレトリガ集録では、トリガ信号の受信前にハードウェアでデータ集録が開始されます(図4)。このタイプの集録では、トリガイベント以前の信号を集録することができます。この場合、ハードウェアはソフトウェア関数でデータ集録を開始し、PCメモリの循環バッファにデータを格納します。バッファでは、必要なプレトリガサンプルが保存できるだけの容量を確保します。バッファが満杯になると、メモリにある一番古いサンプルに後続のサンプルが上書きされます。トリガのメカニズムの主機能は、集録を停止するとメモリに常駐しているサンプルに必要な「時間分割」を提供することです。この場合のトリガ信号は 基準トリガとも呼ばれます。

図4: プレトリガ集録

LabVIEWとDAQmxでトリガアプリケーションを開発する

このセクションでは、NI-DAQmxドライバを使用するトリガアプリケーションをLabVIEWで開発するガイドラインを説明します。別の方法として、テキストベースのプログラミング環境でトリガアプリケーションをプログラミングすることもできます。この場合は、NI-DAQmx APIの関数呼び出しを使用します。

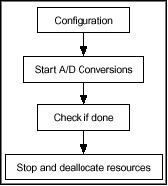

以下の通り、NI-DAQmxアプリケーションは、通常、4つの構成ブロックから成っています(図5)。

図5: 標準のDAQmxアプリケーションのフローチャート

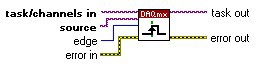

LabVIEWで適切なNI-DAQmx VIを呼び出して、アプリケーションのトリガ条件を構成します。以下に示すとおり「DAQmxデジタルトリガ」VIでデジタルトリガのタスクを構成できます。このVIでトリガソースとトリガにするエッジを指定します。さらに、DAQmxトリガプロパティノードでより複雑なトリガタスクを実装できます。

図6: 「DAQmxトリガ(DAQmx Trigger)」VI

このドキュメントの後半では、LabVIEWとNI-DAQmxの関数を使用してさまざまなトリガタイプの実装方法を説明します。

A. デジタル開始トリガでのポストトリガ集録

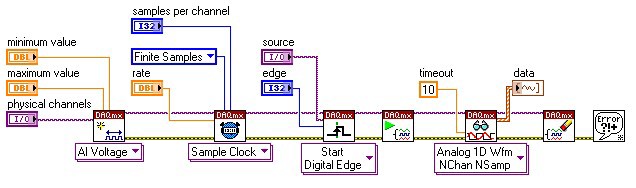

ポストトリガ集録では、DAQハードウェアがトリガ信号を受信した後にA/D変換を開始します。デジタルトリガは、通常、指定したデバイスのI/Oコネクタの外部トリガ入力に配線します。

以下のコードはNI-DAQmx関数を使用したポストトリガアプリケーションの設定方法を示します。

図7: デジタルトリガでのポストトリガ集録

このサンプルでは、アナログ入力タスクはデジタルトリガが発生するまで待機します。トリガエッジが「立ち上がり」に定義されている場合、アナログ入力タスクは指定したデジタルラインで立ち上がりエッジが発生した直後に開始します。

NI EシリーズおよびMシリーズ マルチファンクションI/Oデバイスでは、トリガ入力に複数のPFIラインの1つを選択できます。デフォルトのトリガソースはPFI0ですが、「DAQmxトリガ」VIのソースを設定するとトリガソース(例: 別のPFIラインまたはRTSIライン)を選択できます。

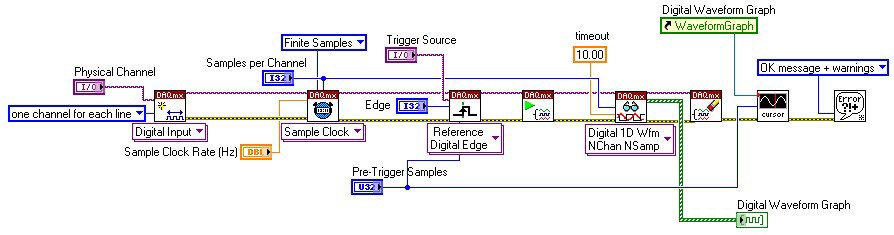

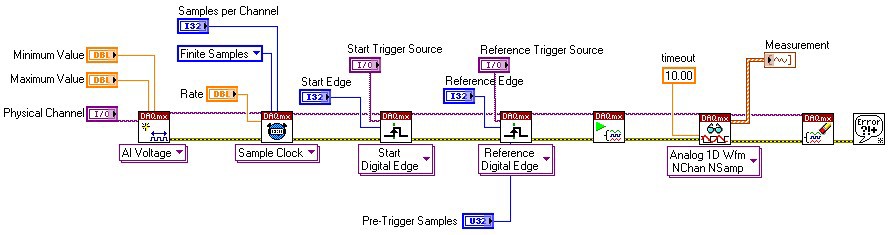

B. デジタル基準トリガでのプレトリガ集録

プレトリガ集録では、A/D変換がソフトウェア関数呼び出しで開始されます。NI-DAQmxは、バッファの最も古いポイントを新しいサンプルに置換し、循環バッファ構造でコンピュータメモリにデジタル化されたデータを格納します。トリガ信号が受信されると、トリガの前後に指定された数のポイントが、ドライバによりアプリケーション(例: LabVIEW、C++など)に返されます。

図8は、LabVIEWで「DAQmx基準トリガ」VIを使用し、必要なプレトリガサンプル数を指定する方法を示します。プレトリガサンプルをゼロに設定すると、ポストトリガ集録と同様の処理になります。

図8: デジタル基準トリガでのプレトリガ集録

C. 開始および基準トリガでのプレトリガ集録

開始トリガと基準(停止)トリガの両方を使用する集録も設定できます。この場合、ソフトウェア関数ではなくデジタルまたはアナログトリガ信号によって集録が開始されます。集録が開始されると、循環バッファ構造(前のケースと同様)は、基準トリガ信号が受信されるまで実装されます。返されるデータは、基準トリガ信号に関連するプレトリガとポストトリガの指定されたサンプル数で指定します。

開始

図9: デジタル開始トリガおよびデジタル基準トリガでの集録

D. アナログハードウェアトリガ

アナログエッジトリガでは、特定の信号レベルとスロープ(立ち上がりまたは立ち下がり)を検索する測定デバイスを構成します。デバイスは、トリガ条件を識別し、そのトリガが発生すると関連付けられた動作(測定開始や集録サンプルのマーク付け)を実行します。アナログトリガ信号は、アナログ信号の受信が可能なアナログ入力チャンネルまたは端子に接続します。

例えば、以下の図のように立ち上がりエッジ信号で信号が3.2に到達するとトリガとなり、データがキャプチャされるよう設定することができます。

アナログ

例えば、

図10: アナログエッジトリガ

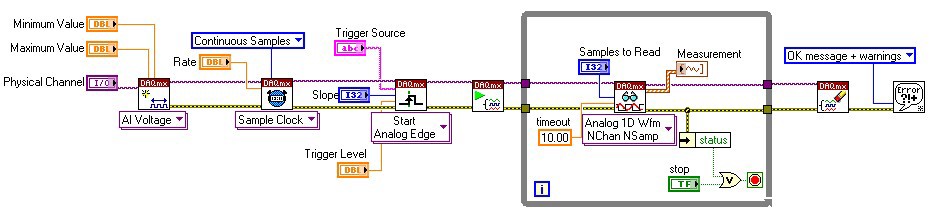

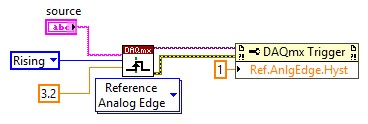

図11は、LabVIEWで「DAQmxアナログトリガ」VIを使用してアナログハードウェアトリガを実装する方法を示します。

図11: LabVIEWでのアナログ開始トリガ

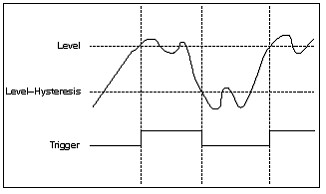

E. ヒステリシスでのアナログトリガ

アナログトリガの状態としてヒステリシスも指定できます。ヒステリシスは、信号のノイズまたはジッタによって発生する不正なトリガを低減するために、トリガレベルの上下に追加するウィンドウです。立ち上がりスロープでヒステリシスを使用すると、トリガは信号がレベル(またはしきい値レベル)からヒステリシスを引いた値より下で開始され、その後レベルより上回った場合にアサートします。また、信号がレベルからヒステリシスを引いた値よりも下回るとアサート解除します。

たとえば、上記のレベルが3.2である例にヒステリシス1を追加する場合、トリガは信号が2.2以下で開始されなければ発生しません。その後、トリガは信号が3.2を越えるとアサートし、2.2より下がるとアサート解除します。

図12: 立ち上がりスロープでのヒステリシス

立ち下がりスロープでヒステリシスを使用すると、トリガは信号がレベル(またはしきい値レベル)からヒステリシスを足した値より上で開始され、その後レベルより下回った場合にアサートします。トリガは、信号がレベルからヒステリシスを足した値よりも上回るとアサート解除します。代わりに、立ち下がりエッジで3.2にヒステリシス1を適用した場合、信号が4.2以上で開始されなければトリガが発生しません。その後、トリガは信号が3.2より下回るとアサートし、4.2を越えるとアサート解除します。

図13: 立ち下がりスロープでのヒステリシス

ヒステリシスは、LabVIEWではトリガプロパティノードを使用して指定します。以下の図は、1のヒステリシスでアナログトリガを作成するコードの一部を示します。

図14: レベル = 3.2、スロープ = 立ち上がり、 ヒステリシス = 1.0を設定する場合