VST(NI PXIe-5644R)のハードウェアアーキテクチャ

概要

内容

高い性能、画期的な設計

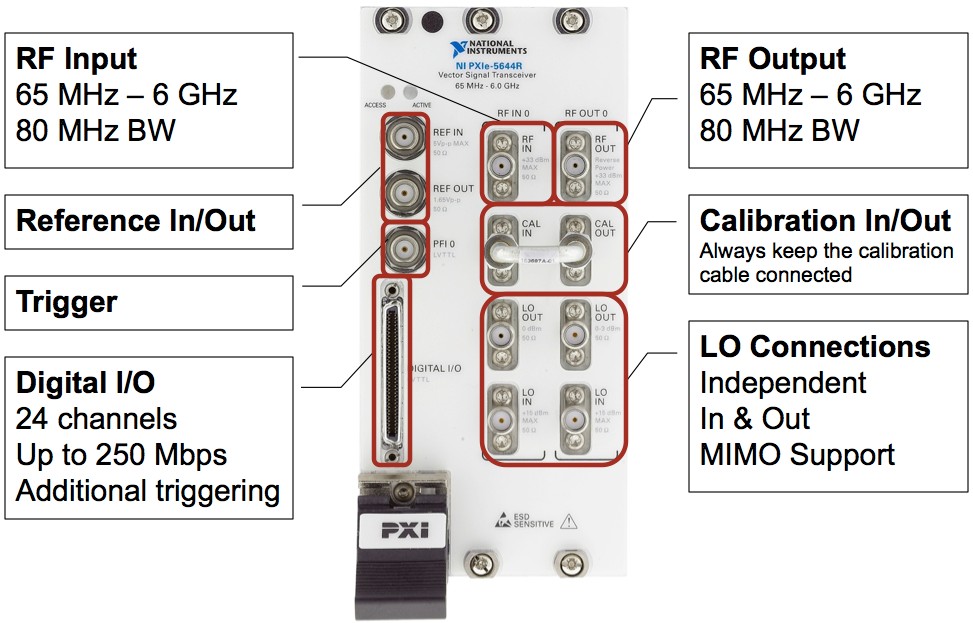

NI PXIe-5644Rは、ベクトル信号トランシーバ(VST:Vector Signal Transceiver)という新たなカテゴリの製品です。VSTは、一般的なベクトル信号アナライザ(VSA:Vector Signal Analyzer)とベクトル信号発生器(VSG:Vector Signal Generator)が備えるRF入出力機能と、内蔵FPGAで実現する信号処理機能/制御機能を併せ持つものです。そのFPGAに実装される機能は、NIとユーザーのどちらが定義することも可能です。RF入力(RF IN)とRF出力(RF OUT)はそれぞれローカルオシレータ(LO)を備えており、65 MHzから6 GHzまでの周波数範囲と最大80 MHzの瞬時帯域幅に対応します。NI PXIe-5644Rは、3スロットのPXI Expressモジュールです(図1)。1台のPXI Expressシャーシに複数台のVSTを接続すれば、MIMO(Multiple Input Multiple Output)のコンフィギュレーション(構成)が可能になります。

図1. NI PXIe-5644Rのフロントパネル

NI PXIe-5644Rの魅力とは何なのでしょうか。それは、このような小さなフットプリントで高い性能を発揮できることです。NI PXIe-5644Rは高度なキャリブレーション(校正)と広帯域に及ぶデジタル補正を駆使することにより、極めて小さなフォームファクタであるにもかかわらず、R&Dグレードの計測器に期待されるのと同等の性能を実現します。このような特徴に加え、ユーザによるプログラミングが可能なFPGAによって実現される高速性能と柔軟性という特徴も併せ持ちます。これらの特徴を組み合わせることで、NI PXIe-5644Rは、RFコンポーネントの特性評価や、検証、検査、製造テストに使用する装置として最適なものとなりました。

上述したような高い性能と小さなフットプリントがNI PXIe-5644Rの特徴としては印象的であるかもしれません。しかし、この製品の最も画期的な機能としては、ユーザによるプログラミングが可能なFPGAを搭載し、LabVIEW FPGAモジュールを使ってプログラミングが行えるという点が挙げられます。NI PXIe-5644Rが搭載するFPGAは、Xilinx社のVirtex-6です。このFPGAを使えば、最大250 Mbit/秒のデータレートで、VSAとVSGのI/Qベースバンドデータや24本のデジタルI/O信号線にアクセスすることが可能です。このように、NI PXIe-5644Rでは、RF技術、高速デジタルI/O技術、FPGA技術を強力に組み合わせています。そのため、テストの対象とするデバイスのリアルタイム制御や、カスタムトリガリング、電力レベルサーボ、ソフトウェア無線(SDR:Software Defined Radio)、チャネルエミュレーションといった広範なアプリケーションで使用することができます。

FPGAベースカードのアーキテクチャ

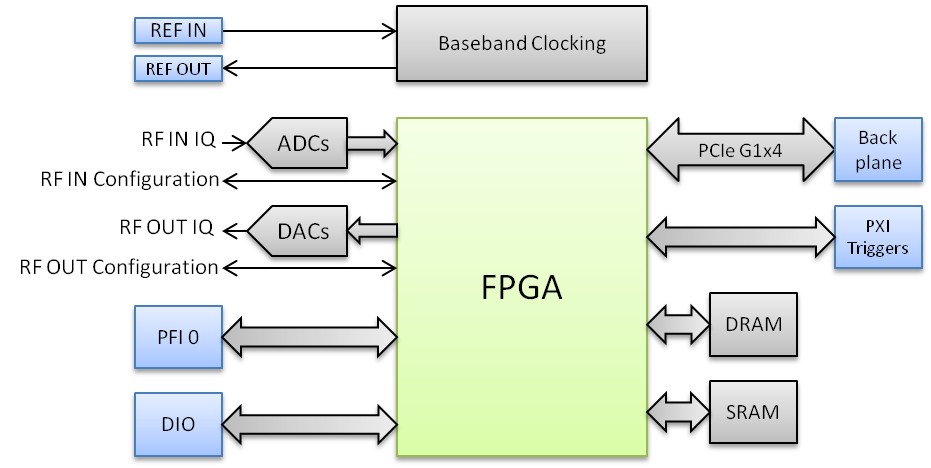

NI PXIe-5644RのFPGAベースカード(basecard)は、FPGA(Xilinx社のVirtex-6)、ベースバンドクロック回路、A/Dコンバータ(以下、ADC)、D/Aコンバータ(以下、DAC)、PFI 0(プログラマブルファンクションデジタルI/Oライン)、DIO(デジタルI/Oコネクタ)、PCI Expressインタフェース、PXIトリガ回路、DRAM、SRAMで構成されています。

図2. FPGAベースカードのブロック図

Xilinx社のVirtex-6

NI PXIe-5644Rが搭載しているFPGAは、Xilinx社のVirtex-6 LX195Tです。このFPGAは、システムのコンフィギュレーションや、デジタルデータの転送、デジタル信号処理に利用されます。また、このFPGAからは、ADCやDAC、PCI Expressバス、DRAM、SRAM、PFI 0、DIO、PXIトリガ回路に直接アクセスすることができます。そのため、FPGAをプログラミングすることにより、さまざまなアプリケーションの要求を満たすようカスタム対応を図ることが可能です。

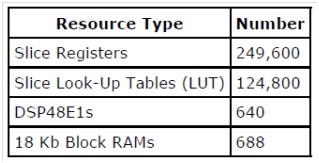

再構成可能なFPGAリソース

表1に、Virtex-6 LX195Tのリソースについてまとめておきます。

表1. Virtex-6 LX195Tのリソース

LabVIEW FPGAモジュールでプログラミングが可能

NI PXIe-5644Rが搭載しているFPGAは、LabVIEW FPGAモジュールを使ってプログラミングすることができます。LabVIEWでは、処理の並列性とデータフローがわかりやすく表示されるので、FPGAのプログラミングに非常に適しています。従来の手法を用いてFPGAを設計した経験を持つユーザも、未経験のユーザも、FPGAという再構成可能なハードウェアの特質を生産的に活用することが可能です。

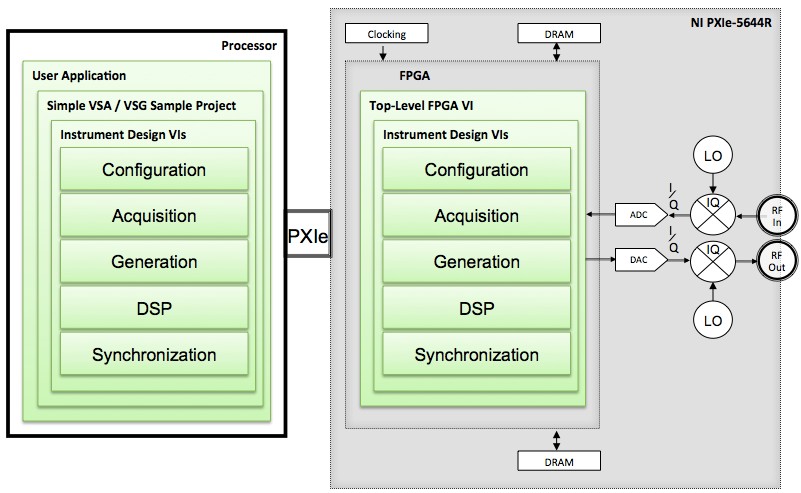

NIは、ユーザが製品を購入した後、最初の計測を即座に実行できるよう、NI PXIe-5644R用のLabVIEWサンプルプロジェクトとInstrument Design VIを用意しました。このVIを使用すれば、FPGAとプロセッサのそれぞれで使用するLabVIEWコードにもアクセスすることができ、そのコードに対する修正を行うことが可能です。Instrument Design VIは、コンフィギュレーションや、集録、生成、デジタル信号処理(DSP)、同期などの機能別に分類されています(図3)。NI PXIe-5644Rに対応するソフトウェアについて、詳しくはVSTのソフトウェアアーキテクチャに関する技術ドキュメント、もしくはVSTに関するウェブイベントをご覧ください。

図3. NI PXIe-5644RにマッピングされているLabVIEWサンプルプロジェクトとInstrument Design VI

ベースバンドクロック

NI PXIe-5644Rが内蔵するFPGAは、内部に複数のクロックを備えています。メインのクロックはサンプリングクロックで、ADC、DAC、および両コンバータに関連するFPGA上のロジック回路のクロックとして使用します。

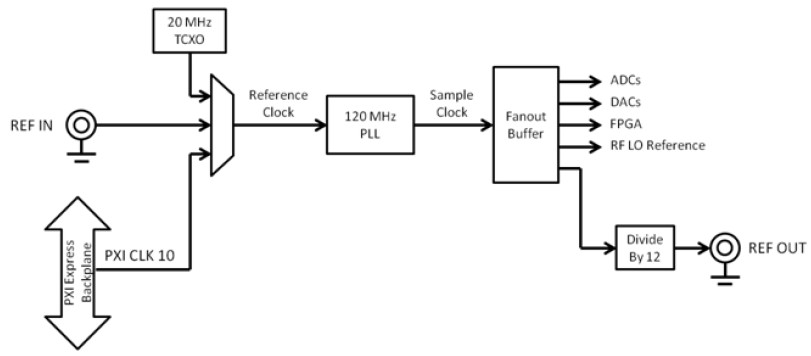

サンプリングクロック

サンプリングクロックの周波数は120 MHzで、PLL(位相同期回路)を介して分配されます。PLLで使用する基準クロックとしては、NI PXIe-5644Rが内蔵するTCXO、NI PXIe-5644RのフロントパネルにあるREF INコネクタへの入力、PXI_CLK 10信号のうちいずれかを選択できます。このサンプリングクロックは、RF INとRF OUTが内蔵するLO回路のリファレンスクロックとなります(図4)。サンプリングクロックの周波数は120 MHzに固定されていますが、FPGA内部のFractional Interpolation(分数補間) VIとFractional Decimation(分数間引き) VIの両DSP VIを使えば、より分解能の高いI/Qデータレートを実現できます。

図4. NI PXIe-5644Rが備えるクロック回路のアーキテクチャ

FPGA用のクロック

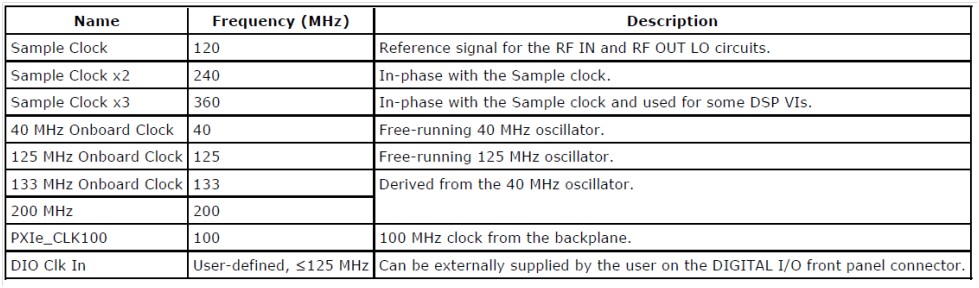

表2は、FPGAで使用するクロックの一覧です。これらのクロックに加え、LabVIEW FPGA環境では、ユーザが定義した周波数のクロックも利用できます。

表2. FPGAで使用するクロックの一覧

ADCとDAC

NI PXIe-5644Rでは、デュアルチャンネルの16ビットADCとDACを使用することができます。これらのADCとDACは120 MS/秒のクロックを用いて80 MHzの複合帯域幅を提供します。また、FPGA内部のサンプリングクロックのドメインと自動的に同期がとられます。そのため、同一クロックドメイン内にあるADCとDACの両方とインタフェースを得て、完全な同期を実現することができます。加えて、受信側と送信側の間で遅延時間を確定的なものとすることが可能です。さらに、RF INとRF OUTは、FPGAの同一クロックドメインでI/Qデータをストリーミングします。そのため、リアルタイムでのテストや組込アプリケーションにおける同期を実現でき、さらに遅延時間を確定的なものとすることが可能なことから、プログラミングが容易になります。

PFI 0

PFI 0は、3.3 VのLVTTL(Low Voltage TTL)に対応した双方向の汎用デジタルI/O信号です。最も一般的な用途としては、トリガ入力やマーカ/イベント出力が挙げられます。またPFI 0のI/OバッファはFPGAに直接接続されているので、LabVIEW FPGA環境を使用することによって、カスタムアプリケーション向けに機能をプログラミングすることも可能です。

デジタルI/O

NI PXIe-5644RのデジタルI/Oには、VHCDI(Very High Density Cable Interconnect)ポートを介してアクセスすることができます。LVTTL対応の双方向デジタルI/Oラインが1ポート当たり4本あり、ポート数が計6ポートなので計24本用意されています。このI/Oラインは、ポートごとに構成することが可能です。デジタルI/Oのコネクタには、クロック入力(Clock In)ライン、クロック出力(Clock Out)ライン、トリガ、追加の双方向デジタルI/Oとして使用可能なPFI 1/PFI 2ラインも含まれています。デジタルI/OバッファはFPGAに直接接続されているので、LabVIEW FPGAモジュールを使用すれば、カスタムアプリケーション向けに個々のデジタルI/O信号に対応する機能をプログラミングすることができます。

ケーブルとアクセサリ

NIは、デジタルI/Oコネクタと接続可能なケーブルやアクセサリを何種類も用意しています。それらは、NI PXIe-5644RのデジタルI/Oに適合するカスタムのピン配列を採用しており、インピーダンスが50Ωの伝送線環境を提供します。なお、他社製のVHDCIケーブルの使用はお勧めしません。

DRAMとSRAM

NI PXIe-5644Rは、容量が1バンク当たり256 MBのDRAMを2バンク搭載しています。理論上の最高データレートはバンク当たり2.1 GB/秒で、FPGAから各バンクにアクセスすることができます。このDRAMバンクは汎用のものですが、通常、生成する波形データ、または集録した波形データを格納する目的で使用されます。

また、読み出しデータレートが最高40 MB/秒、書き込みデータレートが同36 MB/秒のオンボードSRAMも搭載しています。このSRAMの容量は2 MBで、FPGAを介したデータストリーミング(I/Q信号をデジタルデータに変換する場合など)に最適です。

PCI Expressインタフェース

NI PXIe-5644Rは、バックプレーンと接続されたPCI Express Gen 1×4を備えています。これらはDMA(Direct Memory Access)転送やピアツーピアストリーミング、PIO(Programmed I/O)に使用します。

レシーバのアーキテクチャ

NI PXIe-5644Rは、RFレシーバとしてホモダインレシーバを搭載しています。ホモダイン方式は、シンクロダイン、ゼロIF、ダイレクトコンバージョンの名でも呼ばれているものです。このホモダインレシーバにおいて、RF入力信号は、NI PXIe-5665やNI PXIe-5663EなどのVSAが搭載する従来型のヘテロダインレシーバと同様に、周波数ミキサーに送信されます。ヘテロダインレシーバとの違いは、ホモダインレシーバでは、LOの周波数がRF入力信号の周波数と同一もしくは非常に近い値であることです。すなわち、10 MHzまたは20 MHzのDC中心の信号、もしくは低周波のIF信号が使われます。

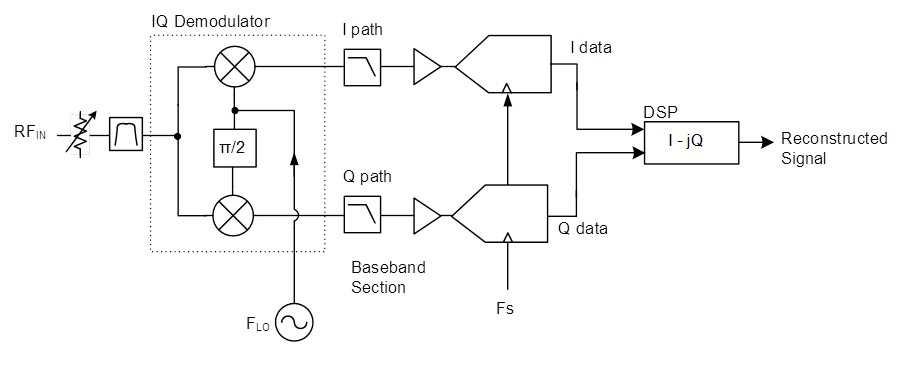

入力信号はベースバンド信号へとミックスダウンされ、I(同相)成分とQ(直交位相)成分に分けられます。まず90°の位相シフトを施して、Iパス信号とQパス信号を得ます。その後、Iパス信号とQパス信号は個別にデジタル化され、IデータとQデータになります。最後に、IデータとQデータのストリームはソフトウェアで結合され、元の信号が復元されます。図5は、ホモダイン方式のレシーバのアーキテクチャを簡略化して示したものです。

図5. ホモダインレシーバの基本アーキテクチャ

ホモダインレシーバのメリット

ホモダイン方式のアーキテクチャには、従来型のヘテロダイン方式を上回るメリットが多数あります。例えば、設計の簡素化や、コスト/消費電力の削減、選択度の向上(隣接チャネルの重複する信号との分離)が図れるといったことです。そのほかに、潜在的な帯域幅の向上や、LOの単一化による設計の簡素化、設計の小型化によるフットプリントの削減なども利点として挙げられます。これらのメリットについてまとめると、以下のようになります。

ホモダインレシーバの課題

上述したとおり、ホモダイン方式のアーキテクチャには多数のメリットがあります。その一方で、包絡線検波が行えないなど、さまざまな課題も存在します。NI PXIe-5644Rでは、直交検波とデジタル信号処理を用いて、そうした問題を克服しています。

ホモダイン方式のアーキテクチャのもう1つの課題はDCオフセットです。ホモダイン方式のゼロIF構造では、あらゆる信号が0 Hzにミックスダウンされます。そのため、DCにスペクトル成分が生じます。この歪みは、データ集録における瞬時帯域幅の中心で降下します。複数のデータ集録に対応するスペクトルを重ね合わせて見た場合、それぞれのスペクトルの中心には周波数オフセットの影響が生じている状態となります。DCオフセットをゼロにするには、デジタル化されたI/Qデータストリームに対してそのオフセットを相殺するようなオフセットを加えます。各LOの周波数信号に対してもオフセットをゼロにするための処理を適用する必要がありますが、これについてはNI PXIe-5644Rのセルフキャリブレーションを実行すれば自動的に完了します。

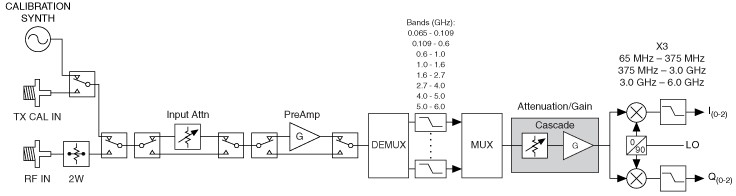

レシーバの信号パス

図6は、NI PXIe-5644Rが備えるレシーバのアーキテクチャを示したものです。この図では、キャリブレーション用のシンセサイザと、出力の大きい信号に対して用いるオプションのアッテネータ、出力の小さい信号に対して用いるオプションのアンプ、阻止帯域を選択可能なフィルタ(フィルタバンク)、増幅/減衰が可能な追加の信号調節回路、周波数に応じて3つのミキサのうち1つを適用する復調回路を示しています。

図6. NI PXIe-5644Rが備えるレシーバのアーキテクチャ

フィルタバンクには、ローパスフィルタやバンドパスフィルタを備える8つの異なるパスがあります。これらのフィルタを用いれば、不要なノイズをほとんど除去することが可能です。そのため、レシーバ全体としては対象とする信号範囲のみに焦点を絞ることができます。このフィルタバンクとその後段にある信号調節回路を通過した後、RF信号は周波数に応じて、3系統の復調器のうちのいずれかによって処理されます。各復調器は特定の周波数帯で動作し、ゲインと位相を最適化します。

レシーバのパスには、1 dBステップで80 dB以上の減衰に対応するアッテネータが複数個組み込まれています。RF入力はAC結合されています。また、切り替え可能なゲインアンプ3個とプリアンプ1個によってダイナミックレンジを拡張し、雑音指数の向上を図ります。

レシーバは、位相ノイズの低いLOを内蔵しています。複数台のダウンコンバータは、この1つのLOを共通のソースとします。MIMOシステムなど、位相同期が必要な信号集録アプリケーションでは、単一のLOをソースとして使用する構成が有利です。1つのLOを共有するNI PXIe-5644Rでは、RFチャンネルはすべて同一のRF周波数に同調されます。

ダウンコンバートされたベースバンド信号は、NI PXIe-5644Rが内蔵するADCのチャネルに直接送信されます。ADCのチャネルは、ベースバンド帯のアナログ信号を16ビットのダイナミックレンジ、120 MS/秒のサンプリングレートでデジタル化します。その結果はオンボードのFPGAに送信され、追加の処理が行われます。その後、データはホストに転送されます。

ダウンコンバータ

NI PXIe-5644Rのレシーバは、1ステージのダイレクトコンバージョン方式(I/Q)ダウンコンバータを備えています。RF信号は、LO周波数(構成済み)からDCにダウンコンバートされ、その結果得られたベースバンド信号はデジタル化されて処理されます。このアーキテクチャは、瞬時帯域幅を拡大することで、イメージ成分の抑圧を図り、LOリークを最小限に抑えます。イメージとLOリークの抑制による性能の向上は、広帯域の直交歪み補正によって実現します。レシーバのパスは、広帯域の復調用VSAとしての用途に向けて最適化されています。

低IFモードと帯域内再調整

I/Q復調器を用いた別のタイプのレシーバとして、低IFレシーバが挙げられます。低IFレシーバの構成は、図5に示したホモダインレシーバ(ゼロIFレシーバ)の構成と同じです。LO周波数が変調信号の周波数範囲内にあるゼロIFレシーバとは異なり、低IFレシーバでは、LO周波数は変調信号の周波数範囲外となります。そのため、ダウンコンバートの際にDC成分が発生することはありません。DCオフセットの問題だけでなく、1/fノイズ、場合によってはベースバンド高調波といった、DC中心であることに関連する障害の大半が解消されます。

LO調整やデジタル周波数シフトといった機能を組み合わせれば、NI PXIe-5644Rを低IFモードで動作させることができます。搬送波からデジタル的にシフトした周波数を使用して、対象とする信号を集録したり、生成したりすることにより、ダイレクトコンバージョンのトポロジで発生するLOリークの影響を避けることができます。ただし、最大帯域幅(BW)についてのトレードオフが発生します。ADCのサンプリングレートが同一であると仮定した場合、低IFレシーバの最大帯域幅はゼロIFレシーバの最大帯域幅の半分になります。NI PXIe-5644Rは、デジタル周波数修正用に追加で割り当てられた4 MHzの複合帯域幅と合わせて、最大80 MHzの複合瞬時帯域幅をサポートします。追加の周波数シフトによって、使用可能な80 MHzの帯域幅は(80/2)-(X-2) MHz(Xは要求されるデジタル周波数シフト)まで減少します。

トランスミッタのアーキテクチャ

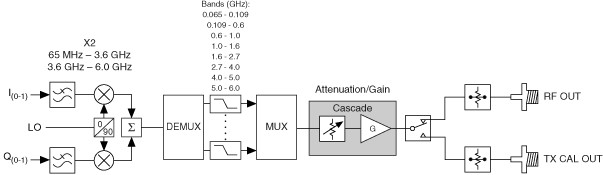

NI PXIe-5644Rが備えるRFトランスミッタのアーキテクチャは、2系統の変調器、フィルタバンク、追加の信号調整回路から成ります(図7)。

図7. NI PXIe-5644Rが備えるトランスミッタのアーキテクチャ

トランスミッタの信号パス

NI PXIe-5644Rが搭載する2系統の変調器は、VSG製品であるNI PXIe-5673Eで使用されているのと同じものです。この変調器は、周波数に応じて位相とゲインのバランスを維持するように最適化されています。また、RFトランスミッタが備えるフィルタバンクはRFレシーバで使用されているのと同じものです。図7に示したとおり、RFレシーバと同様、ローパスフィルタとバンドパスフィルタを備えた8つのパスがあります。

RF信号は、フィルタを通過した後、カスケード型の信号調節ステージに入ります。このステージは、3個のプログラマブルアッテネータと、選択可能な1個のアンプ、固定的に使用する2個のアンプで構成されます。RF信号は、最終的にトランスミッタのパスがキャリブレーション済みか否かによって、RF OUTまたはCAL OUTのいずれかのフロントパネルコネクタに出力されます。

アップコンバータ

RFトランスミッタのパスは、1ステージのダイレクトコンバージョン方式(I/Q)アップコンバータを備えています。ベースバンド信号はこのアップコンバータによって、DCからLO周波数(構成済み)のRF信号へとアップコンバートされます。このアーキテクチャでは、瞬時帯域幅を拡大することで、イメージの抑圧を図り、LOリークを最小限に抑えます。イメージとLOリークの抑制による性能の向上は、広帯域の直交歪み補正によって実現します。このパスは、CW(Continuous-Wave)発生器または広帯域の変調用VSGとしての用途に向けて最適化されています。

トランスミッタのパスには、1 dBステップで100 dB以上の減衰に対応するアッテネータが4個含まれています。また、大きい出力の信号を生成する際には、切り替え可能な追加のゲインアンプ1個を使用します。

トランスミッタは、位相ノイズの低いLOを内蔵しています。複数台のアップコンバータは、この1つのLOを共通のソースとします。MIMOシステムなど、位相同期が必要な信号生成アプリケーションでは、単一のLOをソースとして使用する構成が有利です。1つのLOを共有するNI PXIe-5644Rでは、RFチャンネルはすべて同一のRF周波数に同調されます。

平均実効出力と波高因子を考慮

波高因子は、平均実効出力(RMS値)に対する信号のピーク値の比率を表す値です。CWモードにおける正弦波信号の波高因子は3 dBです。言い換えれば、正弦波の平均実効出力はピーク値よりも3 dB低いということです。変調信号、特にOFDM(Orthogonal Frequency Division Multiplexing:直交周波数分割多重化)方式を用いた変調信号の場合、波高因子は約10 dBから12 dBと非常に大きくなります。

信号生成用に装置を構成する際には、平均実効出力と信号の波高因子の両方について考慮することが重要です。NI PXIe-5644Rの最大平均実効出力は6 dBmで、最大12 dBの波高因子に対応します。平均実効出力が6 dBmを超えると、装置はキャリブレーション済みで、線形性を維持している状態にあるとは言えなくなります。さらに重要なのは、平均実効電力が6 dBmを上回るように設定され、信号の波高因子が12 dB以上で保持されると、極度の飽和が発生したり、NI PXIe-5644Rの逆電力保護回路が起動したりする恐れがあるということです。

シンセサイザLOのアーキテクチャ

NI PXIe-5644Rは、1 Hz以下の調整分解能を有し、65 MHz~6 GHzの周波数範囲に対応します。調整分解能は、LOのステップサイズ機能と、FPGA上に実装される周波数シフト処理を組み合わせることで実現しています。

LOのステッピングモードは2種類あります。

NI PXIe-5644RのシンセサイザLOでは、120 MHzのクロックを基にするPLLを用います。VCO(電圧制御発振器)としては、対応周波数が2 GHz~2.5 GHz/2.5 GHz~3 GHz/3 GHz~4 GHzと異なる3個が用意されています。要求される出力信号が4 GHz未満の場合、信号は分周器へ送られます。同様に、要求される出力信号が4 GHz~6 GHzの場合、信号は逓倍器(2倍の乗算器)へ送られます。このステージの後段にはフィルタバンク(送信信号パスとは別のもの)があり、必要に応じて高調波を除去する処理が行われます(図8)。

複数のゲインを適用後の信号は、内蔵オシレータと外付けオシレータの切り替えスイッチに送られます。後者は、位相同期が求められるMIMOアプリケーションに適しています。MIMO向けの構成において性能を向上させる方法としては、キャリブレーション用のADCを利用してLOパスを校正するという選択肢もあります。図8に示すように、LO信号は、NI PXIe-5644RのRFレシーバとRFトランスミッタの両方に使用されているのと同じ、ローパスフィルタとバンドパスフィルタを伴うフィルタバンクに入力されます。

図8. NI PXIe-5644Rが備えるシンセサイザLOのアーキテクチャ

スペクトル純度

RF入力信号は、LO信号と混合される際に、LOのスペクトル成分を受け継ぎます。このことは、LOのスペクトル純度の高さが非常に重要であるということを意味します。多くの場合、対応周波数帯域ごとに分けてラインアップされているVSA製品には、市販の統合型シンセサイザが組み込まれいます。その種のシンセサイザは、ディスクリート構成の従来型シンセサイザと比べると性能が劣ります。NI PXIe-5644Rは、広帯域対応の計測器として設計されており、ディスクリート構成で一から構築した従来型のシンセサイザを搭載しています。そのため、対応する周波数範囲全体において優れた計測性能を発揮することができます。

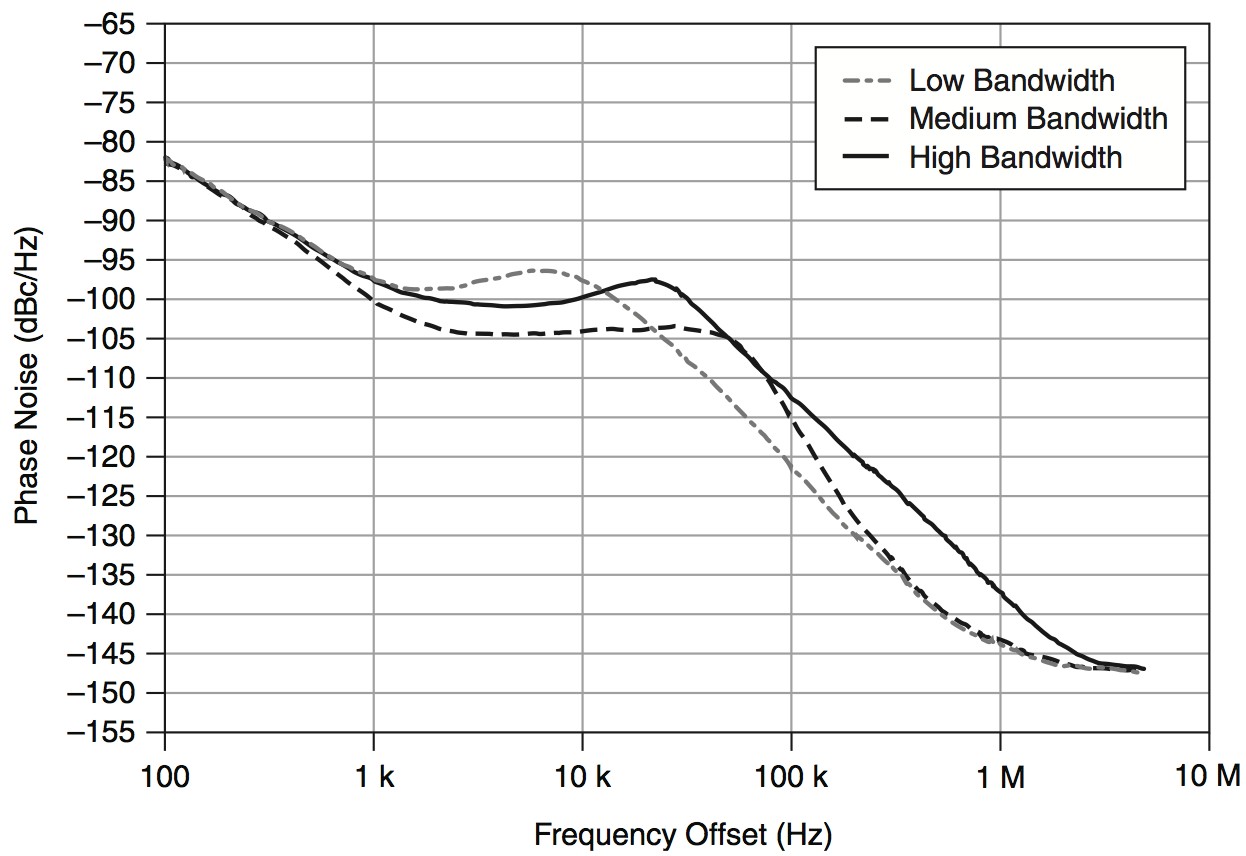

上記のとおり、これらのオプションでは、位相ノイズと整定時間の間にトレードオフの関係があります。

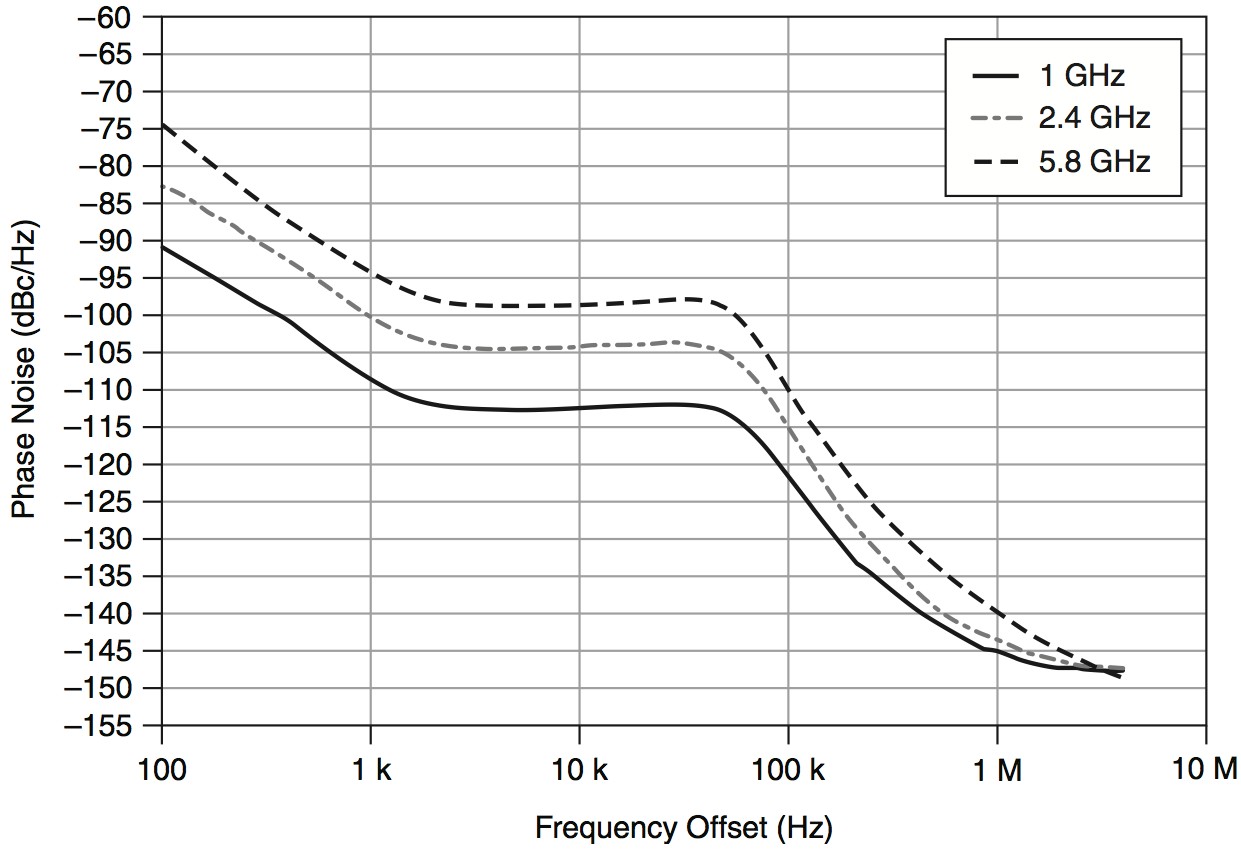

IEEE 802.11acやLTE(Long Term Evolution)などのRF規格に対応した計測には中帯域幅オプションをお勧めします。整定速度が重視されない用途では、低帯域幅オプションを選択するとよいでしょう。高帯域幅オプションの選択が推奨される事例としては、高速周波数ホッピングを利用する用途が挙げられます。図9のグラフは、PLLの各帯域幅オプションごとに位相ノイズがどのように変化するのかを示したものです。一方、図10は中帯域幅オプションを選択した場合に、周波数の変化と位相ノイズがどのような関係になるのかを表したグラフです。

図9. ループ帯域幅と位相ノイズの関係(2.4 GHzで計測)

図10. PLLの中帯域幅オプションを使用した場合の位相ノイズ(1 GHz、2.4 GHz、5.8 GHzで計測)

キャリブレーション

NI PXIe-5644Rでは、正確な周波数と振幅応答を実現するために、工場で1台1台に対して校正(キャリブレーション)が行われます。出荷時には、NIST(米国立標準技術研究所)トレーサビリティに準拠していることを示すキャリブレーション保証書が1台1台に添付されます。外部工場キャリブレーションでは、周波数基準、内蔵LOのパスゲイン、外部LOのパスゲイン、RF入力ゲイン、RF出力ゲインの調整を行います。NIは、NI PXIe-5644Rの仕様を継続的に満足するために、1年に1回(仕様を緩和する場合は2年に1回)の頻度で工場でのキャリブレーションを行うことを推奨しています。

キャリブレーションパス

NI PXIe-5644Rのキャリブレーションでは、キャリブレーションセクションにおけるRF入力とRF出力との間の固定パスが最も重要になります。CAL INとCAL OUTの両フロントパネルコネクタ間をSMA-SMA半剛体ケーブルで接続することが、キャリブレーションを円滑に進めるうえで重要です。このケーブルを緩めたり、デバイスのフロントパネルから外したりすると、セルフキャリブレーション機能が適切に働かなくなります。

セルフキャリブレーション

環境温度が5℃以上変化した場合には、必ずセルフキャリブレーションを実施してください。NI PXIe-5644Rでは、温度ドリフトによって、複数の仕様項目で性能が低下する恐れがあります。セルフキャリブレーションを行うことにより、周囲温度に対して性能を補償し、最適化することができます。NI PXIe-5644Rのセルフキャリブレーションでは、以下のパラメータが調整され、温度補正が行われます。

- LOパスのゲイン

- RF入力のゲイン

- RF出力のゲイン

- RF入力におけるLOリーク

- RF出力におけるLOリーク

- RF入力におけるイメージ抑圧

- RF出力におけるイメージ抑圧

キャリブレーションを実施済みのシンセサイザと、安定した振幅を提供する低歪みアンプを組み合わせることで、周波数の安定化を図ることができます。キャリブレーションテーブルは、周波数と出力の両方を一括処理できるようなものとなっています。また、周波数に対するベクトルキャリブレーションの実施も可能です。こうした高度なキャリブレーション技術は、NI PXIe-5644Rが、非常に小さなフォームファクタでR&Dグレードの性能を達成している理由の1つとなっています。