Xilinx CORE Generator IPパレットでIPコアの再利用を促進

概要

ソフトウェア開発の生産性を向上させるには、コードを効率的に再利用することが重要です。FPGA (プログラム可能なゲートアレイ) ハードウェアでは、再利用可能なコードブロックを一般的にIPブロックと呼びます。NI LabVIEW FPGAモジュールには、製品内のIPブロックにアクセスする方法が多数用意されています。LabVIEW FPGAモジュールには演算や信号処理のための標準関数が数多く組み込まれていますが、他のソースからの既製のIPライブラリを使用する方法が一般的です。 LabVIEW 2011 FPGAモジュールおよびそれ以降のバージョンには、Xilinx社が開発し、Xilinx FPGAハードウェア用に微調整された一連の高性能ライブラリが付属しています。FPGAの設計プロジェクトの生産性を高めるために、Xilinx CORE Generator IPパレットの機能とその使用方法を習得しましょう。

内容

- Xilinx CORE Generatorパレットの概要

- Xilinx CORE Generator IPブロックのライセンス

- CORE Generator IPを使用した開発に関する注意事項

- CORE Generator IPブロックをLabVIEWに組込む

- 他社製IPを別の方法でインポートする

- FPGA用に最適化された高度な機能

- 次のステップ

Xilinx CORE Generatorパレットの概要

基本関数

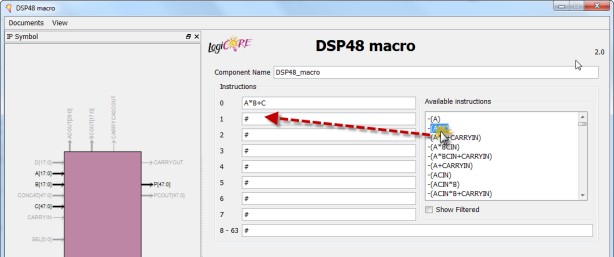

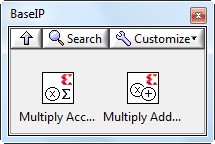

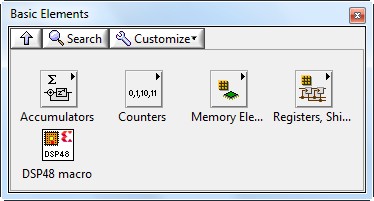

基本IPパレットには、高度に最適化されたアキュムレータ、カウンタ、メモリジェネレータの各関数が用意されています。構成ウィザードでは、DSP48 Macro関数を使用して、カスタマイズされたIPを生成することもできます。このマクロウィザードでは、命令、パイプライン構成、およびポートを指定することで、DSP48を順を追ってカスタマイズできるため、複雑な設定を手動で構成しなくても、DSP48の性能を活用することが可能です。

図1: DSP48 Macro関数を使用すると、LabVIEW FPGA用カスタムIPブロックをすばやく構成し、生成することができます。

| IP製品ページ | |

図2: BaseIP LabVIEW FPGAパレット |

|

図3: Basic Element LabVIEW FPGAパレット |

デジタル信号処理 (DSP)

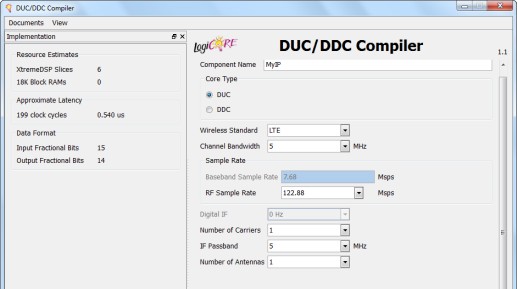

DSP CORE Generatorパレットには、信号処理アプリケーションの開発時間を短縮するためのフィルタと変換のライブラリが用意されています。CORE Generatorウィザードは構成ベースですが、リソース使用量の予測や、現在のポートの利用率をわかりやすく表示するためのIPシンボルなど、さまざまなパラメータが公開されます。このように高度にパラメータ化されたアプローチによって、柔軟かつ効率的にカスタマイズされたIPを生成することができます。

図4: Xilinx社のCORE Generatorのダイアログ画面。IPのさまざまなパラメータや仕様が表示され、特定のアプリケーションのニーズに合わせてIPコアをカスタマイズできます。

図5: デジタル信号処理パレット | IP製品ページ |

Coordinate Rotational Digital Computer (CORDIC) Cascaded Integrator-Comb Compiler |

1このCORE Generator IPコアを使用するには、Xilinx社のライセンスが必要です。詳細については、Xilinx社のIP製品のページを参照してください。

数学関数

CORE Generatorパレットでは、基本的なものから高度なものまで幅広い数学関数を使用できます。たとえば、FPGA上で浮動小数点数に変換したり、浮動小数点数の基本演算を行ったりすることを目的としたIPを生成するためのブロックが用意されています。図6に示すように、IP構成ウィザードを使用して、コードの生成対象となる浮動小数点演算を簡単に選択することができます。

図6: Xilinx CORE GeneratorのFloating-point Operator IPコアには、LabVIEW FPGAで使用できる浮動小数点演算の関数ライブラリが用意されています。

図7: 数学関数パレット | IP製品ページ |

|

メモリおよびデータストレージ要素

図8: メモリおよびストレージ要素パレット | IP製品ページ |

産業における特定用途向けの高度なパレット

CORE Generator IPパレットには、通信用と画像処理用の2つのパレットが用意されており、これらを使用することで、FPGAの設計時間を短縮できます。

通信およびネットワーク

図9: 通信およびネットワークパレット | IP製品ページ |

エラー訂正IP 3GPP2 Turbo Decoder1 Viterbi Decoder1 3GPP Searcher1 LTE FFT 1 ワイヤレスIP DPD1 Peak Cancellation Crest Factor Reduction1

|

1このCORE Generator IPコアを使用するには、Xilinx社のライセンスが必要です。詳細については、Xilinx社のIP製品のページを参照してください。

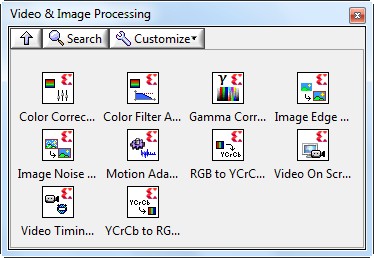

ビデオおよび画像の処理

1このCORE Generator IPコアを使用するには、Xilinx社のライセンスが必要です。詳細については、Xilinx社のIP製品のページを参照してください。

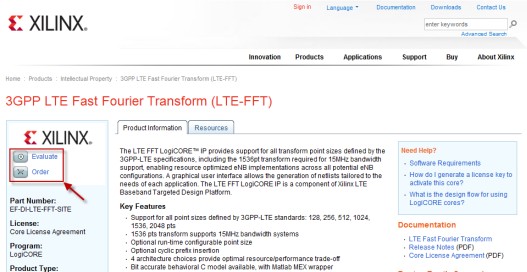

Xilinx CORE Generator IPブロックのライセンス

注記しましたが、一部のXilinx IPブロックを使用するにはライセンスが必要です。ライセンスの費用や取得の手順については、上記のIPブロックのリンクをクリックしてください。

図11: Xilinx社のIP製品ページには、ライセンスが必要となるCORE Generatorブロックの評価や注文に関する情報が記載されています。

CORE Generator IPを使用した開発に関する注意事項

LabVIEW FPGAの他の高性能IPブロックと同様に、アプリケーションの開発でCORE Generatorライブラリを使用する場合は、注意事項がいくつかあります。たとえば、CORE Generator IPは、シングルサイクルタイミングループの内側でのみ実行できます。また、CORE Generator IPは高性能の数学関数と同様に内部でパイプライン処理されている場合が多く、すべてのクロックで出力データが有効になるわけではありません。IP制御信号出力を使用して、データが有効であることを通知する必要があります。

さらに、Xilinx CORE Generatorライブラリがサポートしているのは、Xilinx社のVirtex-5 FPGAとSpartan-6 FPGAのみです。そのため、これらのFPGAターゲットのいずれかに対応しているNI再構成可能I/Oハードウェアを使用する必要があります。

詳細な注意事項については、製品ページにあるIPブロックのデータシートを参照してください。

CORE Generator IPブロックをLabVIEWに組込む

一例として、CORE GeneratorパレットのFloat-point Operator IPコアを使用して、浮動小数点の平方根を求める演算の実行方法を紹介します。

- LabVIEW FPGAプロジェクトを新規に作成します (この例では、NI cRIO-9113シャーシ内のVirtex-5 FPGAをターゲットにしています)。

- FPGA VIを新規作成します。プログラミング→Xilinx Coregen IP→数学関数→浮動小数点を選択し、浮動小数点IPコアをFPGAのブロックダイアグラムにドラッグします。

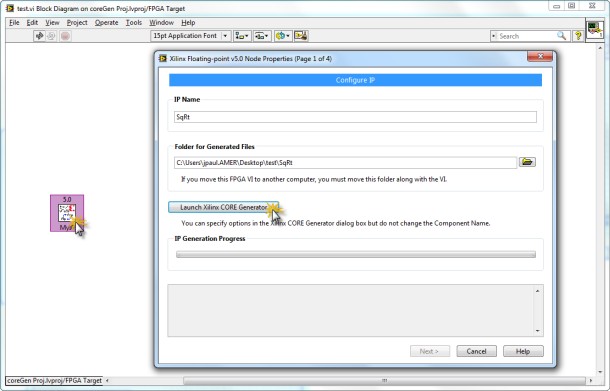

FPGA VIを保存し、IPブロックをダブルクリックして、「Xilinx Floating-point v5.0ノードプロパティ (Xilinx Floating-point v5.0 Node Properties)」ウィンドウを開きます。CORE GeneratorのIP構成ウィザードを起動するために、「Xilinx CORE Generatorの起動」をクリックします。

図12: Xilinx CORE Generatorを起動する。

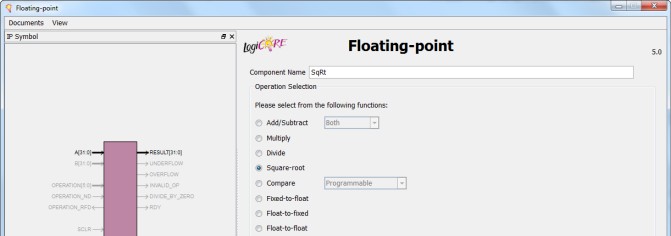

このダイアログウィンドウで、実行する浮動小数点演算の関数を選択します (ここでは、「平方根」を選択します)。ウィザードの他の設定はデフォルトのままにして、残りのステップをすべてクリックして進めます。最後に「生成」ボタンをクリックします。IPコアの生成が完了するまで、数分かかる場合があります。

図13: IPコアを生成する。

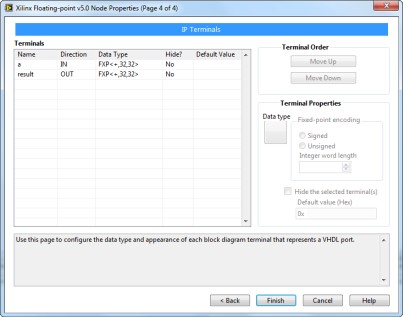

IPの生成が完了したら、「Xilinx Floating-point v5.0ノードプロパティ (Xilinx Floating-point v5.0 Node Properties)」ウィンドウの次の2つのプロパティはデフォルト設定のままにしておきます。クロック信号を選択し、リセット時の動作を構成することで、ブロックをカスタマイズすることができます。「終了」をクリックして生成処理を完了します。

図14: 生成処理を完了する。

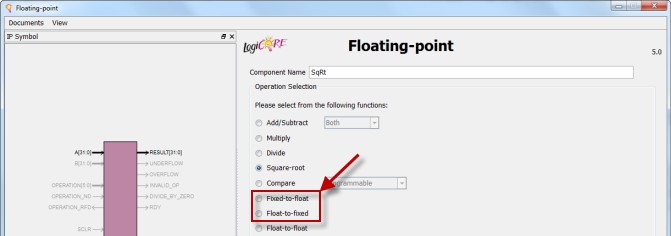

ステップ2~5を2回繰り返して、IPブロックをさらに2つ生成します。1つは固定小数点から浮動小数点へのデータタイプ変換用IPブロック、もう1つは浮動小数点から固定小数点へのデータタイプ変換用IPブロックです。図15に示すように、Floating-point Operator CORE Generator構成ウィザードの最初のステップでこの変換機能を選択してください。

図15: Floating-Point Operator CORE Generatorウィザード

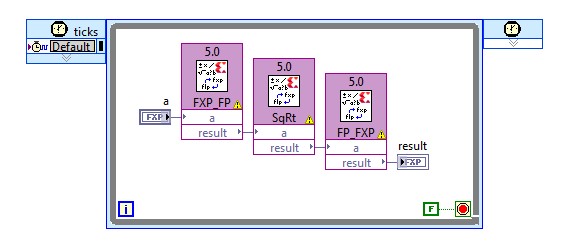

- 最後に、図16に示すように、これらのIPブロックを配線して、シングルサイクルタイミングループ内にロジックを配置します。

図16: IPブロックを配線して、シングルサイクルタイミングループ内に配置する。

ここまでの操作で、浮動小数点の平方根を求める演算を実装することができました。これは、新規または既存のLabVIEW FPGAアプリケーションに組み込むことができますす。

他社製IPを別の方法でインポートする

他のVHDLまたはVerilog IPを取得あるいは作成していた場合、コンポーネントレベルIP (CLIP) ノードまたはIP統合ノードを使用してそれをインポートできます。

詳細については、「CLIPノードを使用して、外部IPをLabVIEW FPGAにインポートする」を参照してください。

FPGA用に最適化された高度な機能

自由に使用できるIPが増えるほど、LabVIEW FPGAアプリケーションをより効率的に開発できるようになります。Xilinx CORE Generator IPパレットでは50を超えるIPコアを利用でき、Xilinx FPGA用に最適化された非常に高度な機能が提供されています。また、搭載されている構成ベースのウィザードを使用することで、お客様固有のアプリケーションに応じて、簡単にIPブロックを設定しカスタマイズすることができます。