LabVIEW FPGAでデジタル通信インタフェースを開発

概要

テストアプリケーションの開発において、未サポートまたはカスタムデジタル通信プロトコルを使用する代わりにLabVIEW FPGAモジュールを使用することで、FPGAベースのRシリーズ再構成可能I/Oハードウェアでさまざまな通信インタフェースの実装およびプロトタイプ作成を行えるようになりました。ASICや独自のVHDLコードの書き込みなど、カスタムハードウェアを設計し構築してからFPGAで実行するのとは異なり、LabVIEW FPGAモジュールでは、特殊な開発ツールを必要とせずに新規機能の開発、テスト、デバッグを迅速に行うことができます。

内容

LabVIEW FPGA

自動車、航空宇宙などさまざまな業界におけるテストシステムの開発で共通して必要とされているのは、テストシステムとテスト対象デバイス間のデジタル通信用インタフェースの開発と実装です。これらのテスト対象デバイスには、その他のテストシステムまたはコンピュータ、計測器、DUT、ECUなどの低レベルシステムコンポーネントなどが含まれます。

理想的には、新しいテストシステムを開発する場合、アプリケーション開発ツールで簡単に使用できるドライバを含むデジタル通信プロトコル用のインタフェースが既にあることです。ただし、多くの場合そのような構成にはなりません。外部デバイスと通信するボードやその他のインタフェースを開発する必要がある場合がほとんどです。その場合、独自のASICを設計するなど、独自のカスタムハードウェアを開発したり、少なくとも既成のコンポーネントを基にボードをはんだ付けする必要があります。しかしながら、再構成可能I/OハードウェアおよびLabVIEW FPGAモジュールでは、LabVIEWとそのグラフィカルプログラミングツールのみを使用してカスタムハードウェアを設計できます。カスタムハードウェア設計は再構成可能I/OハードウェアのFPGAにロードして、ニーズに特化したカスタムインタフェースボードを作成することができます。

このドキュメントでは、LabVIEW FPGAモジュールを使用して、さまざまな通信プロトコルをカスタムインタフェースボードに実装する方法を説明します。この方法は、プラグインPCIおよびPXI再構成可能I/Oカード (Rシリーズ) およびCompactRIOプラットフォームで、安定した業界対応の筐体を利用することができます。

デジタル通信プロトコル

テストシステムでは、RS-232およびGPIBなど一般的なインタフェースから、個々のベンダやアプリケーション開発者により実装されるカスタムプロトコルなど、幅広い通信プロトコルが使用されています。一般的ですが広く知られていないインタフェースには、電子デバイスおよびシステム間の通信に使用されるSPI (シリアルペリフェラルインターフェース) および I2C (Inter-Integrated Circuit) があります。これらのプロトコルはアプリケーションでは一般的ですが、さまざまなプラットフォームおよびソフトウェア環境で使用可能な通信インタフェースによって必ずしもサポートされているわけではありません。このような場合に、LabVIEW FPGAおよび再構成可能I/Oプラットフォームは、コスト効率に優れたソリューションを提供するための理想的なツールとなります。

デジタル通信プロトコルは、アプリケーションの分野、業界、またはプロトコルの性質や技術仕様に基づいてグループ化することができます。以下のセクションでは、各プロトコルの技術的な詳細と性質、そしてLabVIEWでこれらを実装する方法について説明します。以下は、アプリケーションおよび業界の基本カテゴリ、そしてLabVIEW FPGAで作成できる通信インタフェースのサンプルプロトコルです。

コンポーネント/IC通信

-

電子設計:SPI、I2C、JTAG、PS/2など

システム通信

-

航空宇宙:MIL-STD-1553、ARINC 429など

-

自動車:CAN、MOST、KWP、1939など

通信

-

衛星および航空宇宙通信:PCM/Telemetry

民生用電子機器

-

デジタルオーディオ:S/PDIF、I2S

カスタム

-

デバイス特有の実装

プロトコルの分類

デジタル通信プロトコルは、技術定義や要件に基づいて分類することができます。アプリケーションに依存せずにプロトコルを考察する方法は、開発ツールで最適な実装を選択する際に役立ちます。このドキュメントの後半では、これらの分類の基準、そしてさまざまなグループのプロトコルをFPGAで実装する方法について説明します。

通常のデジタル通信インタフェースは、送信側と受信側の間のデータ信号数により、シリアルとパラレルの2つの一般的なカテゴリに分けることができます。データが単一のデータラインで転送されると、すべてのデータビットは順番または連続して転送されるため、シリアルデータリンクとなります。パラレルデータリンクには、通常8データラインの倍数である複数のデータラインがあります。データは、通常は一度に1バイトまたはワードで並列に転送されます。従来、シリアル (RS-232など) とパラレル (GPIBなど) 通信リンクの両方が、同じクロックレートでより高いデータ転送レートを提供するパラレル通信リンクで使用されていました。単一のデータラインで可能なビットレートがメガビットおよびギガビットに増加すると、インタフェースコンポーネント (例: ラインドライバ) やケーブル接続コストがより少ない、コスト効率に優れたシリアルリンクが市場で一般的になりました。シリアルとパラレルの両通信インタフェースには、クロックとトリガ、そして通信の制御およびコマンド発行に使用される追加の信号ラインが存在する場合があります。

物理通信インタフェースにおける2つ目の基本的な分類基準は、デジタル信号ラインに使用される電圧レベルと接地基準です。データビットおよびその他の情報は、信号ラインの電圧レベルを変化することにより転送されますが、インタフェースによって使用される電圧レベルには大幅な違いがあります。シングルエンドデジタル信号では、信号ラインの電圧レベルはコモングランド基準に相対して測定されます。差動デジタル信号は、2つの非基準信号で構成され、2つの信号ライン間の電圧レベルは信号値を表します。差動信号は、信号ラインで発生するノイズの影響を受けにくいため、長距離の信号転送によく使用されます。デジタル通信で使用される特定の電圧レベルは、TTL、CMOS、LVDSなどの規格で呼ばれますが、FPGAにおけるプロトコル実装では使用されません。再構成可能I/Oハードウェアのデジタル入出力は、TTL/CMOS互換電圧レベルを使用します。 他のレベルが必要な場合は、インタフェースハードウェアと通信リンクの間に信号変換器/変換器を挿入する必要があります。

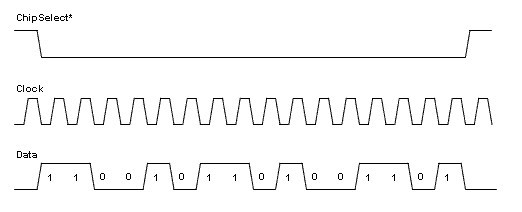

信号とビットバンギング

プロトコルについて分析し、LabVIEW FPGAにおける実装方法を考慮する上で、プロトコルに使用されるさまざまな信号ラインや各信号の目的を認識する必要があります。プロトコルが使用する信号ライン数により、LabVIEWプロジェクトで構成する必要のあるハードウェアリソース数、そしてLabVIEWダイアグラムで使用するデジタルライン数が決定します。SPI (シリアルペリフェラルインタフェース) プロトコルを示す以下のタイミング図 (図1) は、このプロトコルを実装する上で管理する必要のある3つの信号ラインを示してします。

図1:1つのデータラインを使用するSPIプロトコルの簡易タイミング図

実装を始める際に、タイミング図をLabVIEW FPGAコードに変換するには、デジタルラインをオフ/オフにする、そして異なるデジタルライン状態の設定間で適切な時間を待機するという2つの操作を行う必要があります。デジタルプロトコルを読み取るアプリケーションでは、デジタルラインの状態を読み取り、各信号ラインの遷移時間に注意する必要があります。通常、デジタルプロトコルの出力は実装よりも簡単であるため、先に説明します。

クロック機能

プロトコルを分類する次の基準は、プロトコルにより使用されるクロックソースです。2つの主なカテゴリとして、同期および非同期プロトコルがあります。同期プロトコルにはプロトコル特定のタイミング信号が含まれ、非同期プロトコルは定義ビットレートによりタイム付けされます。

同期プロトコルの一般的な例は、上記のタイミング図に示されるSPIプロトコルです。プロトコルには専用のクロック信号が含まれ、データラインが読み書きを行うタイムベースとして、受信側がクロックラインを使用することが可能です。おそらく最もよく知られている非同期プロトコルは、多くのPCで使用されているシリアル (RS-232) バスです。シリアルバスを使用する場合、通信するデバイスのボーレート (ビット/秒) を指定します。ボーレートは、送信側と受信側で同じレートに設定して、データ信号を書き込みまたは読み取ります。タイミングソースは通信の両端で厳密に同じではないため、ビットのずれが起こるのを防ぐために、同期通信データパケットの長さは制限されています。非同期通信は、頻繁に再同期して、僅かなタイミング差を許可する必要があります。一方、同期通信プロトコルは、各データビットで同期され、連続して通信を行うことが可能です。

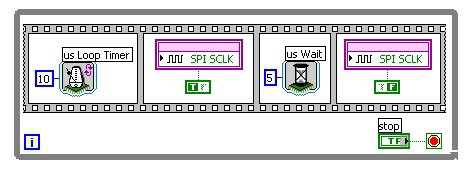

クロック信号を非同期プロトコルの一部として実装すると、FPGAクロックはプロトコルのタイムベースの決定に使用され、それに従ってクロック信号が更新されます。

図2:10 μs (100 kHz) クロック信号を生成するLabVIEW FPGAの図

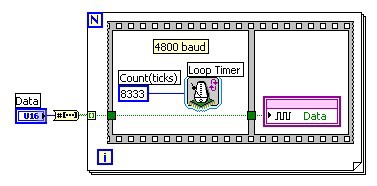

非同期プロトコルの場合、個別のクロック信号は生成されませんが、FPGAクロックおよび定義済みのボーレートがデータ信号の書き込みと読み取りのタイミングを決定するために使用されます。

図3:4800ボーでデータラインを更新するLabVIEW FPGAの図

(8333 FPGAクロックサイクル = 208.3 μs = 1/4800 Hz)

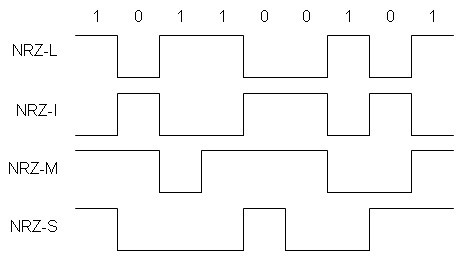

符号化/復号化―パルスコード変調

クロック信号またはタイミング仕様により指定されるレートに基づき、データはデータ信号で符号化されたり、データ信号から読み取られた後符号化されます。 データのエンコードは、さまざまな形式で実行できます。最も一般的な方法は、1データビット値をデジタル信号の1または数種類の状態で示す方法です。この一般的な符号化の方法は、パルスコード変調 (PCM) と呼ばれます。

データビットがデータ信号の単一の状態で表されるPCM方式のサブセットは、非ゼロ復帰 (NRZ) と呼ばれます。 たとえば、HIGHデータ信号は「1」ビットを表し、LOWデータ信号は「0」ビットを表します。この方法では、データ信号のレベルがデータビットを示すためNRZ-Lと呼ばれます。RS-232などの一部のプロトコルでは、HIGH状態が「0」、LOW状態が「1」を示し、この論理は逆になります。この方法はNRZ-I (inverse) と呼ばれます。その他のNRZのサブタイプには、NRZ-M (mark) およびNRZ-S (space) があり、「1」データビット値はデータ信号 (NRZ-M) の変化、「0」はデータ信号 (NRZ-S) の変化で示されます。

図4:非ゼロ復帰 (NRZ) 符号化方式

パルスコード変調には、クロック信号とデータ信号を1データラインに組み合わせ、各ビットがデータ信号の複数の状態で示される別の符号化方法も含まれます。これらは、2相符号化と呼ばれ、一般的なマンチェスタ符号化方法がその例の1つです。

その他のより上級な符号化方法には、異なる形式のパルス幅符号化があります。一般的なパルス幅変調 (PWM) 方法では、アナログ値を一定の周波数パルス列の変動するパルス幅に直接変換します。その他のパルス幅符号化では、異なるパルス幅を使用して「0」および「1」ビットを従来のビットシーケンスで示します。

LabVIEW FPGAにおける実装

ここまで一般的なプロトコルに関する基本用語について説明しました。ここからはプロトコルをLabVIEW FPGAに実装する方法について説明します。プロトコルをLabVIEW FPGAに実装するには、まずタイミング図について一通り理解し、異なる信号ラインの状態変化、そしてこれらの変化間のタイミングを対応するLabVIEW関数およびストラクチャに変換します。各デジタルラインの状態変化はFPGA I/Oノードを使用して実装し、タイミングはLabVIEW FPGAタイミング関数 (「ループタイマ」および「待機」) を使用して実装します。タイミング図で繰り返される手順は、ForループまたはWhileループを使用して実装します。より詳細な関数およびストラクチャのプロトコルグループは、サブVIとしてカプセル化されているため、コードを再利用、モジュール化、管理することが可能です。

SPI出力

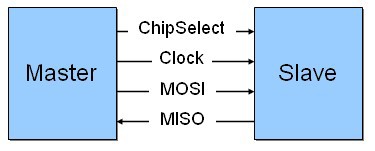

最初の例として、上の図1に示すSPIタイミング図を実装します。 SPIプロトコルを使用した通信は、2つのデバイス間で送信されるデータのパケットで構成されます。SPI通信には、ChipSelect信号およびClock信号を制御するマスタデバイスがあります。マスタデバイスと、ChipSelect信号ラインを持つ単一または複数のスレーブデバイスがあり、すべてのデバイスに共通するデータラインがあります。アプリケーションにマスタとスレーブ間の両方向の通信が存在する場合、MOSI (Master Out Slave In) およびMISO (Master In Slave Out) と呼ばれる2つのデータラインが通常使用されます。ここでは1つのデータラインについてのみ説明します。

図5:2つのデバイス間のSPI通信の配線図

パケット転送は、アドレス指定されるスレーブデバイスのChipSelectラインをアサートすることで、常にマスタデバイスにより開始されます。ChipSelectラインは通常、アクティブLOWでシステムのアイドル時にHIGH状態を維持しますが、マスタデバイスが転送を開始するためにLOWにプルダウンされます。マスタデバイスは、ChipSelect信号のアサート後にデータラインを更新し、クロックラインを切り替えて各データビットをスレーブに転送します。データパケットの内容はアプリケーション特有で、開発者やデバイス設計者により定義されます。

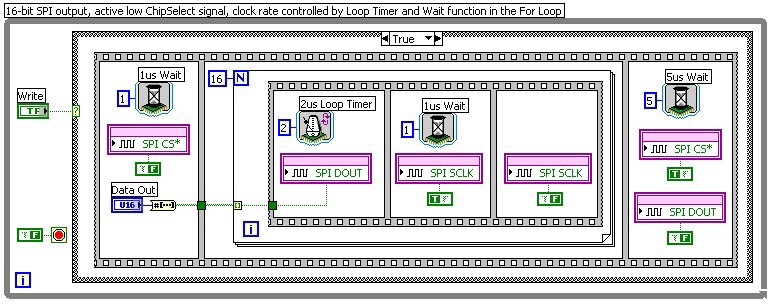

下の図6に示すLabVIEW FPGAダイアグラムでは、各データ転送は「書き込み」ブール制御器を設定することで開始されています。これにより、TRUEケースが実行されます。まず、デジタル出力をLOWに駆動することで、ChipSelectライン (SPI CS*) がアサートされます。同時にデータ値「データ出力」が対応するビットのシーケンス (ブール配列) に変換されます。1マイクロ秒 (1 μs) の待機関数は、スレーブデバイスが次のデータビットの準備を完了するまでの時間を提供します。その後、データラインの更新およびクロックラインの切り替えのシーケンスがForループで16回繰り返されます。ブール配列の各ビットはデータライン (SPI DOUT) に出力され、最初にHIGH、その後LOWに設定されたクロックライン (SPI SCLK) が続いて出力されます。「ループタイマ」関数は、「待機」関数がクロック信号の高位相の長さを1 μsに制御し、500 kHz 50%デューティーサイクルクロック信号を生成する際、ループが2 μs間隔で実行するようにします。16ビットすべてが生成されると、ChipSelectおよびデータラインはアイドル状態に戻り、5 μsの最小待機時間が「待機」関数により挿入されます。この時点で、FPGAは次の書き込みコマンドを行うことができます。

図6:シンプルなSPI出力の実装方法を示すLabVIEW FPGAの図

使用するSPIデバイスの仕様およびアプリケーションに基づき、通信パラメータ (転送されるデータビット数、クロック信号の周波数など) はダイアグラムで調整するか、LabVIEW FPGA VIのフロントパネルにある制御器により動的に制御します。

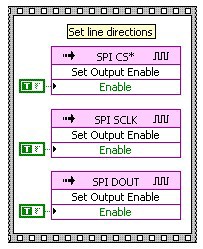

必要な場合、アプリケーションで使用される各デジタルラインの方向は、「出力有効化を設定」FPGA I/Oメソッドノード (図7を参照) を使用してプログラムで設定できます。

図7:デジタルラインのLabVIEW FPGA初期化

SPI入力

プロトコルの入力の実装には、コードがプロトコルの検出および処理を行う上で、より柔軟でなければならないため、いくつかの課題があります。デジタル出力ラインを更新し、適切な遅延を挿入する代わりに、コードは異なるデジタルラインの状態を管理し、必要に応じて信号ラインの特定な遷移時間を測定します。

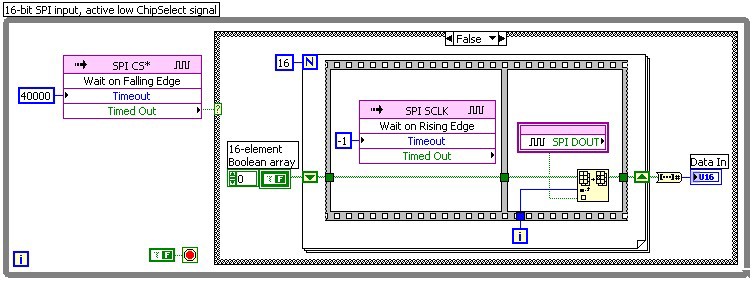

以下の例は、前のSPI出力の例に対応する基本的なSPI入力の実装方法を示します。FPGAは、アイドル時にChipSelectラインを監視し、立ち下がりエッジを検出します。立ち下がりエッジが発生すると、クロックラインの監視を開始します。クロック信号の16個の各立ち上がりエッジでは、FPGAはデータ信号を読み取り、予め割り当てられたブール配列にビット値を保存します。16クロックサイクル後に、データパケットの終わりでブール配列は整数データ値に変換され、VIのフロントパネルで使用できるようになります。

図8:シンプルなSPI入力実装のLabVIEW FPGAの図

SPIプロトコルの性質により、タイミングがすべてプロトコルのエッジで直接制御されるため、この例では時間測定を行う必要はありません。

実装に関する注意事項

このセクションでは、LabVIEW FPGAを使用してデジタル通信プロトコルを開発する上で考慮すべき事項について説明します。

オープンコレクタ/オープンドレイン信号ライン

上記のSPIの例では、各信号ラインは単一のデバイスのみにより駆動されました。ただし多くのプロトコルでは、バスまたは通信の状態により、信号ラインは複数のデバイスにより駆動または制御される場合があります。そのため、複数のデバイスがバスで転送を開始したり、同じデータラインを使用してデータを送受信する必要があります。通常これは、オープンコレクタ/オープンドレイン回路を使用して実行されます。この構成では、デバイスは信号ラインをLOWのみに駆動またはプルダウンすることが可能ですが、ラインをHIGHに設定する場合やラインを駆動しない場合に信号ラインを浮動することが可能です。信号ラインに接続されている各デバイスの他に、信号ラインには設定されている電圧に対しプルアップ抵抗があり、接続されているデバイスが信号LOWを駆動しない場合にラインのHIGH電圧を確立します。この設定では、異なるデバイス間で電圧の競合が起こらずにラインをLOWに駆動することが可能です。このような信号はアクティブLOWと定義され、ラインがバスのアイドル時にHIGH状態で、デバイスがラインをLOWにプルダウンして信号をアサートすることを示します。アクティブLOW信号は通常、信号名に線が引かれるか、上記の例で使用したChipSelect* (SPI CS*) 信号のように、信号名の後にアスタリスクを付けて示します。

オープンコレクタ信号をLabVIEW FPGAで実装するには、デジタルラインの方向を制御する機能を使用して、LOWに駆動と浮動の切り替えを行います。LabVIEW FPGAでは、I/Oメソッドノードがデジタル出力ラインの有効化/無効化に使用されます。ラインが無効な場合、FPGAはデジタルラインを駆動せず、HIGHの浮動状態を許可します。ラインが有効な場合にラインをLOWに駆動するには、「出力データ」をFALSEに設定します。出力データは、ラインが駆動に設定されるかラインが浮動するかに関係なく値を維持するソフトウェアレジスタです。

以下の図は、I2C (Inter-Integrated Circuit) プロトコルの場合のLabVIEW FPGAにおけるオープンコレクタ構成の例です。I2Cは、EEPROM、ADC、DACなどのさまざまなタイプの集積回路と通信するためにSPIと類似のアプリケーションで使用されます。I2Cバスにはクロックとデータの2つの信号ラインのみがあり、それぞれはオープンコレクタラインです。通信の適切な受信側を選択するには、送信側がまず受信デバイスを指定する固有のデバイスアドレスを転送します。

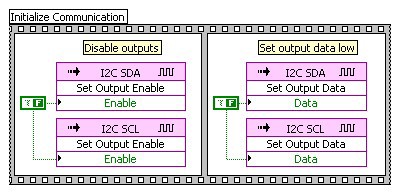

オープンコレクタ通信のVIを初期化するには、2つの信号ライン (SCLとSDA) を無効にし、バスをアイドル状態にします。各信号の出力データはFALSEに設定されています。ここからは、各ラインの状態は「出力有効化を設定」メソッドを使用して制御されます。ラインを有効化するとLOWに駆動し、無効化するとHIGHに浮動します。

図9:2つのデジタルラインをオープンコレクタ通信用に構成する

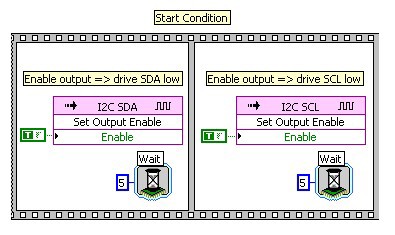

I2Cバスで転送を開始するには、送信側がデータラインをLOWに駆動 (SDA) した後に、クロックラインをLOWに駆動 (SCL) することにより開始条件を転送します。

図10:I2C開始条件をバスで実装する

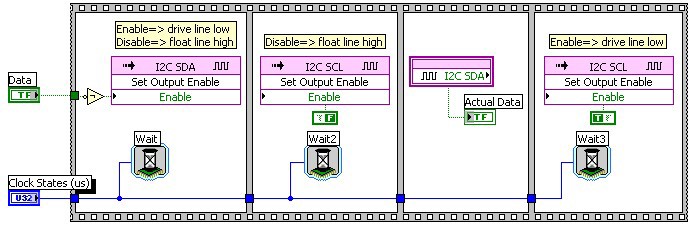

I2Cバスでデータビットを転送するには (図11を参照)、送信側がデータラインを更新 (1番目のフレーム)、その後クロックラインをHIGHに切り替えてから (2番目のフレーム)、LOWに切り替えます (4番目のフレーム)。

各データバイト (8ビット) の転送後、I2Cプロトコルでは余分な1クロックサイクルが通信に挿入され、受信デバイスが前回のバイトの正常な受信を認識することを可能にします。この目的のため、受信側は9回目のクロックサイクルでデータラインをLOWにプルダウンします。送信側は、HIGHデータビットを送信し、クロックサイクル中にデータラインの実際の状態を確認する (3番目のフレーム) ことにより実装されます。送信側がデータをHIGHに浮動しても、受信側はデータをLOWにプルダウンして最後のデータバイトと認識するため、実際のデータ値はLOWである必要があります。

図11:I2Cバスでデータビットを転送する

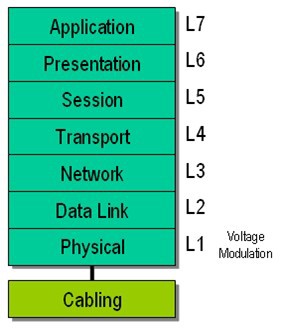

OSI参照モデル

OSI (Open Systems Interconnection) 参照モデルは、通信プロトコルを使用するアプリケーションを含む、通信プロトコルの異なる論理層を示します。これは、プロトコルおよびネットワークのさまざまな側面をより良く定義し、理解するために使用されています。

図12: OSI参照モデル

第1層は物理層で、キャリアでデータを送信する機能を提供する電気および機械の詳細を処理します。簡易な同期パケットがこのレベルで動作します。

第2層は、ビットおよびバイトレベルデータの基本定義、そしてNRZおよび同期の超越する変調を提供します。

次の数層では、アドレス指定、データパケットの定義、エラーチェックなどが行われます。

上記の例に示されるように、L1物理層でFPGAが動作し、電気的レベルで各デジタル入力および出力ラインに直接接続します。これは、LabVIEW FPGAにおいてデジタル通信プロトコルを開発する際、開発者がプロトコルおよびアプリケーションに関する参照モデルのすべての層を管理する必要があるということです。多くの簡易プロトコルでは、アプリケーションとFPGA間の通信を確立させ、プロトコルを使用するためにプロトコル層の上にインタフェースを追加するには、ここまで行った操作の他に多少のプログラミングが必要です。ただし、より複雑なプロトコルでは、バスレベルエラー検出、ハンドル、パケットの構築と構文解析、異なるタイプのパケット処理など、これらの中間プロトコル層を追加するには多大なプログラミング作業が必要です。

タイミングおよび分解能

上記で述べたように、タイミングはプロトコル実装を開発する上で極めて重要です。データとクロックラインは、正確な間隔で更新する必要があります。 プロトコルをデコードする際は、これらの同じ間隔を正確に測定することが重要です。通信プロトコルを開発し、実装がプロトコルの要件と仕様を満たすことを確認するには、FPGAのタイミング動作に注意する必要があります。

FPGAはベースクロック周波数で動作し、すべてのタイミング関数は同じクロックレートに基づいています。LabVIEW FPGAでは、デフォルトのFPGAクロック周波数は40 MHzであるため、各クロックサイクルおよび時間の単位は25ナノ秒 (ns) です。LabVIEW FPGAでは、タイミング関数の間隔をミリ秒、マイクロ秒、ティック数で指定できます。各ティックは1クロックサイクルまたは25 nsに対応します。 つまり、遅延またはループ反復時間を指定するための最大分解能は25 nsです。これは非常に正確に聞こえますが、逆数を計算する場合や生成可能な周波数を決定する場合に、より高いレートで影響が発生します。

デジタルラインに1 MHz更新レートを生成するには、40ティックに設定された「ループタイマ」関数を使用できます。

1 MHz => 1 μs = 1000 ns

1000 ns / 1ティックあたり25 ns = 40ティック

1.25 MHzの更新レートが必要な場合

1.25 MHz =>0.8 μs = 800 ns

800 ns / 1ティックあたり25 ns = 32ティック

1.25 MHzの場合は32ティックの遅延を使用します。1.1 MHzの更新レートが必要な場合

1.1 MHz => 0.9091 μs = 909.1 ns

909.1 ns / 1ティックあたり25 ns = 36.36ティック

特定の部分クロックサイクルを選択できないため、遅延が900 nsで1.111 MHzの周波数に対応する36クロックサイクルを選択します。次に使用できる低周波数は、37ティックまたは1.081 MHzです。40 MHzのFPGAクロックを使用すると、1.081 MHzまたは1.111 MHzでデジタルラインを更新でき、その間の値では更新できないことがわかります。

FPGAプロパティおよびクロックリソースをLabVIEWプロジェクトで使用する場合、FPGAベースクロックの周波数を80または120 MHzに変更するオプションがあります。これにより、FPGAはより高い周波数で動作し、タイミング関数のタイミング分解能が向上されます。ただし高周波数では、FPGA VIダイアグラムで使用し、FPGAにコンパイルされる機能が減少します。

タイミングプロトコルの実装を計画する際、FPGAのタイミング分解能がプロトコルとアプリケーションの要件を十分に満たすことを確認する必要があります。これは、上記の計算に示されるように、プロトコルの生成に必要なタイミングにおいて特に重要です。プロトコルの読み取りおよび復号化では、プロトコルの最大更新レートより高いレートで信号ラインを読み取ることができれば十分です。起こりえる問題を回避するには、信号を更新レートの2倍の速度でサンプルする必要があります。

プロトコルに含まれるデータを復号するには、入力信号で時間測定を行った後に、追加の計算を行ってプロトコルの正確な復号に必要なタイミング分解能を決定します。

ステートマシン

ステートマシンは、デジタル通信プロトコルの符号化または復号化を実装する上で役立つ手法です。LabVIEWでは、Whileループおよびケースストラクチャを使用してステートマシンを簡単に実装し、異なる状態を表すことができます。

ステートマシンは、タイミング図を異なるステップに分割するため通信プロトコルの開発に役立ち、LabVIEW FPGAダイアグラムで各ステップを異なる状態に変換できます。これにより、各プログラムのステップが区別されるため、実装で行うプログラミングを簡略化できます。また、プロトコルの実行から特殊エラー処理状態に簡単に移動できるため、エラーおよび例外処理などの一般的な操作も簡略化できます。プロトコル仕様はステートマシンで作成されている場合がありますが、LabVIEWのステートダイアグラムに直接変換することができます。

図1のSPIタイミング図では、以下のステップを使用してタイミング図を分割し、ステートマシンを作成できます。

- ChipSelectをLOWに設定

- データ (0) を設定

- クロックをHIGHに設定

- クロックをLOWに設定

- データ (1) を設定

- クロックをHIGHに設定

- クロックをLOWに設定

- (ビット2~15でデータとクロックを繰り返す)

- ChipSelectをHIGHに設定

5つの固有のステップがあり、各データビットで繰り返されるものもあります。 当初は、これらの繰り返しステップをForループで実装していました。ステートマシンでは、これらの5つのステップに固有の状態を作成し、それらを繰り返します。データラインを更新し、クロックラインを切り替える3つの繰り返しステッでは、ステートマシンを構成し、最後のステップを行う前にこのシーケンスを16回繰り返します。LabVIEWステートマシンでは、Whileループのシフトレジスタのカウンタを使用して実装できます。

シングルサイクルタイミングループの使用

ステートマシンアーキテクチャのもう1つの利点は、LabVIEW FPGAシングルサイクルタイミングループ (SCTL) 内でプロトコルの実装を行えることです。SCTLでは、LV FPGAダイアグラムを迅速に実行でき、ループの各サイクルを1クロックサイクルで実行できます。これにより、FPGAベースクロックの周波数で信号ラインを更新できます。SCTLはまた、コード生成を最適化するため、FPGAのコードがより効率的になり、使用されるスペースも減少します。ただし、SCTLの内側で実装されるコードにはいくつかの制限があります。たとえば、SCTLの反復につき一度に1ラインのみしかアクセスできません。そのため、各状態で一度に1つの信号ラインを更新または読み取るようにステートマシンの状態を定義する必要があります。

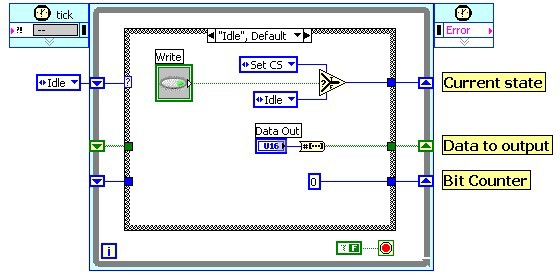

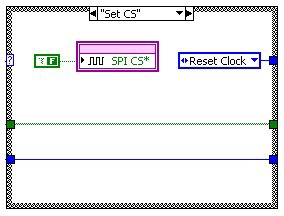

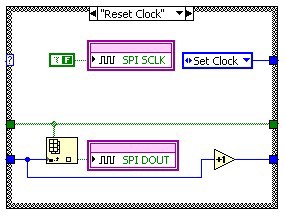

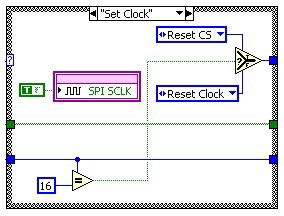

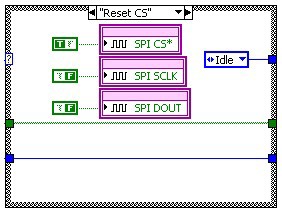

以下のダイアグラム (図13) は、SCTLの内側でステートマシンを使用するSPI出力プロトコルの実装を示します。アイドル状態は、書き込みコマンドが次のデータパケットの出力を開始するのを待機します。また、データ値を出力操作のブール配列に変換します。次のCSを設定ステップは、ChipSelectラインをアサートします。その後、データビットの出力を開始します。クロックをリセットでは、次のビット値でデータラインを更新し、クロック信号をリセットします。クロックを設定では、受信側によるデータ信号の読み取りをトリガするクロック信号を設定します。この状態のペアでは、シフトレジスタのカウンタを増分します。これにより、データラインに送信する適切なデータ値がブール配列から選択されます。16番目のビットを出力した後、すべての信号ラインをバスアイドル状態にリセットするCSをリセット状態に遷移します。そこから、アイドル状態に戻り、次の書き込みコマンドを待機します。

図13:シングルサイクルタイミングループでのSPI出力の実装

2相変調

2相符号化または復号化は、さまざまなプロトコルで使用される一般的なデータ符号化の手法です。データ信号とクロック信号を1信号ラインに組み合わせ、必要なケーブルを減らし、長いケーブル距離におけるデータの整合性を向上させます。