NI USRPハードウェアの仕組み

概要

NI EttusのUSRP (Universal Software Radio Peripheral) デバイスは、ワイヤレスおよびRF用途で使用するソフトウェア無線 (SDR) です。NI EttusのUSRPトランシーバは複数の周波数帯域でRF信号を送受信できるため、通信工学の教育や研究での用途に利用できます。LabVIEW開発環境と組み合わせることで、USRPによって、無線信号を使用してワイヤレスアルゴリズムを検証できる低コストのソリューションを実現できます。

内容

ソフトウェア無線

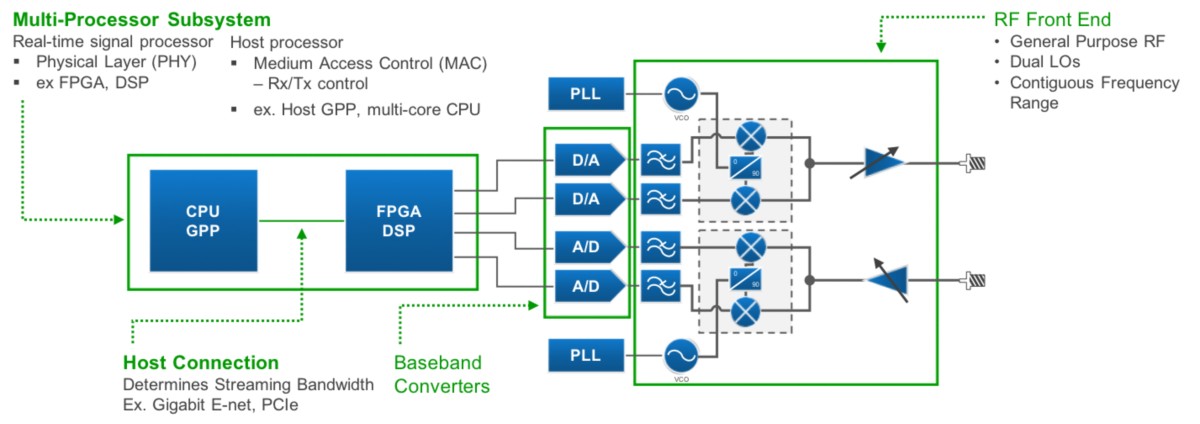

通常、SDRアーキテクチャには、プロセッサが含まれています (オンボードプロセッサまたはコンピュータプロセッサ)。また、FPGAや調整式RFフロントエンドも含まれています。USRPおよびLabVIEWの柔軟性、機能性、低コスト性により、教育機関の研究所や通信研究向けの理想的なSDRプロトタイピングソリューションが実現されます。

図1: ソフトウェア無線の一般的なアーキテクチャ

LabVIEWによって、USRPハードウェアとの間でストリーミングされる信号の変調と復調のための信号処理エンジンが提供されます。LabVIEW Real-TimeモジュールとLabVIEW FPGAモジュールを追加することで、NI Linux Real-Time OSとFPGAをすべて同じ開発環境からターゲットにすることができます。LabVIEWには、実世界のラジオ信号向けに最適化された多くの一般的なアナログ/デジタル変調テクニックと信号処理アルゴリズムの機能ブロックが搭載されています。

一般的な用途

USRPハードウェアは、さまざまな用途に利用できます。ハードウェアの柔軟性と低コスト性により、教育から高度なワイヤレス研究 (動的スペクトルアクセス、ホワイトスペース、物理層/MAC層研究など) まで、多くの分野でUSRP製品を使用することできます。またUSRP製品は、カスタムプロトコルの作成やスペクトルのディスクへの記録など、シンプルな送受信を行う際にも役立ちます。

ハードウェアの概要

3a. USRP (ホストのみ)

図2:NI USRP-2921

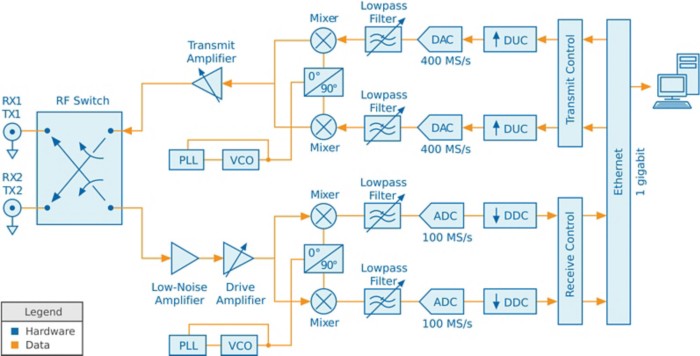

USRPハードウェアは、一般的なSDRアーキテクチャに従い、デジタルダウンコンバージョン (DDC) およびデジタルアップコンバージョン (DUC) ステップのための機能固定のFPGAを備えた高速のアナログ/デジタル変換器 (ADC) とデジタル/アナログ変換器 (DAC) による直接変換アナログフロントエンドを実装します。レシーバチェーンは、極めて小さな信号をも受信し、ダイレクトダウンコンバージョンにより同相 (I) および直角位相 (Q) ベースバンド信号にデジタル化する高感度のアナログフロントエンドから始まります。ダウンコンバージョンの次は、高速A/D変換と、サンプルレートを低下させてIとQをパケット化するDDCを行い、ギガビットEthernetを使用してホストコンピュータに送信し、さらに処理を行います。トランスミッタチェーンでは、まずホストコンピュータでIとQが生成され、Ethernetケーブル経由でUSRPハードウェアに転送されます。DUCはDAC用に信号を準備し、その後I-Qミキサーによって信号が直接アップコンバートされます。そしてRF周波数信号が生成され、増幅されて送信されます。

図3:USRP-2921システムレベル図

3b.プログラム可能なFPGAを搭載したUSRPデバイス

図4:NI USRP-2944

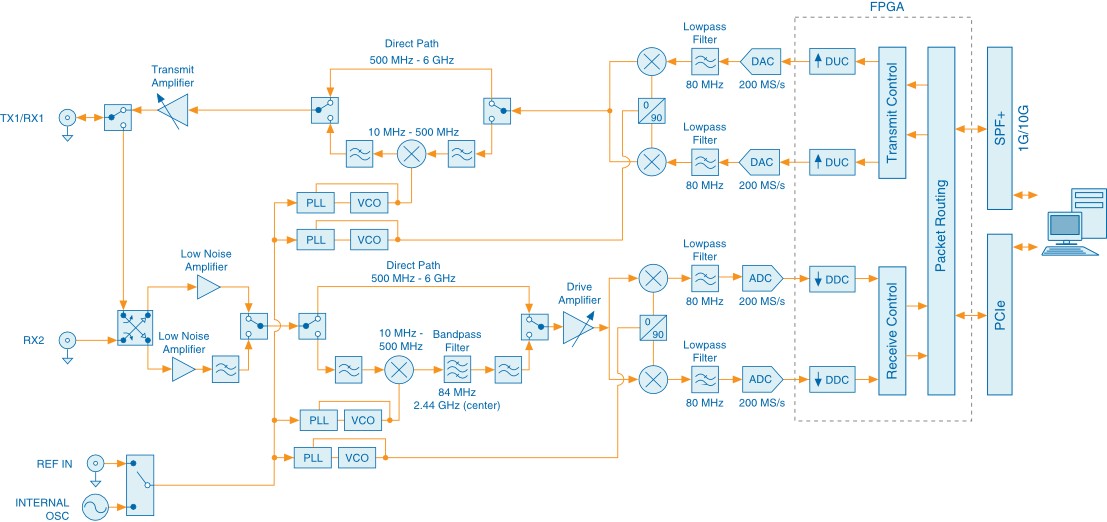

NI USRP-294x/295xデバイスでは、全二重方式の送受信チャンネル (チャンネルあたり最大160 MHzのリアルタイム帯域幅) 2つと、大型DSP指向Kintex-7 FPGAが、ハーフワイド1U型のラックマウント式フォームファクタに収容されています。アナログRFフロントエンドは、クロック速度が120 MS/sのデュアルADCとデュアルDACを使って、大規模なKintex-7 410T FPGAに接続します。

各RFチャンネルにはスイッチが付いており、TX 1 RX1ポートを使った1つのアンテナでの時分割複信 (TDD) 操作と、TX1とRX2の2つのポートを使った周波数分割複信 (FDD) 操作の切り替えができるようになっています。

NI USRP-294x/295xデバイスは、10 MHz~6 GHzの周波数レンジをカバーし、ユーザによるプログラミングが可能なデジタルI/Oラインで外部デバイスを制御できます。Kintex-7 FPGAは、DSP48コプロセッシングを組み込んだ、再構成可能なLabVIEW FPGAターゲットで、高レートで低遅延なアプリケーションに最適です。システムコントローラにPCI Express x4で接続することで、デスクトップまたはPXIシャーシに対して最大800 MB/s、ノートブックPCに対して200 MB/sのデータ転送が可能になります。このような接続方法により、最大17台のUSRPデバイスを1つのPXI Expressシャーシに配線することができ、それらをまとめてデイジーチェーン接続することで、高帯域幅の多チャンネルアプリケーションを作成することができます。

図5:USRP-2944システムレベル図

3c. NI USRP-2974スタンドアロンデバイス

図6:NI USRP-2974

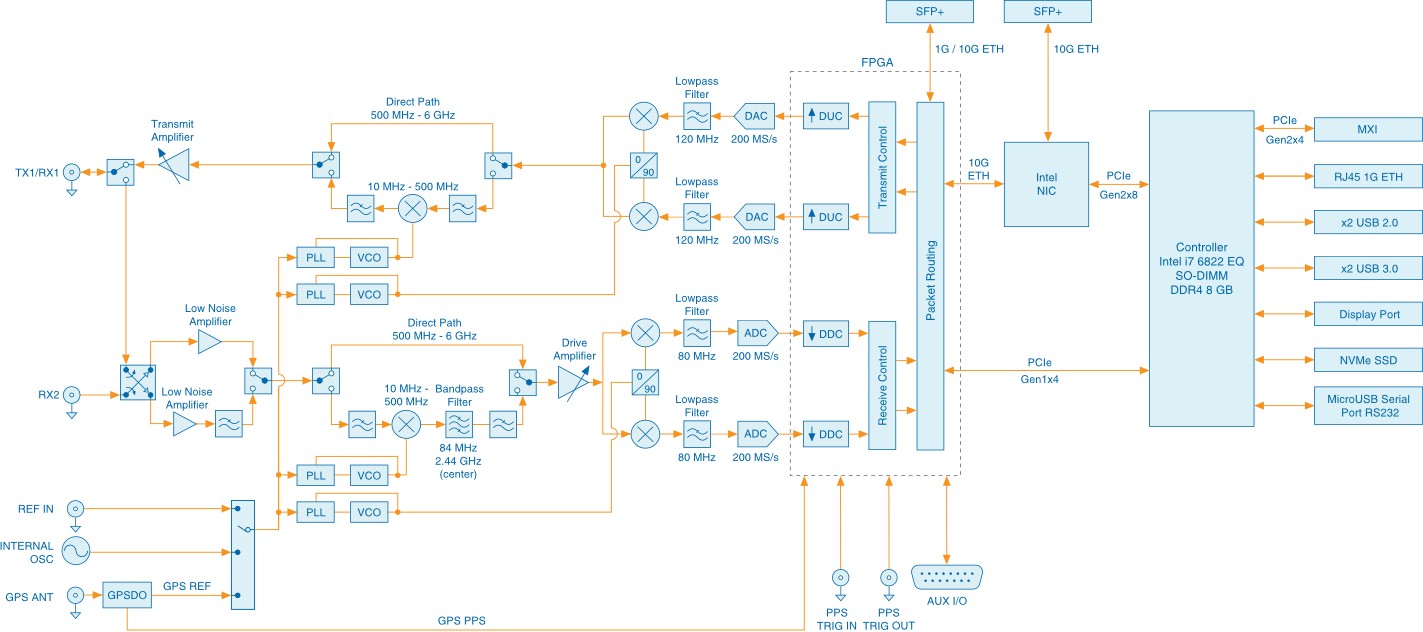

スタンドアロンNI USRP-2974では、オンボードプロセッサ、FPGA、およびRFがすべて1つのフォームファクタに収容されています。USRP-2974は、異種処理アーキテクチャを基に構築されており、NI Linux Real-Time OSを実行するオンボードIntel Core i7プロセッサを搭載しています。この製品は、160 MHzの帯域幅で10 MHz~6 GHzまでの周波数をカバーする2x2無線機で、x86プロセッサを追加してスタンドアロンシステムの操作を形成します。このため、処理の確定的な実行や、Xilinx Kintex 470 FPGAのプログラミングなどをすべて単一の開発環境で行う場合に適しています。また、USRP-2974は、GPS対応の10 MHz恒温槽付水晶発振器 (OCXO) 基準クロックも備えています。

図7:USRP-2974システムレベル図

ソフトウェアの概要

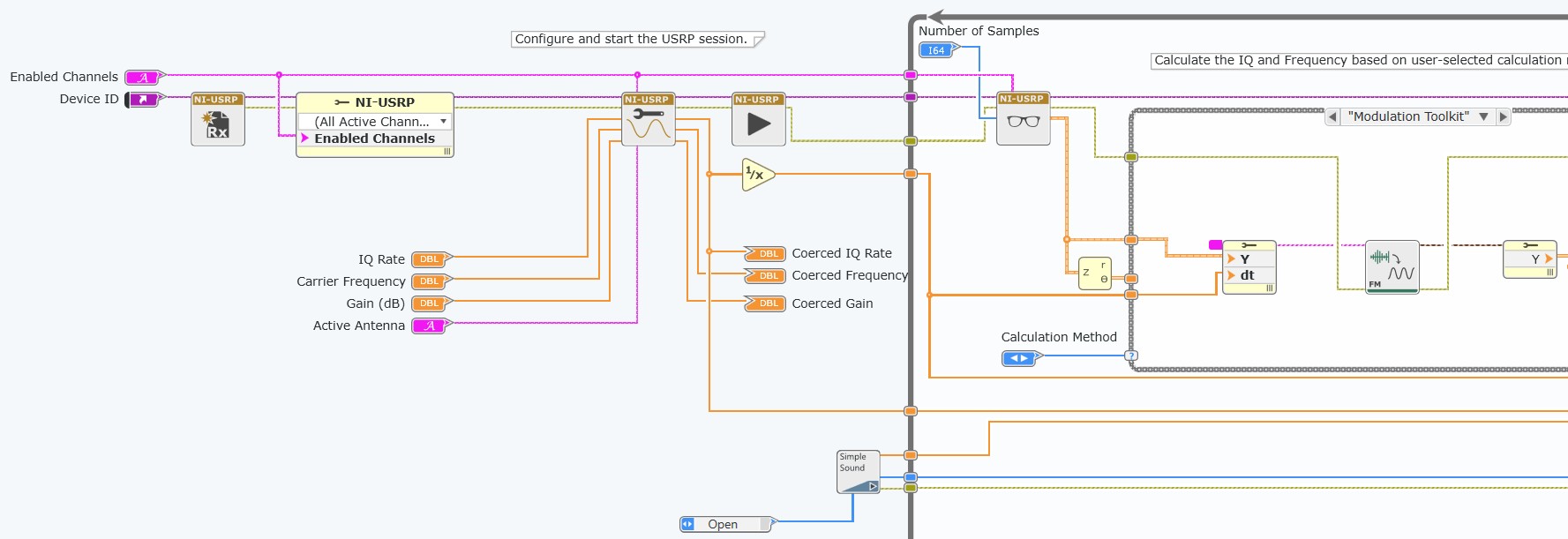

LabVIEWは、通信アルゴリズムの開発と実装に最適なグラフィカルデータフロープログラミング環境です。最も基本的なレベルでは、LabVIEWはNI-USRPドライバを使用してUSRPハードウェア構成を指定し、正しくフォーマットされたベースバンドI/Qデータを送受信します。

図8:USRPドライバAPIを使用したLabVIEWブロックダイアグラムのスクリーンショット

次のステップ

登録商標Linux®は、全世界における商標保持者Linus Torvalds氏から排他的ライセンスを受けているLMI (Linux Mark Institute) からの許諾により使用しています。MATLAB®はThe MathWorks, Inc.社の登録商標です。