Options de compilation de NI LabVIEW FPGA

Aperçu

Contenu

- Les FPGA deviennent plus difficiles (pas plus faciles) à compiler

- Présentation du système de compilation LabVIEW FPGA

- Options prêtes à l’emploi du système de compilation LabVIEW FPGA

- Transférer la compilation FPGA

- Réduire le temps de compilation avec Linux

- Étapes suivantes

Les FPGA deviennent plus difficiles (pas plus faciles) à compiler

Le compilateur FPGA n’est pas un grand algorithme monolithique. Il s’agit plutôt d’une série de grands algorithmes complexes. Le problème informatique est de faire passer votre conception par un flux qui génère une structure optimisée sur une puce dotée de millions d’éléments de traitement configurables de n’importe quelle façon. Le compilateur utilise une synthèse pour créer un système de connexions logiques entre les éléments de traitement. Le compilateur mappe, place et route ensuite dans un processus itératif pour trouver la meilleure solution et connecte tout sur la puce physique tout en essayant de respecter les contraintes de l’utilisateur. Comme vous pouvez l’imaginer, les mathématiques derrière la recherche d’une solution globale et optimisée à un problème qui a des possibilités infinies sont non triviales. Par conséquent, les compilations FPGA peuvent prendre des heures, voire plus, avec du silicium de plus haute densité.

Pour améliorer la durée des compilations, vous pouvez transférer la compilation à une machine Windows dédiée haut de gamme ayant beaucoup de RAM ainsi qu’un bon processeur. Pour réduire davantage le temps de compilation, vous pouvez installer les outils de compilation Xilinx sur un système Linux afin de tirer parti de l’optimisation des performances des outils de compilation. NI a conçu le système de compilation LabVIEW FPGA pour vous permettre de configurer facilement l’une ou l’autre de ces options au sein de votre propre entreprise. Vous pouvez également cibler vos compilations sur des ordinateurs haut de gamme à maintenance zéro dans le cloud.

Présentation du système de compilation LabVIEW FPGA

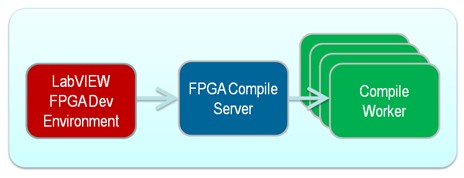

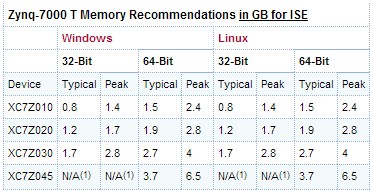

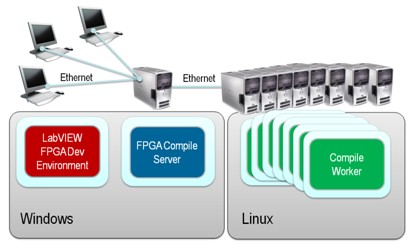

NI a conçu le système de compilation LabVIEW PGA avec trois composants logiciels fondamentaux, ce qui offre une solution de compilation modulaire et évolutive. Le système de compilation est divisé en trois parties : l’ordinateur de développement, le serveur de compilation et n’importe quel nombre de machines de compilation.

LabVIEW FPGA Module Development Environment – L’environnement de développement LabVIEW que vous connaissez est l’endroit pour créer votre application. Cliquez sur Exécuter sur votre VI FPGA termine l’étape de génération de fichiers intermédiaires (voir Processus de compilation LabVIEW FPGA pour en savoir plus). Après la génération, l’ordinateur de développement envoie les fichiers intermédiaires via la communication des services Web au serveur de compilation.

Serveur de compilation — Le serveur de compilation accepte les tâches de compilation d’un ou de plusieurs systèmes de développement LabVIEW FPGA et recherche les machines de compilation disponibles pour exploiter les tâches de compilation. Si aucune machine de compilation n’est disponible, le serveur de compilation maintient la tâche de compilation dans une file d’attente jusqu’à ce qu’une machine de compilation soit disponible.

Machine de compilation — Les outils de compilation Xilinx sont installés pour la synthèse, le mappage, le placement et le routage de la conception FPGA. Avec ces outils, une machine de compilation implémente la conception et génère un fichier bitfile. La machine de compilation renvoie le fichier bitfile au serveur de compilation qui, à son tour, le renvoie à l’ordinateur de développement.

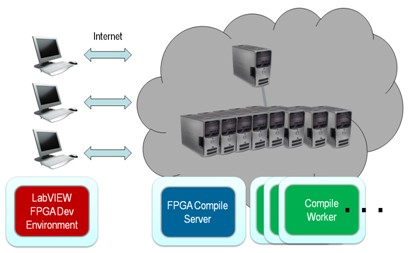

Figure 1 : L’architecture du système de compilation LabVIEW FPGA comprend trois parties : l’ordinateur de développement, le serveur de compilation et la ou les machines de compilation.

L’avantage de cette architecture de système de compilation est qu’elle prend en charge plusieurs machines de compilation ainsi que l’exploitation automatique des tâches de compilation. Le serveur de compilation traite les files d’attente et la distribution. De plus, il est tolérant aux machines de compilation qui passent d’un état hors ligne et en ligne. En fait, si une machine de compilation est abandonnée pendant une tâche de compilation, le serveur de compilation le détecte et envoie la compilation à une autre machine de compilation disponible. Bien que la tâche de compilation doive recommencer à zéro, elle se termine sans aucune action de votre part. Étant donné que les lignes de communication entre l’environnement de développement et le serveur de compilation sont toutes des services Web robustes, le système de compilation est également tolérant aux pannes pour un certain nombre de problèmes liés au développement, comme le redémarrage d’un ordinateur de développement.

Options prêtes à l’emploi du système de compilation LabVIEW FPGA

Prêt à l’emploi, le LabVIEW FPGA Module inclut deux options de système de compilation. Vous pouvez compiler directement sur votre ordinateur de développement ou transférer la compilation vers une seule machine de compilation dédiée distante.

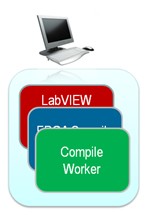

Par défaut, LabVIEW installe avec LabVIEW FPGA Module un serveur de compilation et une machine de compilation sur l’ordinateur de développement. Si vous utilisez le module LabVIEW 2009 FPGA ou une version antérieure, cette configuration se comporte exactement de la même manière, la compilation étant implémentée sur l’ordinateur de développement. Pour le serveur de compilation, c’est comme si la compilation était sur un ordinateur séparé appelé « localhost », car le système est conçu de toutes pièces pour supporter la compilation distribuée.

Figure 2 : Par défaut, LabVIEW FPGA Module installe le serveur de compilation et la machine de compilation sur l’ordinateur de développement et exécute la tâche de compilation en utilisant les ressources de l’ordinateur de développement.

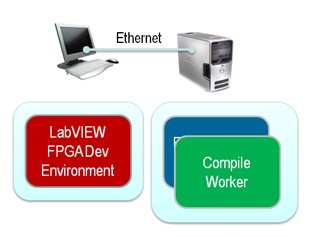

`Pour configurer une structure de système de compilation plus sophistiquée, vous pouvez installer le serveur et une machine de compilation sur un autre ordinateur. Pour configurer le serveur de compilation distant, installez uniquement les outils de compilation Xilinx. Pour obtenir des instructions détaillées sur ce processus, reportez-vous à l’article Installation et activation de LabVIEW FPGA Compile Server sur un ordinateur distant.

Figure 3 : LabVIEW FPGA prend en charge un serveur de compilation simple, monoposte et déchargé sans complément logiciel.

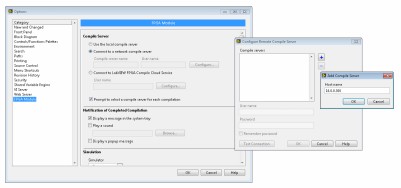

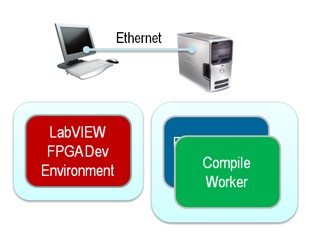

Une fois les outils de compilation Xilinx installés sur l’ordinateur distant, vous pouvez diriger la machine de développement vers ce nouveau serveur de compilation en sélectionnant Se connecter à un serveur de compilation réseau lorsque vous cliquez sur le bouton Exécuter. Vous pouvez aussi définir cette option de compilation à partir de la page Outil > Options > Module FPGA.

Figure 4 : Ciblez la machine de compilation FPGA distante en sélectionnant l’option de système de compilation et en spécifiant où se trouve le serveur.

Transférer la compilation FPGA

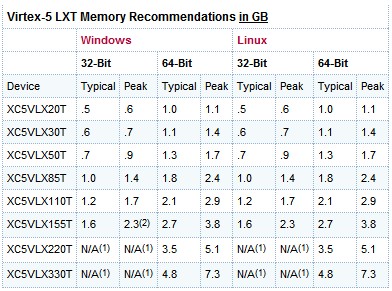

La compilation FPGA devient de plus en plus complexe sur le plan informatique et, par conséquent, plus longue, à mesure que les développeurs utilisent une technologie FPGA plus sophistiquée. Pour économiser les ressources sur votre ordinateur de développement, l’architecture du système de compilation LabVIEW FPGA inclut des options pour transférer la compilation sur des ordinateurs dédiés. Il doit s’agir d’ordinateurs haut de gamme dotés de bons processeurs et de niveaux élevés de RAM. Le tableau n°1 montre le minimum de RAM nécessaire pour différents FPGA Xilinx Virtex-5.

Tableau 1 : Suivez ces recommandations pour les FPGA Xilinx Virtex-5 et Zynq-700. Source Recommandations de mémoire Xilinx à l’aide de la suite ISE Design)

Les performances d’une tâche de compilation sont particulièrement affectées lorsque le processus manque de mémoire système et doit paginer le disque dur ou, dans certains cas, quitter. Suivez les recommandations du tableau 1 pour obtenir les meilleurs résultats. Pour un serveur 32 bits, vous devriez avoir 4 Go de RAM et seulement les outils de compilation Xilinx installés. Vous pouvez activer l’extension de mémoire de Windows à 3 Go pour maximiser la quantité de RAM que le système d’exploitation peut allouer à la compilation. Comme le montre le tableau, les systèmes 64 bits devraient avoir davantage de RAM. Ces systèmes sont bien sûr capables d’adresser beaucoup plus que 4 Go de RAM, et il est préférable d’installer le plus de RAM possible, jusqu’à 16 Go environ.

Transférer à un seul ordinateur

Vous pouvez utiliser LabVIEW FPGA Module pour installer le serveur de compilation et la machine de compilation sur un ordinateur et une compilation de cibles distincts. Pour ce faire, suivez les étapes de l’article Installer et activer le serveur de compilation LabVIEW FPGA sur un ordinateur distant.

Figure 5 : Un serveur de compilation simple, monoposte et déchargé est pris en charge par LabVIEW FPGA Module sans complément logiciel.

Transférer à une ferme de compilation

Avec FPGA Compile Farm Server, vous pouvez créer une ferme de compilation sur site qui inclut plusieurs machines de compilation pouvant être ciblées par plusieurs développeurs. Remarque : Pour le module LabVIEW FPGA 2013 et les versions antérieures, utilisez le NI LabVIEW FPGA Compile Farm Toolkit.

Le serveur de compilation est responsable de la distribution des tâches de compilation à toutes les machines de compilation disponibles. Les compilations s’exécutent en parallèle car il y a plusieurs machines de compilation. S’il n’y a pas de machines de compilation disponibles, le serveur de compilation place les requêtes dans une file d’attente, en utilisant des FIFO, et ferme les requêtes lorsqu’une machine de compilation devient disponible.

Figure 6 : Architecture de ferme de compilation sur site avec un serveur de compilation et plusieurs machines de compilation.

Transférer vers un serveur Compile Cloud en ligne

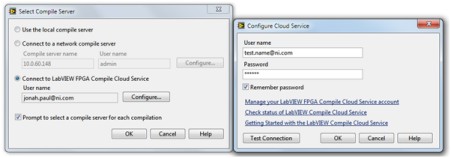

La dernière option de compilation FPGA utilise les serveurs de compilation et les machines de compilation que NI met à disposition en ligne dans le cloud. Pour faciliter l’utilisation, NI a ajouté des crochets directement depuis LabVIEW FPGA pour entrer un login, et sans installation supplémentaire, vous pouvez décharger vos compilations sur le cloud. Par rapport à un ordinateur de bureau Windows standard, les VI FPGA connaissent une réduction substantielle des temps de compilation car LabVIEW FPGA Compile Cloud Service exécute les outils de compilation Xilinx sous Linux avec les derniers ordinateurs haut de gamme dédiés à haute RAM. Lorsque vous compilez dans le cloud, vous pouvez aussi compiler de nombreux VI en parallèle.

Pour cibler le service cloud, utilisez la boîte de dialogue du serveur de compilation LabVIEW FPGA, sélectionnez le service cloud en ligne et vous entrez votre nom d’utilisateur ainsi que votre mot de passe.

Figure 7 : Connectez-vous au cloud via LabVIEW pour réduire le temps de compilation et décharger les compilations.

Une fois le cloud de compilation configuré, le service effectue la compilation sur le cloud plutôt que sur votre ordinateur local ou votre ferme de compilation locale. La connexion utilise les dernières mesures de sécurité de l’industrie informatique, qui sont similaires à celles utilisées par d’autres services Internet, tels que les services bancaires.

Figure 8 : Architecture cloud pour le déchargement des compilations.

Réduire le temps de compilation avec Linux

NI investit dans le support de la machine de compilation FPGA sous Linux. Selon la complexité et la logique de votre VI FPGA, vous pouvez vous attendre à ce que la machine de compilation Linux réduise les temps de compilation d’environ 20 à 50 % par rapport à une machine de compilation Windows. À l’origine, Xilinx avait conçu et optimisé les outils de compilation pour le système d’exploitation Linux, ce qui explique cette réduction substantielle du temps de compilation.

Figure 9 : LabVIEW 2012 FPGA et les versions ultérieures supportent l’installation de l’outil de compilation Xilinx sur les machines Linux, ce qui réduit les temps de compilation.

>> Explorez les avantages de l’utilisation de la machine de compilation Linux FPGA dans le cloud.

>> En savoir plus sur la façon de développer votre propre machine de compilation Linux FPGA.

Étapes suivantes

Le système de compilation FPGA LabVIEW offre une grande flexibilité grâce à l’architecture du serveur de compilation et de l’assistant de compilation qui permet de décharger votre ordinateur de développement LabVIEW du processus de compilation FPGA, très gourmand en ressources processeur. Le système de compilation LabVIEW FPGA réduit également les temps de compilation en utilisant une machine de compilation basée sur Linux. Une fois que vous avez sélectionné l’option de compilation FPGA appropriée pour votre équipe, suivez les liens ci-dessous pour en savoir plus sur sa configuration.