États numériques, niveaux de tension et familles logiques

Aperçu

Familiarisez-vous avec les états numériques, les niveaux logiques de tension et les familles de niveaux logiques pour les signaux numériques. Ce tutoriel fait partie de la série Principes fondamentaux des instruments.

Contenu

États numériques

Dans les périphériques numériques, il n’existe que deux états : activé et désactivé. En utilisant uniquement ces deux états, les périphériques peuvent communiquer un grand nombre de données et contrôler divers autres périphériques. En binaire, ces états sont représentés par un 1 ou un 0. Le 1 binaire est généralement considéré comme un niveau logique haut et 0 est un niveau logique bas.

Niveaux de tension

Cependant, les périphériques numériques sont souvent pilotés par des périphériques analogiques présentant un nombre infini d’états. Comment transformer un nombre infini d’états en seulement deux ? La réponse consiste à créer des niveaux logiques de tension, qui définissent la tension permettant de représenter une logique haute ou une logique basse.

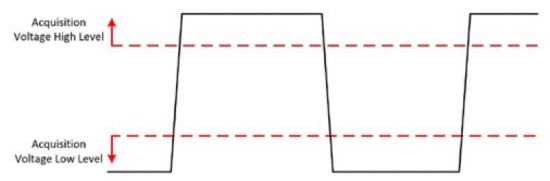

Figure 1 : Les niveaux de tension définissent la tension analogique qui représente un niveau logique haut ou bas.

Un système peut définir les niveaux logiques de tension sur n’importe quelle valeur, mais de nombreux circuits représentent une logique haute de +5 V ou +3,3 V à la masse et une logique basse comme masse ou 0 V. Ce type de système est appelé système positif ou actif haut. Il décrit la manière dont la broche est activée. Pour une broche active haute, il faut la raccorder à votre ligne haute tension.

Un système négatif ou actif bas est l’inverse. La tension la plus élevée représente un niveau logique bas et la tension la plus basse correspond à un niveau logique haut. Pour une broche active basse, vous devez ralentir cette broche en la raccordant à la masse. Les fiches techniques indiquent souvent qu’une broche est active basse en plaçant une ligne au-dessus du nom de la broche, comme EN.

Bien qu’un haut et un bas soient spécifiés, dans la plupart des systèmes, il existe une plage plus pratique. Par exemple, un niveau logique haut peut être n’importe quelle valeur entre 2 V et 5 V et un niveau bas n’importe quelle valeur entre 0 V et 1 V. Les tensions en dehors de ces plages sont considérées comme non valides et ne se produisent qu’en cas de défaillance ou de transition du niveau logique.

États Z et X

Bien qu’un signal numérique ne puisse avoir que deux états (activé et désactivé), vous pouvez utiliser des états supplémentaires afin de faciliter l’acquisition et la génération de signaux numériques. Avec la logique à trois états, il existe une troisième condition possible : un état à haute impédance où la sortie est déconnectée de la ligne. Cet état n’est ni haut ni bas, mais flottant ou à haute impédance. Il porte la désignation Z et est souvent utilisé comme ligne d’activation.

L’utilisation la plus courante de l’état Z concerne le test d’une ou de plusieurs lignes numériques pouvant être pilotées par plusieurs émetteurs. Le port de données d’une puce mémoire en est un bon exemple. Lorsque l’ordinateur écrit dans le périphérique de mémoire, il doit diriger les données à écrire dans la puce mémoire sur les broches de données du périphérique de mémoire (soit 0, soit 1). Plus tard, lorsque le processeur de l’ordinateur souhaite lire le contenu de la mémoire, le périphérique de mémoire doit renvoyer la valeur des données précédemment stockée au processeur de l’ordinateur (généralement un état Z sur les broches de données).

Un quatrième état que vous pouvez rencontrer est l’état de maintien qui est désigné par un X. Lors de la génération de signaux numériques, il peut être utile que le périphérique maintienne simplement la voie à son état actuel, quel que soit l’état dans lequel elle se trouve. Cet état est utile lors de la définition des états initiaux ou inactifs.

Lorsque vous acquérez des données, l’état X a une désignation différente de l’indifférence. Cet état est utile lorsque vous comparez un signal numérique acquis à un signal attendu. Par exemple, sur un signal, il est possible que seules les quatre premières valeurs d’un signal à 10 valeurs sont importantes. Vous pouvez utiliser l’état X pour les six dernières valeurs et ainsi comparer uniquement les quatre premières.

| État | Désignation |

|---|---|

| 0 | Niveau logique bas |

| 1 | Niveau logique haut |

| Z | Haute impédance |

| X | État de maintien ou d’indifférence |

Tableau 1 : Un signal numérique peut uniquement présenter un état haut ou bas. Cependant, les états Z et X peuvent être utiles dans les applications qui génèrent ou acquièrent des signaux numériques.

Familles logiques

Les familles logiques standardisées facilitent le travail avec les circuits et les composants. Elles fournissent un niveau de tension standardisé qui constitue un niveau logique haut ou logique bas. Tous les circuits d’une famille logique sont compatibles avec les autres circuits de cette même famille car ils partagent les mêmes caractéristiques.

Familles logiques asymétriques

Les familles logiques asymétriques spécifient les niveaux de tension par rapport à la masse. Les quatre niveaux sont définis comme suit :

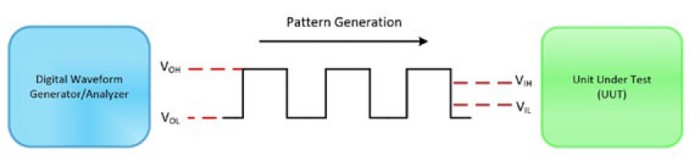

- VOH (tension de haut niveau de sortie) : également connu sous le nom de tension de génération de haut niveau. Lorsqu’il est configuré pour la génération active, il s’agit de la tension produite par le périphérique lorsqu’il génère une logique haute. Lorsqu’il est configuré pour la génération de collecteur ouvert, cela équivaut à définir la voie de données à un état de haute impédance.

- VOL (tension de bas niveau de sortie) : également connu sous le nom de tension de génération bas niveau. Il s’agit de la tension produite par le périphérique lorsqu’il génère un niveau logique bas.

- VIH (tension d’entrée de haut niveau) : également connu sous le nom de tension d’acquisition de haut niveau. Il s’agit du niveau de tension qu’il est nécessaire d’envoyer au périphérique pour qu’il puisse lire un niveau logique haut.

- VIL (tension de bas niveau d’entrée) : également connu sous le nom de tension d’acquisition de bas niveau. Il s’agit du niveau de tension qu’il est nécessaire d’envoyer au périphérique pour qu’il puisse lire un niveau logique bas.

Figure 2 : Des niveaux logiques asymétriques sont spécifiés pour la sortie et l’entrée.

Pour communiquer avec un périphérique avec exactitude, assurez-vous de configurer le périphérique numérique de manière à ce que les conditions suivantes soient remplies :

- VOH ≥ DUT VIH

- VOL ≤ DUT VIL

- VIH ≤ DUT VOH

- VIL ≥ DUT VOL

- VIH > VIL

Il existe généralement une marge entre la tension de sortie d’un périphérique et l’entrée d’un autre. C’est ce que l’on appelle la marge de bruit ou le niveau d’immunité au bruit (NIM). Si vous vous trouvez dans un environnement bruité et que vous rencontrez des difficultés avec des bits de données incorrects, envisagez d’augmenter cette valeur.

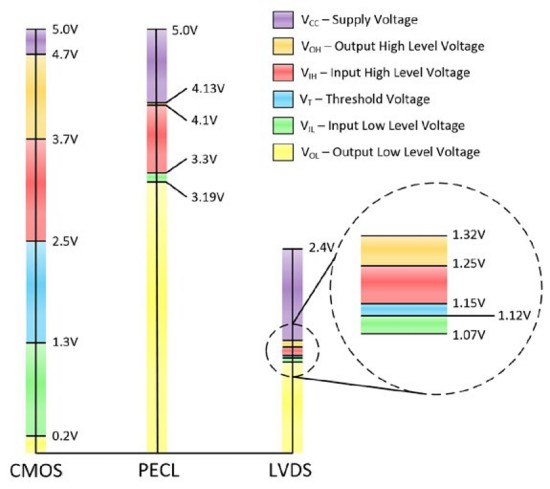

Il existe plusieurs familles logiques asymétriques. La logique transistor-transistor (TTL) est très courante pour les circuits intégrés. Elle est utilisée dans de nombreuses applications telles que les ordinateurs, l’électronique grand public et les équipements de test. Les circuits construits à partir de transistors bipolaires permettent de commuter et de maintenir des états logiques. Une TTL doit également répondre à des spécifications de courant et à des temps de montée/descente spécifiques. En savoir plus dans Quelle est la définition d’un signal compatible avec la logique TTL ?.

Figure 3 : Niveaux de tension TTL standard de 5 V

Les CMOS sont une autre famille de circuits intégrés courants. Ces périphériques présentent une immunité au bruit élevée, nécessitent une consommation d’énergie inférieure et ont une tension de base plus faible. La plupart des niveaux de tension sont similaires à ceux des périphériques TTL pour une meilleure compatibilité. Cela facilite la commutation d’un périphérique TTL vers un CMOS, mais il peut être plus difficile de faire le contraire. Une tension trop élevée vers un CMOS peut endommager la puce. Dans ce cas, il est possible d’utiliser un diviseur de tension pour réduire la tension.

Figure 4 : Niveaux de tension CMOS standard

Familles logiques différentielles

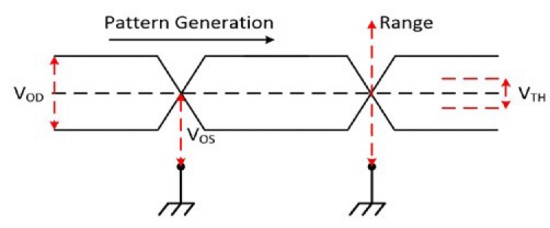

Les familles logiques asymétriques utilisent un niveau de tension défini par rapport à la masse. Les familles logiques différentielles, quant à elles, utilisent la différence entre deux valeurs et non une référence à la masse. Afin que le signal différentiel soit interprété comme un signal logique bas, le signal doit être inférieur à son signal complémentaire de plus d’une valeur spécifique connue sous le nom de valeur de seuil (VTH). Comme les signaux sont référencés et transmis ensemble, vous pouvez obtenir une meilleure immunité au bruit dans vos signaux par rapport à des familles logiques asymétriques. Les niveaux de tension des familles logiques différentielles sont généralement spécifiés à partir d’une tension différentielle plutôt qu’absolue. Les quatre niveaux sont définis comme suit :

- VOD (tension différentielle de sortie) : différence de tension entre les signaux.

- VOS (tension d’offset) : mode commun du signal différentiel. Considérez cette valeur comme la moyenne des deux signaux. Il s’agit d’une référence à la masse.

- VTH (tension de seuil) : différence de tension nécessaire pour que le périphérique enregistre un état logique valide.

- VRANGE (plage de tension d’entrée) : tension absolue référencée à partir de la masse autorisée par le périphérique.

Résumé

- Un niveau logique de tension définit la tension représentant un niveau logique haut ou bas.

- De nombreux circuits représentent une logique haute de +5 V ou +3,3 V à la masse et une logique basse comme masse ou 0 V. Ce type de système est appelé positif ou actif haut.

- Dans la logique à trois états, l’état Z est un état à haute impédance, souvent utilisé comme ligne d’activation.

- Dans la génération numérique, l’état X maintient le niveau logique actuel. En acquisition numérique, cela indique un état indifférent.

- Les familles logiques fournissent un niveau de tension standardisé qui constitue un niveau logique haut ou bas.

- TTL est basée sur VCC = 5 V.

- CMOS est basée sur VCC = 3,3 V

- Les familles logiques différentielles utilisent la différence entre deux valeurs et non une référence à la masse.

- LVDS est une méthode différentielle à faible bruit, faible puissance et faible amplitude avec VCC = 3,3 V.

- Les circuits LVPECL sont un type de circuit ECL qui nécessite une paire de lignes de signaux pour chaque voie (VCC = 3 ou 3,3 V).