Opciones de compilación de NI LabVIEW FPGA

Información general

Contenido

- Los FPGAs son cada vez más difíciles (no más fáciles) de compilar

- Descripción general del sistema de compilación LabVIEW FPGA

- Opciones listas para usar del sistema de compilación LabVIEW FPGA

- Descargue la compilación de FPGA

- Reduzca el tiempo de compilación con Linux

- Próximos pasos

Los FPGAs son cada vez más difíciles (no más fáciles) de compilar

El compilador FPGA no es un gran algoritmo monolítico. En cambio, es una colección de algoritmos grandes y complejos. El desafío de cómputo lleva su diseño a través de un flujo que genera un diseño optimizado en un chip con millones de elementos de procesamiento que puede configurar de cualquier manera. El compilador usa síntesis para crear un sistema de conexiones lógicas entre los elementos de procesamiento. Luego, el compilador mapea, coloca y enruta en un proceso iterativo para encontrar la mejor solución y conecta todo en el chip físico mientras intenta mantenerse dentro de las restricciones del usuario. Como puede imaginar, las matemáticas detrás de encontrar una solución optimizada globalmente para un problema que tiene infinitas posibilidades no son triviales. Como resultado, las compilaciones de FPGA pueden tardar horas o incluso más con silicio de mayor densidad.

Para mejorar el tiempo de compilación, puede descargar su compilación a una máquina Windows separada, de alta gama y dedicada con mucha RAM y un buen procesador. Para reducir aún más el tiempo de compilación, usted puede instalar las herramientas de compilación Xilinx en un sistema Linux para aprovechar la optimización del rendimiento de la herramienta de compilación. NI diseñó el sistema de compilación LabVIEW FPGA para que le resulte más fácil configurar cualquiera de estas opciones dentro de su propia compañía, o incluso dirigir sus compilaciones a PCs de alta calidad sin mantenimiento en la nube.

Descripción general del sistema de compilación LabVIEW FPGA

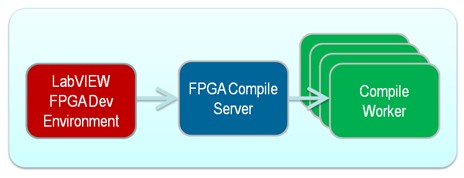

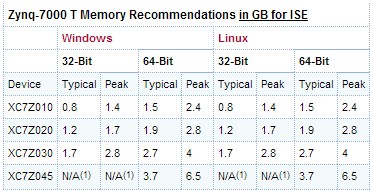

NI diseñó el sistema de compilación LabVIEW FPGA con tres componentes de software fundamentales, lo que da como resultado una solución de compilación modular y escalable. El sistema de compilación se divide en tres partes: la PC de desarrollo, el servidor de compilación y cualquier cantidad de trabajadores de compilación.

Entorno de desarrollo del LabVIEW FPGA Module —El entorno de desarrollo de LabVIEW con el que está familiarizado es donde crea su aplicación. Al hacer clic en Run en su VI de FPGA, se completa el paso de generación de archivos intermedios (consulte Proceso de compilación de LabVIEW FPGA para obtener más información). Después de la generación, la PC de desarrollo envía los archivos intermedios a través de la comunicación de servicios web al servidor de compilación.

Servidor de compilación—El servidor de compilación acepta trabajos de compilación de uno o varios sistemas de desarrollo de LabVIEW FPGA y busca trabajadores de compilación disponibles para asignar trabajos de compilación. Si no hay trabajadores de compilación disponibles, el servidor de compilación retiene el trabajo de compilación en una cola hasta que un trabajador de compilación esté disponible.

Compile Worker—El compilador tiene las herramientas de compilación Xilinx instaladas para la síntesis, mapeo, colocación y enrutado del diseño de FPGA. Con estas herramientas, un trabajador de compilación implementa el diseño y genera un archivo de bits. El trabajador de compilación envía el archivo de bits al servidor de compilación, que, a su vez, envía el archivo de bits a la PC de desarrollo.

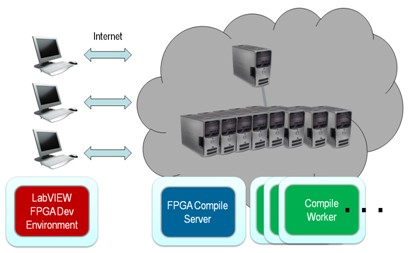

Figura 1: La arquitectura del sistema de compilación LabVIEW FPGA incluye tres partes: la PC de desarrollo, el servidor de compilación y los trabajadores de compilación.

El beneficio de esta arquitectura del sistema de compilación es que soporta múltiples trabajadores de compilación y la realización automática de trabajos de compilación. El servidor de compilación maneja la cola y la realización, y es tolerante a fallas para compilar los trabajadores que entran y salen. De hecho, si un trabajador de compilación se desconecta durante un trabajo de compilación, el servidor de compilación lo detecta y lleva la compilación a otro trabajador de compilación disponible. Aunque el trabajo de compilación tiene que comenzar de nuevo, finaliza sin ninguna acción de su parte. Debido a que las líneas de comunicación entre el entorno de desarrollo y el servidor de compilación son servicios web robustos, el sistema de compilación también es tolerante a fallas para una serie de problemas del lado del desarrollo, como un reinicio de la PC de desarrollo.

Opciones listas para usar del sistema de compilación LabVIEW FPGA

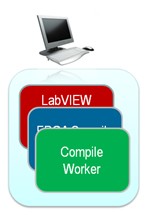

Listo para usar, el LabVIEW FPGA Module incluye dos opciones de sistema de compilación. Puede compilar directamente en su PC de desarrollo o transferir la compilación a una sola máquina de compilación dedicada y remota.

De forma predeterminada, LabVIEW instala un servidor de compilación y un trabajador de compilación en la PC de desarrollo junto con el LabVIEW FPGA Module. Si usa el LabVIEW 2009 FPGA Module o anterior, esta configuración se comporta exactamente de la misma manera, con la compilación implementada en la PC de desarrollo. Para el servidor de compilación, es como si la compilación estuviera en una PC separada llamada "localhost", porque el sistema está diseñado desde cero para soportar la compilación distribuida.

Figura 2: De manera predeterminada, el LabVIEW FPGA Module instala tanto el servidor de compilación como el trabajador de compilación en la PC de desarrollo y ejecuta el trabajo de compilación utilizando los recursos en la PC de desarrollo.

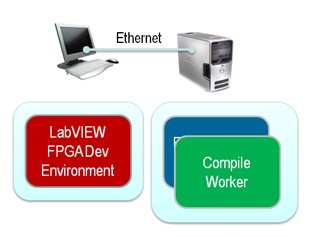

Si desea configurar una estructura de sistema de compilación más sofisticada, puede instalar el servidor de compilación y un trabajador de compilación en otra PC. Para configurar el servidor de compilación remoto, instale únicamente las herramientas de compilación Xilinx. Para obtener instrucciones paso a paso sobre este proceso, consulte el artículo Instalar y activar el servidor de compilación LabVIEW FPGA en una PC remota .

Figura 3: LabVIEW FPGA soporta un servidor de compilación simple, descargado y de una sola máquina sin ningún complemento.

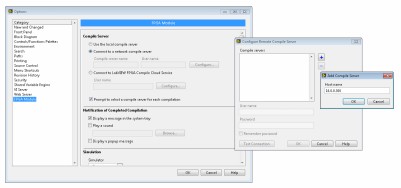

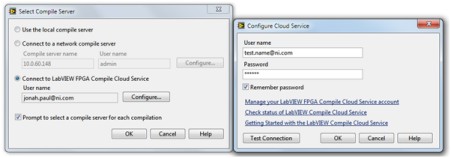

Una vez que instale las herramientas de compilación Xilinx en la PC remota, puede apuntar la máquina de desarrollo a este nuevo servidor de compilación seleccionando Connect to a network compile server cuando hace clic en el botón Run . Alternativamente, usted puede establecer esta opción de compilación desde la página Tools»Options»FPGA Module .

Figura 4: Apunte a la máquina de compilación FPGA remota seleccionando la opción del sistema de compilación y especificando dónde reside el servidor.

Descargue la compilación de FPGA

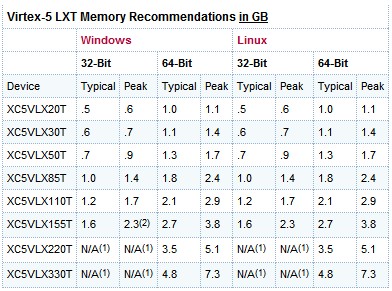

La compilación de FPGA se vuelve más compleja desde el punto de vista computacional y, como resultado, más larga, a medida que los desarrolladores utilizan tecnología FPGA más sofisticada. Para conservar recursos en su PC de desarrollo, la arquitectura del sistema de compilación LabVIEW FPGA incluye opciones para descargar la compilación a PCs dedicadas. Estas deben ser computadoras de alta gama con buenos procesadores y altos niveles de RAM. La Tabla 1 muestra las necesidades mínimas de RAM para varios FPGAs Xilinx Virtex-5.

Tabla 1: Siga estas pautas de RAM recomendadas para los FPGAs Xilinx Virtex-5 y Zynq-700. (Fuente: Recomendaciones de memoria Xilinx usando ISE Design Suite)

El rendimiento de un trabajo de compilación se ve afectado de manera negativa cuando el proceso carece de memoria del sistema y tiene que buscar en el disco duro o, en algunos casos, cerrarse. Siga las recomendaciones de la Tabla 1 para obtener los mejores resultados. Para un servidor de 32 bits, debe tener 4 GB de RAM y solo las herramientas de compilación Xilinx instaladas. Puede usar el conmutador de Windows de 3 GB para maximizar la cantidad de RAM que el sistema operativo puede asignar a la compilación. Como puede ver en la tabla, los sistemas de 64 bits deben tener más RAM instalada. Por supuesto, esos sistemas pueden manejar mucho más de 4 GB de RAM, por lo que, en este caso, cuanto más, mejor, hasta 16 GB.

Descargar a una sola PC

Puede usar el LabVIEW FPGA Module para instalar el servidor de compilación y el trabajador de compilación en una PC separada y compilación de destino. Para hacer esto, siga los pasos en el artículo Instalar y activar el servidor de compilación LabVIEW FPGA en una PC remota .

Figura 5: Un servidor de compilación simple, descargado y de una sola máquina es compatible con el LabVIEW FPGA Module sin ningún complemento.

Descargar a una granja de compilación

Con el Servidor de granja de compilación FPGA, usted puede crear una granja de compilación en sitio que incluya múltiples trabajadores de compilación que pueden ser el objetivo de múltiples desarrolladores. Nota: Con el LabVIEW 2013 FPGA Module y versiones anteriores, use el NI LabVIEW FPGA Compile Farm Toolkit.

El servidor de compilación es responsable de asignar trabajos de compilación a todos los trabajadores de compilación disponibles. Las compilaciones se ejecutan en paralelo porque hay varios trabajadores de compilación. Si no hay trabajadores de compilación disponibles, el servidor de compilación pone en cola las solicitudes, utilizando FIFOs, y las asigna cuando un trabajador de compilación está disponible.

Figura 6: Arquitectura de granja de compilación en sitio con un servidor de compilación y varios trabajadores de compilación.

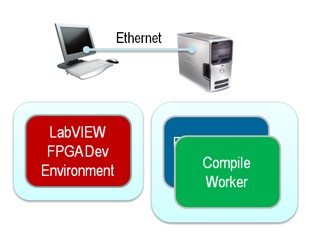

Descargar a un servidor de compilación en la nube en línea

La última opción de compilación de FPGA utiliza los servidores de compilación y los trabajadores de compilación que NI pone a disposición en línea en la nube. Para facilitar el uso, NI ha agregado enlaces directamente desde LabVIEW FPGA para ingresar un inicio de sesión, y sin instalación adicional, puede descargar sus compilaciones a la nube. En comparación con un escritorio estándar de Windows, los VIs de FPGA experimentan una reducción sustancial en los tiempos de compilación porque el LabVIEW FPGA Compile Cloud Service ejecuta las herramientas de compilación Xilinx en Linux con las últimas PCs dedicadas de alta calidad de RAM alta. Cuando compila en la nube, también puede compilar muchos VIs en paralelo.

Para apuntar al servicio en la nube, use el cuadro de diálogo para el servidor de compilación LabVIEW FPGA, seleccione el servicio en la nube en línea e ingrese su nombre de usuario y contraseña.

Figura 7: Conéctese a la nube a través de LabVIEW para reducir el tiempo de compilación y descargar compilaciones.

Una vez que ha configurado la nube de compilación, el servicio se compila en la nube en lugar de en su PC local o granja de compilación local. La conexión utiliza las últimas medidas de seguridad de la industria de TI, que son similares a las utilizadas por otros servicios de Internet, como la banca.

Figura 8: Arquitectura en la nube para descargar compilaciones.

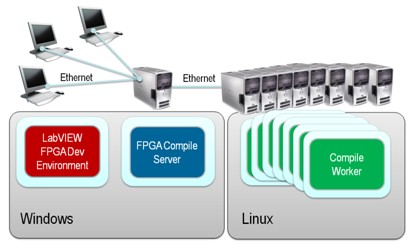

Reduzca el tiempo de compilación con Linux

NI invierte en soportar el trabajador de compilación FPGA en el SO Linux. Dependiendo de la complejidad y la lógica de su VI de FPGA, puede esperar que el trabajador de compilación de Linux reduzca los tiempos de compilación en aproximadamente un 20 a 50%, en comparación con un trabajador de compilación de Windows. Xilinx diseñó y optimizó originalmente las herramientas de compilación para el sistema operativo Linux, lo que explica esta reducción sustancial en el tiempo de compilación.

Figura 9. LabVIEW 2012 FPGA y versiones posteriores soportan la instalación de la herramienta de compilación Xilinx en máquinas Linux, lo que resulta en tiempos de compilación reducidos.

>> Explore los beneficios de usar el trabajador de compilación FPGA de Linux en la nube.

>> Aprenda más detalles sobre cómo mejorar su propio trabajador de compilación de FPGA de Linux.

Próximos pasos

El sistema de compilación LabVIEW FPGA proporciona flexibilidad a través del servidor de compilación y la arquitectura del trabajador de compilación para descargar el proceso de compilación FPGA que requiere un uso intensivo del procesador de su PC de desarrollo con LabVIEW . El sistema de compilación LabVIEW FPGA también reduce los tiempos de compilación al usar un trabajador de compilación basado en Linux. Una vez que haya seleccionado la opción de compilación FPGA adecuada para su equipo, siga los enlaces a continuación para obtener más información sobre cómo configurarla.