NI Multifunction RIO Frequently Asked Questions (FAQ)

Contents

- What is RIO technology?

- What Are the New Multifunction RIO devices?

- How do the new R Series devices compare with previous-generation R Series devices?

- Comparison of FPGAs on NI FPGA Products

- How do I decide which FPGA is right for my application?

- Will my Virtex-II program work on a Virtex-5 or Kintex-7?

- Do I need to know VHDL to use LabVIEW FPGA?

- Do I need the LabVIEW FPGA Module to program R Series devices?

- Can I program my R Series device in C/C++?

- How is R Series different from other data acquisition families?

- Can I program R Series devices with NI-DAQmx, NI-DAQmx Base, or the NI Measurement Hardware DDK?

- What are the R Series onboard processing capabilities?

- Can I achieve simultaneous analog input/output with an R Series device?

- Additional Resources

What is RIO technology?

With NI reconfigurable I/O (RIO) technology, you can define your own custom measurement hardware circuitry using reconfigurable FPGA chips and NI LabVIEW graphical development tools. R Series multifunction RIO devices offer the best combination of value and performance by integrating this FPGA technology with eight analog inputs, eight analog outputs, and up to 96 digital I/O lines into a single device that is offered on standard PC form factors such as PCI, PCI Express, PXI/CompactPCI, and USB. Using the LabVIEW FPGA Module, you can create your own hardware personalities for custom data acquisition, high-speed control, digital communications protocols, sensor simulation, and onboard signal processing without in-depth knowledge of hardware description languages.

Figure 1. R Series devices are offered on standard PC form factors such as PCI, PCI Express, PXI/CompactPCI, and USB.

What Are the New Multifunction RIO devices?

The newest multifunction RIO devices can be found on the following shop pages:

How do the new R Series devices compare with previous-generation R Series devices?

The new R Series devices are equipped with high-performance Kintex-7 FPGAs, which offer improved optimization capabilities to achieve faster code execution and more LabVIEW code capacity than previous-generation R Series devices. The new Kintex-7 FPGAs are ideally suited for USB R Series devices. This device family has the capacity and performance of previous-generation high-end FPGAs but at half the power. The impressive reduction in power has resulted in the ability to pack up to 10 times the digital signal processing (DSP) capability per device as the previous generation of R Series devices. With this increase in logic and DSP resources, you can implement more complex algorithms with more extensive use of signal processing and real-time analysis and address the growing I/O data rates and complexity of today’s applications. To learn more about Kintex-7 FPGAs, see [Advantages of Xilinx 7 Series FPGA Modules].

In addition, the new NI USB-785xR devices can sample up to 1 M/s on all eight analog input channels with 16-bit resolution and selectable gain resolution of ±10 V, ±5 V, ±2 V, and ±1 V. With FPGA-based parallel execution, multiple control loops do not have to compete for processor bandwidth. Faster analog input rates also improve analog triggering precision and frequency measurement capabilities. The new NI USB-785xR devices also natively support fixed-point I/O, which allows you to work directly with engineering units in the FPGA.

Finally, the new R Series devices feature faster digital I/O channels that can toggle at speeds up to 80 MHz. Furthermore, you can select the voltage levels of the digital I/O lines directly from LabVIEW FPGA. The available logic levels are 3.3 V, 2.5 V, 1.8 V, 1.5 V, and 1.2 V.

Comparison of FPGAs on NI FPGA Products

The number of gates has traditionally been a way to compare FPGA chips to ASIC technology, but it does not truly describe the number of individual components inside an FPGA. This is one of the reasons why Xilinx has moved away from specifying the number of gates in an FPGA. Instead, they compare on a few different components including flip-flops, look-up tables (LUTs), DSP slices, and available block RAM. Review the tables on the Slices on an FPGA Chip guide for more information.

How do I decide which FPGA is right for my application?

Unfortunately, it is difficult to determine whether an application or program will require a larger or smaller FPGA. The LabVIEW FPGA Module and NI-RIO driver give you the ability to compile block diagrams without having any hardware at all, so the best way to see how many resources you need is to try it.

You can use the following as a general guideline when deciding which FPGA works for your application: For an application that performs basic timing, triggering, and synchronization on the FPGA, you can use a smaller FPGA. If the application includes timing, triggering, and synchronization along with additional signal processing on the FPGA (control, digital filtering, complex analog triggering), you will need a larger FPGA that has more resources to implement those operations.

Will my Virtex-II program work on a Virtex-5 or Kintex-7?

In general, a program compiled for a Virtex-II 1M gate FPGA should also compile for a Virtex-5 LX30 or larger, and a program compiled for a Virtex-II 3M gate FPGA should also compile for a Virtex-5 LX50 or larger. Due to architectural differences between the two FPGA families, there are no guarantees, and the only way to see if a program migrates between families is to try it. With the LabVIEW FPGA Module and NI-RIO driver, you can compile block diagrams without having any hardware at all.

Do I need to know VHDL to use LabVIEW FPGA?

No. Using the LabVIEW FPGA Module, you can synthesize graphical code directly from LabVIEW to the FPGA on R Series devices. While knowing how LabVIEW compiles the graphical block diagram to VHDL can help you pinpoint optimization trade-offs, you do not need to understand FPGAs or VHDL to use LabVIEW. LabVIEW is ideal for engineers who need the hardware customization that FPGA technology offers but who do not know or understand low-level hardware description languages such as VHDL or Verilog.

Do I need the LabVIEW FPGA Module to program R Series devices?

Yes, you must use the LabVIEW FPGA Module to program R Series devices. However, if you have existing VHDL IP cores or other VHDL code you wish to use, you can integrate VHDL into a LabVIEW block diagram using the HDL Interface Node.

Read this application note to learn how to integrate VHDL into a LabVIEW block diagram.

Can I program my R Series device in C/C++?

With the FPGA-Interface C API, you can program the real-time processor on NI FPGA-based hardware using C tools such as NI LabWindows™/CVI and Microsoft Visual Studio, and interface to the LabVIEW FPGA code running on the FPGA. In other words, the code running on your host machine can be written in C/C++ or LabVIEW, while the code actually deployed to the FPGA must be written in LabVIEW FPGA.

Learn more about the FPGA-Interface C API.

How is R Series different from other data acquisition families?

Instead of a fixed ASIC for controlling device functionality, R Series data acquisition (DAQ) devices offer a user-programmable FPGA chip for onboard processing and flexible I/O operation. R Series devices feature a dedicated analog-to-digital converter (ADC) per channel for independent timing and triggering. This offers specialized functionality such as multirate sampling and individual channel triggering, which are beyond the capabilities of typical data acquisition hardware. You can define the hardware-timed digital I/O on R Series devices as counters, PWM channels, flexible encoders, or lines for digital communication protocols.

Can I program R Series devices with NI-DAQmx, NI-DAQmx Base, or the NI Measurement Hardware DDK?

All R Series multifunction RIO devices use NI-RIO driver software; they are not compatible with NI-DAQmx or NI-DAQmx Base. There is support, however, within the NI Measurement Hardware DDK (Driver Development Kit) for custom driver development through register-level programming. Once you have compiled and downloaded a LabVIEW FPGA application to an R Series target, the NI Measurement Hardware DDK provides documentation for the host application to interface with registers on the FPGA.

What are the R Series onboard processing capabilities?

The LabVIEW FPGA Module includes a signal processing palette with numerous functions such as:

- PID control

- Butterworth filters (highpass and lowpass)

- Notch filters

- Analog period measurement

- DC and RMS measurement

Can I achieve simultaneous analog input/output with an R Series device?

Yes. All R Series multifunction devices have dedicated ADCs and digital-to-analog converters (DACs) on every analog input/output channel, making it possible to sample/update all channels simultaneously or at different rates. With independent ADCs, you can sample every channel on the device at the maximum rate (up to 1 MS/s). You can program the independent DACs to update analog output channels at rates up to 1 MS/s.

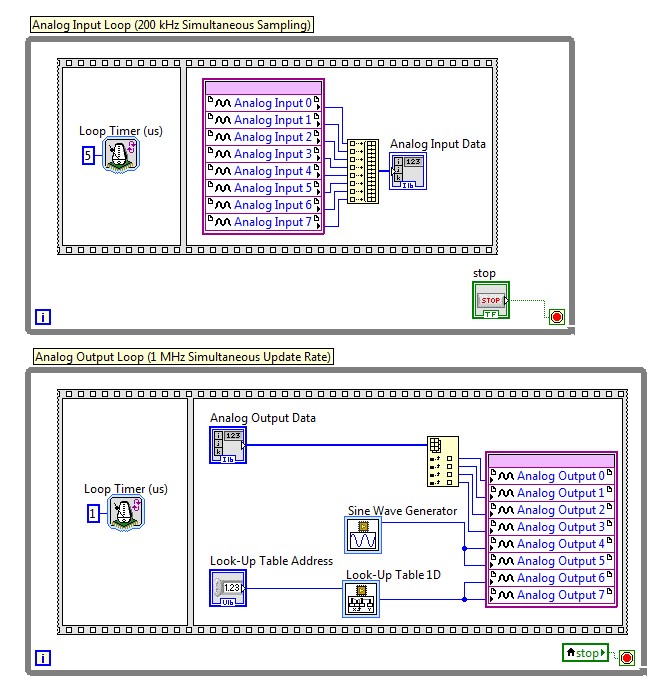

The LabVIEW FPGA block diagram in Figure 2 shows how easy it is to implement simultaneous analog input/output on R Series FPGAs. By using a LabVIEW FPGA Analog Input I/O Node that is reading from all eight channels of the R Series device in the same While Loop, the program samples from all eight channels simultaneously. The lower loop running in parallel uses the LabVIEW FPGA Analog Output I/O Node and updates all eight analog output channels at 1 MS/s.

Figure 2. Simultaneous Analog Input/Output With R Series and LabVIEW FPGA