NI PXI Timing and Synchronization Design Advantages

Contents

- Overview

- Timing and Synchronization for PXI Express Chassis

- Signal and Time-Based Synchronization

- Oscillator Options

- Synchronization Made Easy Through NI Driver APIs

- NI-DAQmx Channel Expansion

- NI-TClk

- NI’s PXI Express Timing and Synchronization-Enhancing Products

- Next Steps

Overview

Timing and synchronization are an integral part of measurement and control systems. We will explore common strategies for achieving performant timing and synchronization. We will examine how NI PXI provides valuable hardware and software advantages to make it easier to design flexible systems that can meet today’s timing and synchronization requirements.

NI PXI Express hardware is the industry’s best-in-class way to build out flexible, multichannel, and multi-instrument systems, and nowhere is that more evident than in timing and synchronization capabilities. Generating high-quality clocks, and sharing sample clocks, time-bases, and low-skew triggers are critical for many measurements and applications.

Clock quality directly affects the following factors:

- Measurement noise

- Distortion

- Frequency accuracy

Tight synchronization from shared clocks, timebases, and triggers is needed for the following purposes:

- Optimizing test times

- Aligning stimuli and responses

- Combining different instruments to make composite measurements

- Building out large scale acquisition systems

- Aggregating data from different sources

While the complexity of managing timing and synchronization in systems can often scale exponentially with system size and mix, the NI PXI Express platform has numerous built-in features that make it easy to synchronize varied I/O with each other within a single PXI Express chassis to a high level of performance. With an assortment of PXI Express timing and synchronization add-on hardware, you can expand synchronization to build multichassis instruments and interface with common standardized time protocols even at large scale.

The built-in features of PXI Express chassis and controllers have many uses:

- Route and share sample clocks and triggers between PXI Express I/O devices

- Includes matched-length backplane PXI_STAR routes for low skew and jitter

- Achieves better than 1 ns synchronization for NI-TClk-enabled devices

- Timestamp data and events

- Enjoy the ease of use provided from high-level NI-TClk and NI-DAQmx APIs that automatically and dynamically establish the necessary backplane connections for clocks and triggers

- Access and manually establish your own routes when you need low-level control

For the next level of accuracy or extendibility, you can augment your PXI Express system with timing and synchronization upgrades to accomplish the following tasks:

- Import and export clocks and triggers

- Utilize the highest quality matched differential trigger (DSTAR) routes

- Interface with common timing protocols and standards such as GPS, IEEE 1588, IEEE 802.1AS, IRIG-B, Automotive Ethernet, and EtherCAT

- Generate high-performance OCXO or rubidium reference clocks

- Generate high-precision arbitrary-frequency clocks

- Extend synchronization features between chassis

Timing and Synchronization for PXI Express Chassis

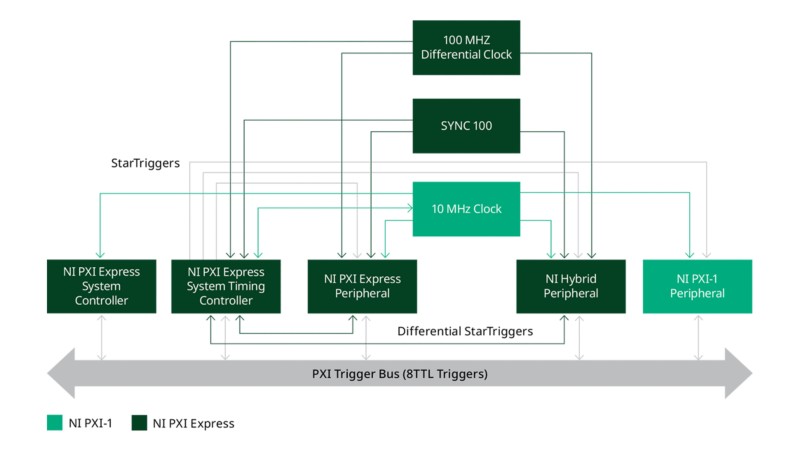

While PXI Gen 1 was a huge step forward in standardizing complex and flexible system design, PXI Express, as the latest evolution of the PXI platform, delivers a higher degree of synchronization to measurement I/O devices while remaining backward compatible with PXI Gen 1. PXI Express maintains the 10 MHz backplane clock as well as the single-ended PXI trigger bus and length-matched PXI star trigger signal provided by the original PXI specification. PXI Express also adds a 100 MHz differential clock and differential star triggers to the backplane to offer increased noise immunity and industry-leading synchronization accuracy (100 ps and 150 ps of module-to-module skew, respectively). The higher frequency 100 MHz clock can be especially helpful in reducing phase noise of higher sampling rate devices such as oscilloscopes that steer their sample clocks based on the backplane clock. These clock and trigger signals (PXI_CLK10, PXI_TRIG, PXI_STAR, and PXI_DSTARA/B/C) can be imported and exported to other PXIe chassis and third-party devices using NI PXI Express timing devices that can control the PXI Express system timing slot. Additionally, PXI Express systems can synchronize their clock and trigger signals to time-aware protocols such as IEEE 1588, IEEE 802.1AS, GPS, IRIG-B, and PPS through specialized NI time-protocol interfaces. For more details and supported NI modules, see Table 1 later in this paper.

Figure 1: PXIe Chassis Timing and Synchronization Features

The phase noise and stability of the backplane system reference clocks are important characteristics of the PXI chassis, as they indicate how reliably you can expect to synchronize modules within the system. With NI PXI Express’s choice of components and backplane design, phase noise performance of the PXI Express 100 MHz differential system clock on an 18-slot chassis is best-in-class compared to other chassis available on the market.

You can phase-lock-loop (PLL) the 10 MHz and 100 MHz system reference clocks to a higher stability clock source than the one provided on the chassis backplane. This helps higher sample rate PXI modules to better align their samples across multiple instruments. The PLL circuitry of the NI PXI chassis can suppress more noise when locking to an external reference, thus permitting cleaner transmission of the higher stability clock source. With other vendors’ chassis, depending on the system clock source phase noise required by the application, you may need to phase-lock the external reference clock to each module individually, rather than at a system-level to the chassis backplane, resulting in an increase in system complexity and cost.

Signal and Time-Based Synchronization

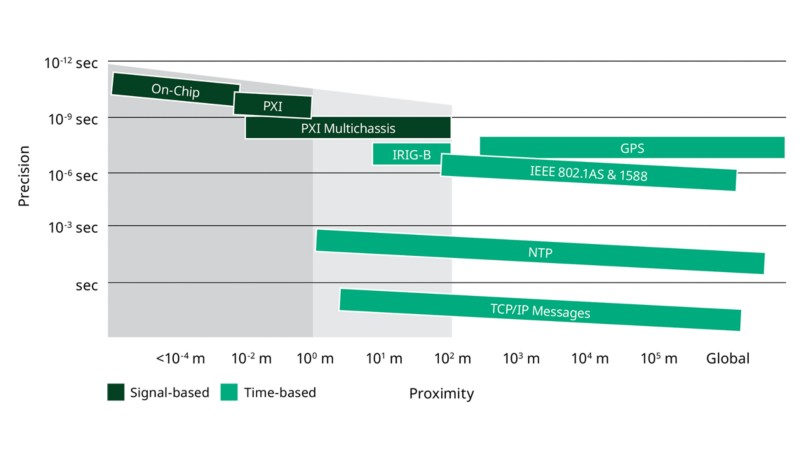

NI PXI Express timing and synchronization features work with two different types of synchronization architectures, signal-based and time-based, so you can achieve the flexibility and customization you need when developing applications that require different levels of performance.

Figure 2: Signal-Based and Time-Based Synchronization Architecture Performance

With an NI PXI Express signal-based timing and synchronization architecture, clocks and triggers are physically connected between modules and chassis. This typically generates the highest precision of synchronization. However, with longer than certain subsystem-connecting cable distances (approximately 200 m), this performance is unachievable because of clock skew and noise.

If the required distance between synchronized chassis is too great for cables to reliably transmit clock and trigger signals, you must use a time-based synchronization architecture. Timebase synchronization can also be an important aspect of integrating with other systems or DUTs that rely on time protocols. The NI PXI Express timing and synchronization solution allows you to use absolute time reference protocols such as IEEE 1588, IEEE 802.1AS, GPS, and IRIG-B to achieve synchronization over large distances.

Oscillator Options

No oscillator perfectly generates the specified frequency. Clock error is commonly described by three major components: absolute accuracy, long-term stability, and jitter. While synchronizing devices together can eliminate long-term stability as a clock error source between components of a system, and while PLLs can help reduce jitter when sharing clocks, you cannot improve clock accuracy without having a better clock. If clock accuracy matters, a high-quality clock source is necessary.

For an NI PXI Express chassis, the clock source is an oscillator that is accurate to 25 parts per million (ppm). By inserting an NI PXI timing and synchronization module, such as the PXIe-6674T with a higher-accuracy and stability oven-controlled crystal oscillator (OCXO), into the system timing slot of the chassis, you can lock the backplane reference clock to an oscillator frequency source that is accurate to 50 parts per billion (ppb) or import an external clock source. For special cases where 50 ppb is insufficient for long-term stability (such as systems that run offline for days but still need to correlate time with other systems and devices that they aren’t connected to), the PXIe-6674T can be combined with a best-in-industry rubidium-based PXIe-3352 clock source or through a GPS-disciplined-oscillator (GPSDO) such as the PXI-6683H, PXIe-3352, or CDA-2990.

Figure 3: NI PXIe-6674T—The Industry’s Highest Performance PXI Timing and Synchronization Module with OCXO

NI PXI timing and synchronization modules can improve the overall system clock error by generating and sharing a precision clock source among multiple PXI devices.

Synchronization Made Easy Through NI Driver APIs

The PXI timing triggers and clocks are configurable at a low level through NI I/O instrument drivers as well as through the NI-Sync driver, which exposes all the timing features of the chassis for direct utilization by the I/O devices. Intelligent signal aliasing makes it easier and more flexible to set up dynamic routes for triggering that rely on device name rather than on slot number, making it easier to migrate an application to a different chassis or slightly different set of instruments. This modularity makes NI PXI Express hardware well suited to system designs that are subject to changing requirements and last-minute device substitutions, since the complex work of synchronization architecture and routing can usually be established programmatically.

For more information on synchronization in NI IO instrument drivers, refer to Timing and Synchronization Features of NI-DAQmx.

NI-DAQmx Channel Expansion

NI has enhanced the NI-DAQmx driver with an innovative approach to configure multiple DAQ modules for synchronization. A full chassis of almost any single DAQ module type can be programmed with one multidevice task. With multidevice tasks, you can scale your application from one to 544 channels using the same DAQmx code. You can also use a single DAQmx task to automatically synchronize channels across multiple boards with different measurement types.

For more information about DAQmx Channel Expansion in PXI Express, refer to:

DSA, SC Express, and X Series Multidevice Tasks

NI-DAQmx Synchronization of PXI Express Modules

NI-TClk

For applications requiring the synchronization of high-speed PXI modular instruments, distributing the necessary clocks and triggers to achieve this synchronization can be challenging because of the latencies and timing uncertainties caused by skew and jitter. The complexity is further compounded when attempting to synchronize heterogeneous instruments running at different sample rates.

Precise synchronization in these cases often involves attempting to share a low-skew reference clock between all the instruments, employing phase-lock loops (PLLs) and multipliers attached to that reference clock to generate each device’s unique sample clock, and distributing a low skew trigger to all the instruments, some sort of finely tunable time delay compensation mechanism, and some sort of calibration measurement upon which to base adjustments. Not only is this complicated to do both in the hardware and the software implementations, it’s also fragile since even a slight instrument model swap can cause the whole architecture to have to be reworked and all the calibration to be redone.

NI PXI is the best way to build mixed, flexible, high-speed, and expandable IO systems. To help reduce the inherent complexity of high-speed instrument synchronization, NI developed a patented method for synchronization, called NI-TClk, that greatly simplifies adding additional high speed instruments and keeping them synchronous down to 1 ns accuracy out-of-the-box or to tens of ps with manual calibration.

NI-TClk technology can help you in the following ways:

- Align the sample clocks that may not necessarily be aligned initially despite being phase locked to the 10 MHz reference clock

- Enable the accurate triggering of synchronized devices

The flexible NI-TClk technology is applicable to the following use cases:

- High-speed modular instrument synchronization with a sample clock or reference clock

- Extending synchronization from a single PXI chassis to several PXI chassis to address high-channel systems using a system timing module

- Homogeneous and heterogeneous synchronization—devices running at the same or different sample rates using internal or external sample clocks

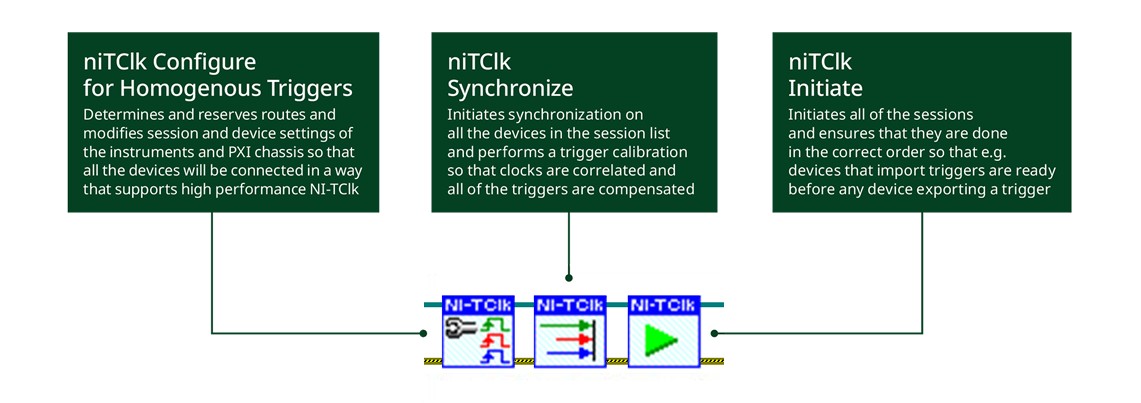

NI-TClk technology delivers PXI modular instrument synchronization performance improvements right out of the box. The key software components comprise three LabVIEW VIs/C functions that require no parameters to be set. NI-TClk architectures can deliver synchronized devices with skews of at worst 1 ns between each device. Typical skews observed are in the range of 200 ps to 500 ps. Manual calibration of the sample clock on each device can lower skews to less than 30 ps between devices.

Figure 4: Required NI-TClk Functions

In situations where high speed and heterogeneous device synchronization must be highly accurate, NI-TClk reduces a mountain of complexity into just three VIs. Within a single PXI chassis, as large as 18 slots, all the NI-TClk-capable devices can synchronize with those three VIs using built-in features of the NI PXI chassis. No additional cables. No external PLLs. No manual routing. No special software. It’s all handled automatically by NI-TClk. Neither swapping models out for other models, nor changing slots of the instruments, nor changing samples rates will result in having to rework this synchronization code. NI-TClk automatically adapts to all of those changes and keeps the test writer working on the logic of the test steps rather than on solving complex triggering architectures. NI Modules and Devices Supported by NI-TClk provides a complete list of I/O devices that support NI-TClk.

NI’s PXI Express Timing and Synchronization-Enhancing Products

While many of the amazing timing and synchronization of PXI Express are built-in to the PXI Express chassis, some come through special chassis upgrades, modules, or accessories. Here’s a quick look at those options:

| Product | Overview | Technical Summary |

|---|---|---|

| PXI Express Chassis | The most flexible and capable platform for building complex test and measurement systems | Built-in 25 ppm-accurate PXI_Clk10, onboard PXI_TRIG/PXI_STAR, easy trigger and clock routing within chassis, NI-DAQmx channel expansion support, NI-TClk support |

| PXIe-1084 with External Trigger Access | Chassis with integrated clock in/out | Standard PXIe chassis features, import/export/daisy-chain of PXI_Clk10 and PXI_TRIG lines |

|

| Chassis with integrated clock In/out | Standard PXIe chassis features, import/export/daisy-chain of PXI_Clk10 |

| PXIe-1092 with OCXO | Chassis with integrated clock In/out and OCXO | <100 ppb-accurate PXI_CLK10, standard PXIe chassis features, import/export/daisy-chain of PXI_Clk10 and PXI_TRIG lines |

| PXIe-1095 with OCXO | Chassis with integrated clock in/out and OCXO | <100 ppb-accurate PXI_CLK10, standard PXIe chassis features, import/export/daisy-chain of PXI_Clk10 and PXI_TRIG lines |

| PXIe-6674T | 1-slot timing master module for generation and import/export of all PXI timing signals | <100 ppb-accurate PXI_CLK10, enables import/export of PXI_Clk10/PXI_TRIG/PXI_STAR/PXI_DSTAR for multi-chassis sync, DDS clock generation |

| PXIe-6672 | 1-slot timing master module for generation and import/export of most PXI timing signals | <5 ppm-accurate PXI_CLK10, enables import/export of PXI_Clk10/PXI_TRIG/PXI_STAR for multi-chassis sync, DDS clock generation |

| PXIe-3352 | 2-slot super stable clock source module | 0.030 ppb-accurate 10 MHz rubidium clock which can be imported with a PXIe-1085/1092/1095/6674T/or 6672, GPS-disciplined oscillator with rubidium holdover, PPS import/export |

| PXI-6683H | 1-slot timing protocol interface and GPS-disciplined oscillator module | <5 ppm-accurate PXI_CLK10, GPS-disciplined oscillator which can be imported with a PXIe-1085/1092/1095/6674T/or 6672, GPS positioning, PPS import/export, IRIG-B support, IEEE-1588 and IEEE 802.1AS (Linux only) timekeeper and timestamping which can also override OS system time |

| CDA-2990 | Clock distribution and GPS-disciplined oscillator accessory | GPS-disciplined oscillator 10 MHz, PPS output, 1 to 8 clock distribution |

| cRIO-9805 | IEEE 802.1AS Ethernet switch | 4 ports |

Table 1: PXI Express Timing and Synchronization-Enhancing Products