Increase IP Reuse With the Xilinx CORE Generator IP Palette

Overview

To increase your software development productivity, efficient code reuse is important. With field-programmable gate array (FPGA) hardware, reusable code blocks are often called IP blocks. The NI LabVIEW FPGA Module offers many ways to access IP blocks in the product. While the LabVIEW FPGA Module provides numerous built-in functions for math and signal processing, it is common to use off-the-shelf IP libraries from other sources. The LabVIEW 2011 FPGA Module and later versions include a set of high-performance libraries created by Xilinx and fine-tuned for Xilinx FPGA hardware. To increase your FPGA project productivity, learn more about Xilinx CORE Generator IP palette functionality and how to use it.

Contents

- Xilinx CORE Generator Palette Summary

- Licensing Xilinx CORE Generator IP Blocks

- Development Considerations With CORE Generator IP

- Integrate a CORE Generator IP Block Into LabVIEW

- Other Ways to Import Third-Party IP

- Advanced, Optimized Functionality for FPGAs

- Next Steps

Xilinx CORE Generator Palette Summary

Basic Functions

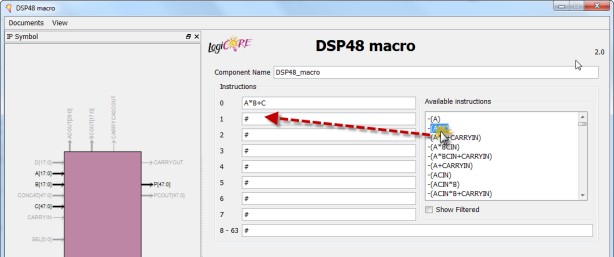

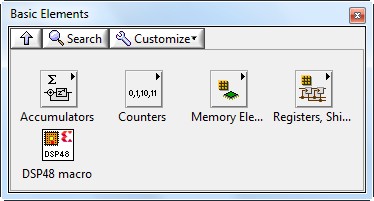

The basic IP palettes include highly optimized accumulator, counter, and memory generator functions. You can also use the DSP48 Macro function to generate customized IP through the Configuration Wizard. This macro wizard steps you through the customization of the DSP48 through specifying instructions, pipeline configurations and ports, so you can take advantage of the DSP48 power without having to manually configure these complex settings.

Figure 1: Using the DSP48 Macro function, you can quickly configure and generate a custom IP block for LabVIEW FPGA.

| IP Product Page IP | |

Figure 2: BaseIP LabVIEW FPGA Palette |

|

Figure 3: Basic Element LabVIEW FPGA Palette |

Digital Signal Processing (DSP)

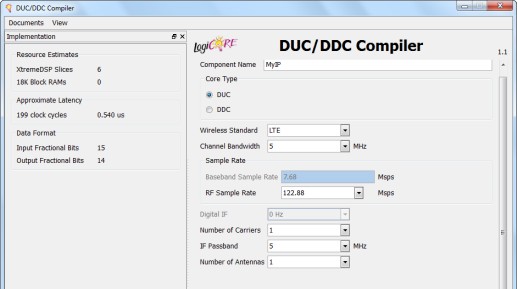

The DSP CORE Generator palette includes filter and transform libraries to accelerate signal processing application development. Although configuration-based, the CORE Generator Wizard exposes a wide variety of parameters including resource usage estimates and an IP symbol to clearly show current port utilization. With this highly parameterized approach, you can achieve the flexibility and efficiency of customized IP generation.

Figure 4: The Xilinx CORE Generator dialogs expose many IP parameters and specifications to help you customize the core for specific application needs.

Figure 5: Digital Signal Processing Palette | IP Product Page |

Coordinate Rotational Digital Computer (CORDIC) Cascaded Integrator-Comb Compiler |

1You need a Xilinx license to use this CORE Generator IP core. Reference the IP product page for more information.

Math Functions

The CORE Generator palette math functions range from basic to advanced. For example, the palette includes a block that generates IP for conversion to, and basic operations for, floating-point numbers on an FPGA. As shown in Figure 6, you can use the IP Configuration Wizard to easily select the floating-point operations for which you want to generate code.

Figure 6: The Xilinx CORE Generator Floating-point Operator IP core offers a floating-point function library for LabVIEW FPGA.

Figure 7: Math Functions Palette | IP Product Page |

|

Memories & Data Storage Elements

Figure 8: Memories & Storage Elements Palette | IP Product Page |

Advanced Industry-Specific Palettes

The CORE Generator IP palette includes two communications and image processing palettes that you can reuse to reduce your FPGA design time.

Communications & Networking

Figure 9: Communication & Networking Palette | IP Product Page |

Error Correction IP 3GPP2 Turbo Decoder1 Viterbi Decoder1 3GPP Searcher1 LTE FFT 1 Wireless IP DPD1 Peak Cancellation Crest Factor Reduction1

|

1You need a Xilinx license to use this CORE Generator IP core. Reference the IP product page for more information.

Vision & Image Processing

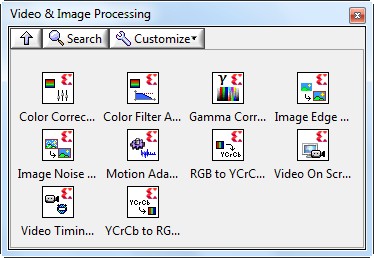

Figure 10: Video & Image Processing Palette | IP Product Page |

RGB to YCrCb Color-Space Converter YCrCb to RGB Color-Space Converter Color Filter Array Interpolation1 Gamma Correction1

|

1You need a Xilinx license to use this CORE Generator IP core. Reference the IP product page for more information.

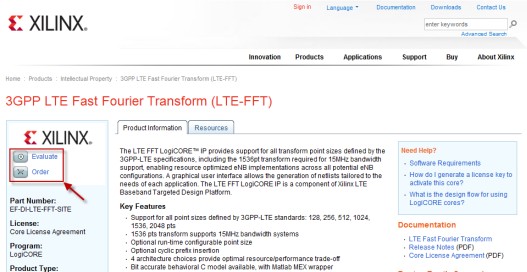

Licensing Xilinx CORE Generator IP Blocks

As noted, some Xilinx IP blocks require licenses. To find out more about licensing costs and processes, click an IP block link above.

Figure 11: Xilinx IP product pages include evaluation and ordering information for CORE Generator blocks that require licensing.

Development Considerations With CORE Generator IP

Similar to other high-performance IP blocks in LabVIEW FPGA, there are some development considerations to keep in mind when using the CORE Generator libraries in an application. CORE Generator IP can only execute in single-cycle Timed Loops. Because CORE Generator IP often is internally pipelined, similar to the high-performance math functions, output data is not validate on each clock, and you should use the IP control signal outputs to signal when the data is validate.

In addition, Xilinx CORE Generator library support is limited to Xilinx Virtex-5 and Spartan-6 FPGAs, so ensure that you are using NI reconfigurable I/O hardware that includes one of these FPGA targets.

Consult the IP block data sheets on the product pages for more detailed considerations.

Integrate a CORE Generator IP Block Into LabVIEW

To execute a floating-point square root calculation using the Float-point Operator IP core on the CORE Generator palette

- Create a new LabVIEW FPGA project (this example targets the Virtex-5 FPGA in an NI cRIO-9113 chassis).

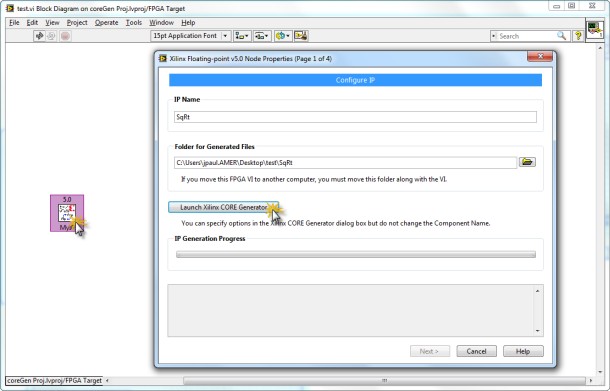

- Create a new FPGA VI. Select Programming»Xilinx Coregen IP»Math Functions»Floating-point and drag the floating-point IP core onto the FPGA block diagram.

Save the VI and double-click the IP block to open the Xilinx Floating-point v5.0 Node Properties window. To start the CORE Generator IP Configuration Wizard, click Launch Xilinx CORE Generator.

Figure 12: Launch the Xilinx CORE Generator.

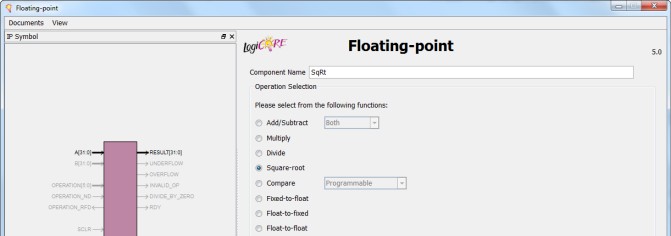

In the dialog window, select a floating-point function to execute (here, Square-root). Leave the other wizard settings at default by clicking through the remaining steps, and click the Generate button. IP core generation may take a few minutes to complete.

Figure 13: Generate an IP core.

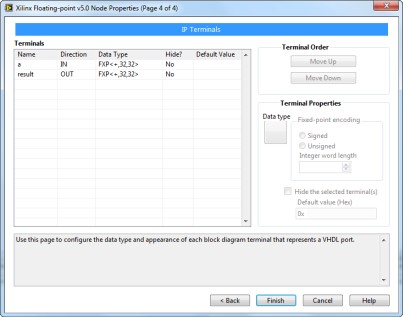

Once IP generation is complete, leave the next two properties in the Xilinx Floating-point v5.0 Node Properties window at their default settings. You can customize your block by selecting a clock signal and configuring the reset behavior. Click Finish to complete the generation process.

Figure 14: Complete the generation process.

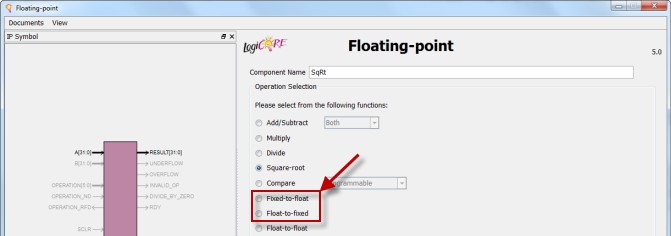

Repeat steps two through five twice to generate two more IP blocks – one for the fixed- to floating-point data type and the other for the floating- to fixed-point data type. Select this functionality in the first step of the Floating-point Operator CORE Generator Configuration Wizard, as shown Figure 15.

Figure 15: Floating-Point Operator CORE Generator Wizard

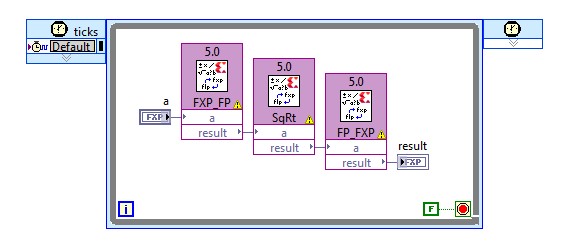

- Finally, wire the IP blocks and place the logic inside a single-cycle Timed Loop, as shown in Figure 16.

Figure 16: Wire the IP blocks and place them inside a single-cycle Timed Loop.

You have now implemented a floating-point square-root operation, which you can incorporate into new or existing LabVIEW FPGA applications.

Other Ways to Import Third-Party IP

If you have acquired or created other VHDL or Verilog IP, you can import it using the Component-Level IP (CLIP) Node or IP Integration Node.

To learn more, read Importing External IP into LabVIEW FPGA.

Advanced, Optimized Functionality for FPGAs

The more IP at your disposal, the more efficiently you can complete your LabVIEW FPGA applications. The over 50 IP cores available with the Xilinx CORE Generator IP palette offer you even more advanced functionality optimized for Xilinx FPGAs. With the included configuration-based wizards, you can easily set up and customize IP blocks for your specific application.