Compile Faster with the LabVIEW FPGA Compile Cloud Service

Overview

As engineers use more sophisticated FPGA technology for their applications, FPGA compilation grows computationally more complex and takes longer to complete. To help maximize the productivity of LabVIEW FPGA Module users, NI offers complimentary use of the LabVIEW FPGA Compile Cloud Service for LabVIEW FPGA users with an active software subscription license or service agreement.

Contents

Benefits

The LabVIEW FPGA Compile Cloud offers many benefits to LabVIEW FPGA users, including:

- Shorter compile times enabled by high-performance Linux-based servers in the cloud

- Improved productivity by performing multiple compiles at a time, in parallel

- Keeps your development computer free to perform other tasks

- Provides the convenience of being able to power-down your PC at any time during a compile

- Increases space available on your hard drive if you choose to use the Compile Cloud Service exclusively, and do not have a need to install the Xilinx compilation tools locally (see Software Requirements for FPGA Compile Cloud Service)

How it Works

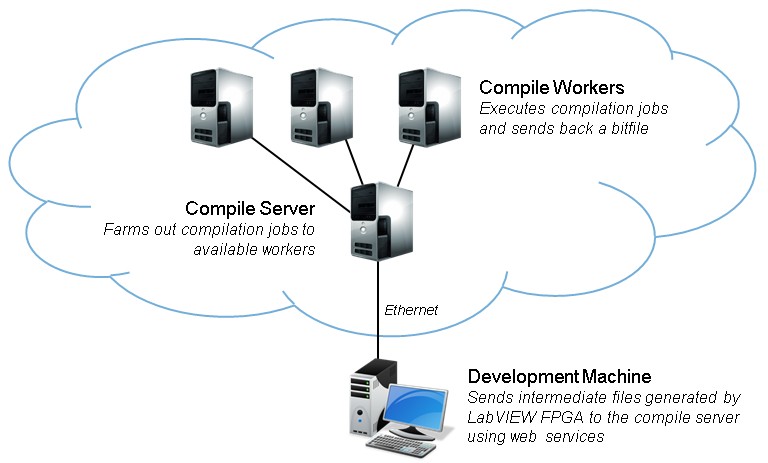

NI has architected the LabVIEW FPGA compile system with three fundamental software components, resulting in a modular, scalable compile solution. The compile system is split into three parts: the development computer, the server, and any number of workers.

Development Machine —The LabVIEW development environment is where you create your LabVIEW FPGA VI. When you compile your LabVIEW FPGA VI, the compiler completes the Generating Intermediate Files step. After generation, the development computer sends the intermediate files through web services communication to the FPGA compile server. All communication between the development computer and the FPGA compile server is sent over an encrypted channel. For more information on the LabVIEW FPGA compilation process, see the whitepaper LabVIEW FPGA Compilation Process: From Run Button to Bitfile.

Compile Server—The server accepts compile jobs from many LabVIEW FPGA development systems and looks for available workers to farm out the compilation jobs. If no workers are available, the server holds the compile job in a queue until a worker becomes available.

Compile Workers—The workers have the Xilinx compilation tools installed for FPGA design synthesis, mapping, placing, and routing. With these tools, a worker executes the compile on the design and eventually generates a bit file that it sends back to the server, where the server sends it back to the development computer.

Figure 1: The compile system is split into three parts: the development machine, the compile server, and the compile workers.

How to Get Started

To get started with the LabVIEW FPGA Compile Cloud service follow these basic steps:

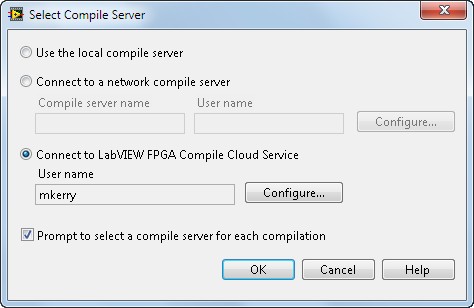

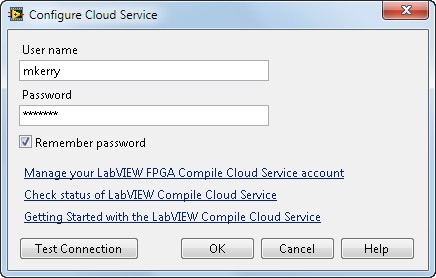

Figure 2. Connect to the cloud from within the LabVIEW development environment