Build Timing Source Hierarchy VI

- Updated2025-01-28

- 2 minute(s) read

Build Timing Source Hierarchy VI

Creates a hierarchy of timing sources based on the names you enter in timing source names.

Inputs/Outputs

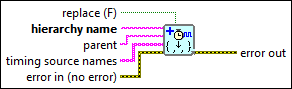

replace (F)

—

replace (F)

—

replace (F) replaces any timing source you entered in timing source names if a timing source by that name already exists in the hierarchy of timing sources.  hierarchy name

—

hierarchy name

—

hierarchy name is the name of the timing source hierarchy you want to create.  parent

—

parent

—

parent is the valid timing source you want to start after the all the timing sources in hierarchy name start.  timing source names

—

timing source names

—

timing source names is an array of names of the timing sources you want to add to the timing source hierarchy. If replace is TRUE, the new timing source replaces any timing source with the same name that already exists in the timing source hierarchy. These timing sources start before the timing source you enter in parent.  error in (no error)

—

error in (no error)

—

error in describes error conditions that occur before this node runs. This input provides standard error in functionality.  error out

—

error out

—

error out contains error information. This output provides standard error out functionality. |

The hierarchy determines the order in which the timing sources start. The parent timing source does not start until after the timing sources in hierarchy name start. Use this VI when you have timing sources that have signal dependencies, such as DAQ counters routed to drive analog input connections. In such a case, the counter timing source acts as the parent.