While Loop

- Updated2025-03-14

- 3 minute(s) read

Repeats the code within its subdiagram until a specific condition occurs. A While Loop always executes at least one time.

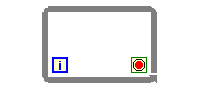

Components of a While Loop

—Subdiagram—Contains code that the While Loop executes once per iteration.

—Subdiagram—Contains code that the While Loop executes once per iteration.  —Iteration Terminal (i)—Provides the current loop iteration count. The loop count always starts at zero for the first iteration. If the iteration count exceeds 2,147,483,647, or 231-1, the iteration terminal remains at 2,147,483,647 for all further iterations. If you need to keep count of more than 2,147,483,647 iterations, you can use shift registers with a greater integer range.

—Iteration Terminal (i)—Provides the current loop iteration count. The loop count always starts at zero for the first iteration. If the iteration count exceeds 2,147,483,647, or 231-1, the iteration terminal remains at 2,147,483,647 for all further iterations. If you need to keep count of more than 2,147,483,647 iterations, you can use shift registers with a greater integer range.  —Conditional Terminal—Evaluates a Boolean input value to determine whether to continue executing the While Loop. To specify whether the loop stops for a TRUE or FALSE Boolean value, configure the continuation behavior of the loop. You also can determine when the loop stops by wiring an error cluster to the conditional terminal.

—Conditional Terminal—Evaluates a Boolean input value to determine whether to continue executing the While Loop. To specify whether the loop stops for a TRUE or FALSE Boolean value, configure the continuation behavior of the loop. You also can determine when the loop stops by wiring an error cluster to the conditional terminal. Tip To create a While Loop that automatically wires a stop button to the conditional terminal, add the While Loop from the Execution Control palette.

FPGA Module Details

The following details apply when you use this object in an FPGA VI.

Note The following details are subject to change with each version of the LabVIEW FPGA Module.

| Single-Cycle Timed Loop | Not supported. |

| Usage | The iteration (i) terminal is a 32-bit signed integer that saturates on reaching its maximum value, 2^31 - 1. |

| Timing | The While Loop incurs two clock cycles of overhead between iterations. If the While Loop contains initialized shift registers, it takes one clock cycle before the first iteration to initialize shift register values. Code placed in a While Loop generally takes longer to execute than the same code placed in a single-cycle Timed Loop. |

| Resources | The While Loop consists of a small state machine. Shift registers require FPGA resources in proportion to the width of the data type. Loop auto-indexers consist of a hidden shift register for each array element. |

Configuring a While Loop

- Creating a basic While Loop

- Adjusting the timing of execution

- Automatically processing each element in an array

- Accumulating data in arrays leaving loops

- Passing values between iterations

- Monitoring the Boolean value of a terminal for each loop iteration

- Converting a While Loop to a For Loop or Timed Loop

- Conditionally writing values to output tunnels