Digitale Zustände, Spannungspegel und Logikfamilien

Überblick

Erfahren Sie mehr über digitale Zustände, Spannungslogikpegel und Logikpegelfamilien für Digitalsignale. Diese Anleitung ist Teil der Reihe „Gerätegrundlagen“.

Inhalt

Digitale Zustände

Bei digitalen Geräten gibt es nur zwei Zustände: Ein und Aus. Allein mit diesen beiden Zuständen können Geräte viele Daten austauschen und verschiedene andere Geräte steuern. In binärer Form werden diese Zustände als 1 oder 0 dargestellt. Binär 1 wird normalerweise als logisch High und 0 als logisch Low angesehen.

Spannungspegel

Digitale Geräte werden jedoch oft von analogen Geräten mit unendlich vielen Zuständen angesteuert. Wie kann man aus so vielen Zuständen zwei machen? Die Antwort besteht darin, logische Spannungspegel zu erzeugen, die die Spannung so definieren, dass sie ein logisches High oder logisches Low darstellt.

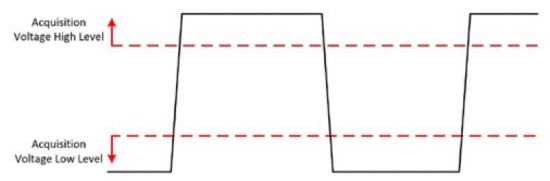

Abbildung 1: Spannungspegel definieren die Analogspannung als logisches High oder Low.

Ein System kann die Spannungslogikpegel auf jeden beliebigen Wert festlegen. Aber viele Schaltungen stellen ein logisches High von +5 V oder +3,3 V gegen Masse und ein logisches Low von Masse oder 0 V dar. Diese Art von System wird als positiv oder aktiv-hoch bezeichnet. Es beschreibt, wie der Kontakt aktiviert wird. Bei einem aktiven High-Kontakt wird es mit Ihrer Hochspannung verbunden.

Ein negatives oder ein aktives Low-System ist das Gegenteil davon. Die höhere Spannung stellt ein logisches Low und die niedrigere Spannung ein logisches High dar. Bei einem aktiven Low-Kontakt müssen Sie diesen Kontakt auf Low ziehen, indem Sie ihn mit der Masse verbinden. In Datenblättern wird oft ein Strich über dem Kontaktnamen angezeigt, z. B. EN.

Obwohl ein High und ein Low angegeben sind, gibt es in den meisten Systemen aus praktischen Gründen einen Bereich. Ein logisches High kann beispielsweise ein Wert zwischen 2 V und 5 V sein, ein Low kann ein Wert zwischen 0 V und 1 V sein. Spannungen außerhalb dieses Bereichs werden als ungültig betrachtet und treten nur im Fehlerzustand oder während eines Logikpegel-Übergangs auf.

Z- und X-Zustände

Obwohl ein digitales Signal nur zwei Zustände haben kann (Ein und Aus), können Sie zusätzliche Zustände verwenden, um das Erfassen und Erzeugen digitaler Signale zu unterstützen. Bei der Tristate-Logik gibt es eine dritte mögliche Bedingung: einen hochohmigen Zustand, bei dem der Ausgang von der Leitung getrennt ist. Dieser Zustand ist kein High- oder Low-Zustand, sondern ein schwebender oder hochohmiger Zustand. Er hat die Bezeichnung Z und wird oft als Aktivierungsleitung verwendet.

Der Z-Zustand wird am häufigsten zum Testen einer oder mehrerer digitaler Leitungen verwendet, die von mehreren Sendern angesteuert werden können. Die Datenschnittstelle auf einem Speicherchip ist ein gutes Beispiel dafür. Wenn der Computer Daten auf das Speichergerät schreibt, muss er die Daten, die in den Speicherchip geschrieben werden sollen, an den Datenkontakten des Speichergeräts ansteuern (entweder 0 oder 1). Wenn der Computerprozessor später den Inhalt des Speichers auslesen muss, muss das Speichergerät den zuvor gespeicherten Datenwert an den Computerprozessor zurückgeben (normalerweise ein Z-Zustand an den Datenkontakten).

Ein vierter Zustand ist der mit einem X gekennzeichnete Haltezustand. Bei der Erzeugung digitaler Signale kann es hilfreich sein, den Kanal einfach im aktuellen Zustand beizubehalten, unabhängig davon, in welchem Zustand er sich befindet. Dieser Zustand ist nützlich, wenn der Anfangs- oder inaktive Zustand festgelegt wird.

Beim Erfassen von Daten hat der X-Zustand eine andere Bezeichnung als „egal“. Dieser Zustand ist hilfreich, wenn Sie ein erfasstes Digitalsignal mit einem erwarteten Signal vergleichen. Bei einem Signal mit zehn Werten können beispielsweise nur die ersten vier Werte berücksichtigt werden. Sie können den X-Zustand für die letzten sechs Werte verwenden und nur die ersten vier vergleichen.

| Zustand | Bezeichnung |

|---|---|

| 0 | Logisch Low |

| 1 | Logisch High |

| Z | Hohe Impedanz |

| X | Haltezustand oder „egal“ |

Tabelle 1: Ein Digitalsignal kann sich nur im High- oder Low-Zustand befinden. Die Zustände Z und X können jedoch bei Anwendungen hilfreich sein, die Digitalsignale erzeugen oder erfassen.

Logikfamilien

Standardisierte Logikfamilien erleichtern die Arbeit mit Schaltungen und Komponenten. Sie liefern einen standardisierten Spannungspegel, der ein logisches High oder logisches Low darstellt. Alle Schaltungen einer Logikfamilie sind mit anderen Schaltungen derselben Familie kompatibel, da sie dieselben Eigenschaften aufweisen.

Gegen Bezugspotenzial geschaltete Logikfamilien

Gegen Bezugspotenzial geschaltete Logikfamilien geben Spannungspegel in Bezug auf Masse an. Die vier Ebenen sind wie folgt definiert:

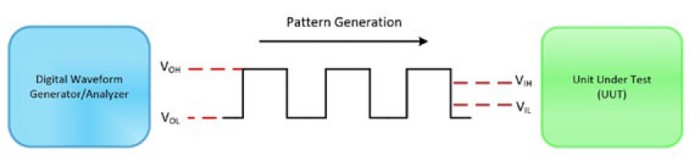

- VOH (High-Pegel-Ausgangsspannung) – Dies wird auch als High-Pegel der Erzeugungsspannung bezeichnet. Bei der Konfiguration für aktive Antriebserzeugung ist dies die Spannung, die das Gerät erzeugt, wenn es ein logisches High erzeugt. Bei Konfiguration für Offene-Kollektor-Erzeugung entspricht dies dem Einstellen des Datenkanals in einen hochohmigen Zustand.

- VOL (Low-Pegel-Ausgangsspannung) – Dies wird auch als Low-Pegel der Erzeugungsspannung bezeichnet. Dies ist die Spannung, die das Gerät erzeugt, wenn es ein logisches Low erzeugt.

- VIH (High-Pegel-Eingangsspannung) – Dies wird auch als High-Pegel der Erfassungsspannung bezeichnet. Dies ist der Spannungspegel, der an das Gerät gesendet werden muss, damit es ein logisches High lesen kann.

- VIL (Low-Pegel-Eingangsspannung) – Dies wird auch als Low-Pegel der Erfassungsspannung bezeichnet. Dies ist der Spannungspegel, der an das Gerät gesendet werden muss, um ein logisches Low zu lesen.

Abbildung 2: Gegen Bezugspotenzial geschaltete Logikpegel sind für Ausgang und Eingang spezifiziert.

Für eine korrekte Kommunikation mit einem Gerät muss das digitale Gerät so konfiguriert sein, dass die folgenden Bedingungen erfüllt sind:

- VOH ≥ DUT VIH

- VOL ≤ DUT VIL

- VIH ≤ DUT VOH

- VIL ≥ DUT VOL

- VIH > VIL

Normalerweise besteht ein Puffer zwischen der Ausgangsspannung eines Geräts und dem Eingang eines anderen Geräts. Dies wird als Rauschgrenze (Noise Margin) oder Störfestigkeitsgrad (NIM, Noise Immunity Level) bezeichnet. Wenn Sie sich in einer störungsreichen Umgebung befinden und Probleme mit falschen Datenbits auftreten, sollten Sie diesen Wert erhöhen.

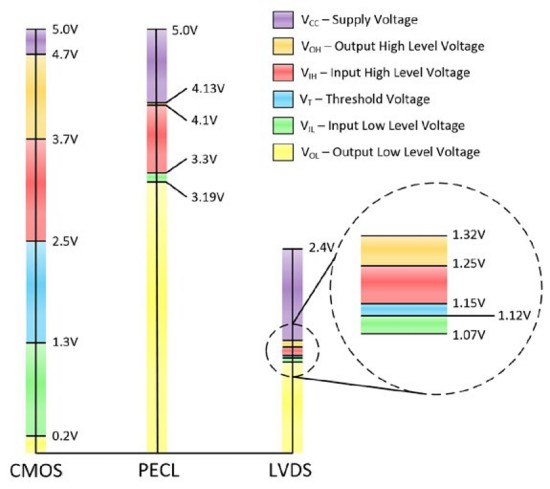

Es gibt mehrere gegen Bezugspotenzial geschaltete Logikfamilien. Die Transistor-Transistor-Logik (TTL) ist bei integrierten Schaltungen weit verbreitet und wird in vielen Anwendungen wie Computern, Unterhaltungselektronik und Prüfgeräten verwendet. Schaltungen aus Bipolartransistoren erreichen logische Zustände und halten sie aufrecht. Eine TTL muss außerdem bestimmte Stromspezifikationen und Anstiegs-/Abfallzeiten erfüllen. Weitere Informationen dazu finden Sie unter Was ist die Definition eines TTL-kompatiblen Signals?

Abbildung 3: Standardmäßig-5-V-TTL-Spannungspegel

Eine weitere verbreitete IC-Familie ist CMOS. Diese Geräte haben eine hohe Störfestigkeit, verbrauchen weniger und haben eine niedrigere Basisspannung. Die meisten Spannungspegel sind aus Gründen der Kompatibilität denen von TTL-Geräten ähnlich. Dies erleichtert den Wechsel von einem TTL- auf ein CMOS-Gerät, aber der umgekehrte Weg kann schwieriger sein. Eine zu hohe Spannung an einem CMOS-Gerät kann den Chip beschädigen. In diesem Fall können Sie die Spannung mit einem Spannungsteiler reduzieren.

Abbildung 4: Standard-CMOS-Spannungspegel

Differentielle Logikfamilien

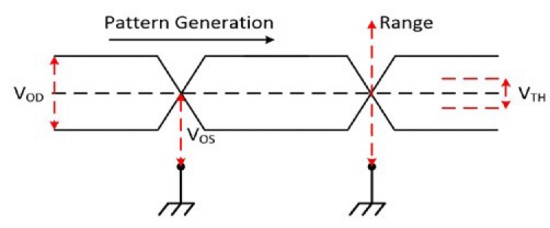

Gegen Bezugspotenzial geschaltete Logikfamilien verwenden einen festgelegten Spannungspegel in Bezug auf Masse. Differenziallogikfamilien verwenden jedoch die Differenz zwischen zwei Werten und keine Referenz auf Masse. Damit das differenzielle Signal als logisch Low interpretiert werden kann, muss das Signal um mehr als einen bestimmten Wert, der als Schwellenwert bezeichnet wird, kleiner als sein komplementäres Signal sein. Da die Signale referenziert und gemeinsam übertragen werden, können Sie eine höhere Störfestigkeit Ihrer Signale erreichen als bei Verwendung von gegen Bezugspotenzial geschalteten Logikfamilien. Spannungspegel für differentielle Logikfamilien werden in der Regel als differentielle und nicht als absolute Spannung angegeben. Die vier Ebenen sind wie folgt definiert:

- VOD (Ausgangsdifferenzspannung) – Dies ist die Spannungsdifferenz zwischen den Signalen.

- VOS (Offset-Spannung) – Dies ist der Gleichtakt des differenziellen Signals. Betrachten Sie dies als den Mittelwert der beiden Signale. Er hat eine Referenz auf Masse.

- VTH (Schwellwertspannung) – Dies ist die Spannungsdifferenz, die das Gerät benötigt, um einen gültigen Logikzustand zu registrieren.

- VRANGE (Eingangsspannungsbereich) – Dies ist die vom Gerät zulässige absolute Spannung, bezogen auf Masse.

Zusammenfassung

- Ein logischer Spannungspegel definiert die Spannung, die ein logisches High oder ein logisches Low darstellt.

- Viele Schaltungen stellen ein logisches High von +5 V oder +3,3 V von Masse und ein logisches Low von Masse oder 0 V dar. Diese Art von System wird als positiv oder aktiv-hoch bezeichnet.

- In der Tristate-Logik ist der Z-Zustand ein hochohmiger Zustand und wird oft als Aktivierungsleitung verwendet.

- Bei der digitalen Erzeugung behält der X-Zustand den aktuellen Logikpegel bei. Bei der digitalen Erfassung wird der Zustand „egal“ angezeigt.

- Logikfamilien bieten einen standardisierten Spannungspegel, der ein logisches High oder logisches Low darstellt.

- TTL basiert auf VCC = 5 V.

- CMOS basiert auf VCC = 3,3 V

- Differentielle Logikfamilien verwenden die Differenz zwischen zwei Werten und keine Referenz auf Masse.

- LVDS ist eine rauscharme Differenzierungsmethode mit geringem Stromverbrauch und geringer Amplitude mit VCC = 3,3 V.

- LVPECL-Schaltkreise sind eine Art ECL-Schaltkreise, die für jeden Kanal zwei Signalleitungen benötigen (VCC = 3 oder 3,3 V).